chapter 8.pdf

chapter 8.pdf

chapter 8.pdf

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

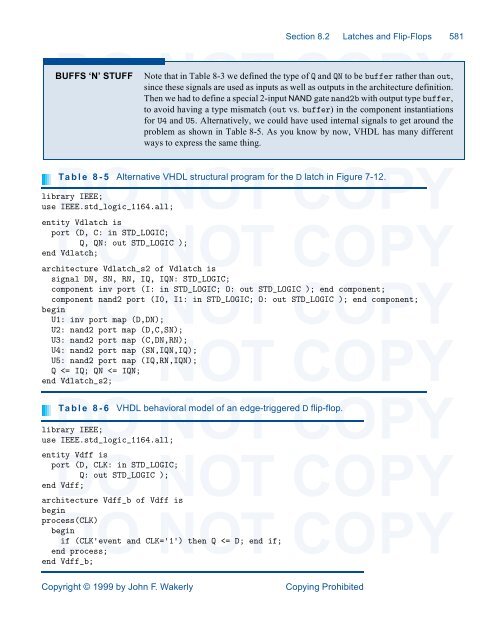

Section 8.2 Latches and Flip-Flops 581DO NOT COPYBUFFS ‘N’ STUFF Note that in Table 8-3 we defined the type of Q and QN to be buffer rather than out,since these signals are used as inputs as well as outputs in the architecture definition.Then we had to define a special 2-input NAND gate nand2b with output type buffer,DOto avoidNOThaving a type mismatch (out vs.COPYbuffer) in the component instantiationsfor U4 and U5. Alternatively, we could have used internal signals to get around theproblem as shown in Table 8-5. As you know by now, VHDL has many differentways to express the same thing.DO NOT COPYTable 8-5 Alternative VHDL structural program for the D latch in Figure 7-12.library IEEE;use IEEE.std_logic_1164.all;entityDOVdlatch isNOT COPYport (D, C: in STD_LOGIC;Q, QN: out STD_LOGIC );end Vdlatch;architecture Vdlatch_s2 of Vdlatch issignal DN, SN, RN, IQ, IQN: STD_LOGIC;DO NOT COPYcomponent inv port (I: in STD_LOGIC; O: out STD_LOGIC ); end component;component nand2 port (I0, I1: in STD_LOGIC; O: out STD_LOGIC ); end component;beginU1: inv port map (D,DN);U2: nand2 port map (D,C,SN);U3:DOnand2 port map (C,DN,RN);NOT COPYU4: nand2 port map (SN,IQN,IQ);U5: nand2 port map (IQ,RN,IQN);Q