chapter 8.pdf

chapter 8.pdf

chapter 8.pdf

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

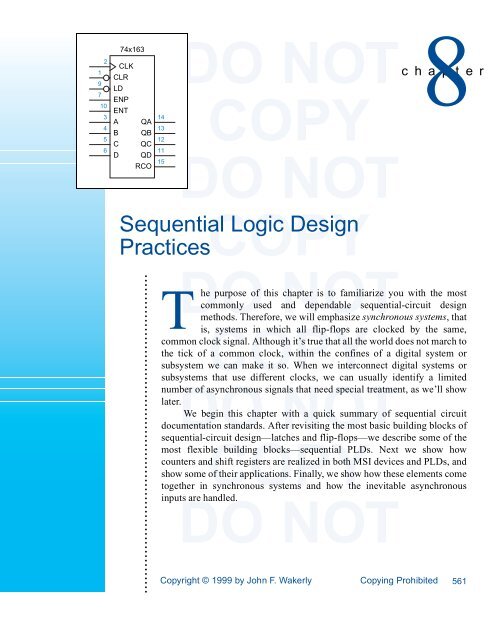

219710345674x163CLKCLRLDENPENTABCDQAQBQCQDRCO1413121115DO NOTCOPYDO NOT8c h a p t e rCOPYSequential Logic DesignPractices• • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • •TDONOTCOPYDO NOTCOPYDO NOThe purpose of this <strong>chapter</strong> is to familiarize you with the mostcommonly used and dependable sequential-circuit designmethods. Therefore, we will emphasize synchronous systems, thatis, systems in which all flip-flops are clocked by the same,common clock signal. Although it’s true that all the world does not march tothe tick of a common clock, within the confines of a digital system orsubsystem we can make it so. When we interconnect digital systems orsubsystems that use different clocks, we can usually identify a limitednumber of asynchronous signals that need special treatment, as we’ll showlater.We begin this <strong>chapter</strong> with a quick summary of sequential circuitdocumentation standards. After revisiting the most basic building blocks ofsequential-circuit design—latches and flip-flops—we describe some of themost flexible building blocks—sequential PLDs. Next we show howcounters and shift registers are realized in both MSI devices and PLDs, andshow some of their applications. Finally, we show how these elements cometogether in synchronous systems and how the inevitable asynchronousinputs are handled.Copyright © 1999 by John F. WakerlyCopying Prohibited561

562 Chapter 8 Sequential Logic Design PracticesDO8.1NOTSequential Circuit DocumentationCOPYStandards8.1.1 General RequirementsBasic documentation standards in areas like signal naming, logic symbols, andschematic layout, which we introduced in Chapter 5, apply to digital systems asDOa wholeNOTand therefore to sequentialCOPYcircuits in particular. However, there areseveral ideas to highlight for system elements that are specifically “sequential”:• State-machine layout. Within a logic diagram, a collection of flip-flops andcombinational logic that forms a state machine should be drawn togetherDO NOTin a logical format on the sameCOPYpage, so the fact that it is a state machine isobvious. (You shouldn’t have to flip pages to find the feedback path!)• Cascaded elements. In a similar way, registers, counters, and shift registersthat use multiple ICs should have the ICs grouped together in the schematicso that the cascading structure is obvious.DO NOT COPY• Flip-flops. The symbols for individual sequential-circuit elements,especially flip-flops, should rigorously follow the appropriate drawingstandards, so that the type, function, and clocking behavior of the elementsare clear.DO•NOTState-machine descriptions. StateCOPYmachines should be described by statetables, state diagrams, transition lists, or text files in a state-machinedescription language such as ABEL or VHDL.• Timing diagrams. The documentation package for sequential circuitsDO NOTshould include timing diagramsCOPYthat show the general timing assumptionsand timing behavior of the circuit.• Timing specifications. A sequential circuit should be accompanied by aspecification of the timing requirements for proper internal operation (e.g.,maximum clock frequency), as well as the requirements for any externallyDO NOTsupplied inputs (e.g., setup- andCOPYhold-time requirements with respect to thesystem clock, minimum pulse widths, etc.).8.1.2 Logic SymbolsWe introduced traditional symbols for flip-flops in Section 7.2. Flip-flops areDOalwaysNOTdrawn as rectangular-shapedCOPYsymbols, and follow the same generalguidelines as other rectangular-shaped symbols—inputs on the left, outputs onthe right, bubbles for active levels, and so on. In addition, some specific guidelinesapply to flip-flop symbols:DO•NOTA dynamic indicator is placed onCOPYedge-triggered clock inputs.• A postponed-output indicator is placed on master/slave outputs that changeat the end interval during which the clock is asserted.• Asynchronous preset and clear inputs may be shown at the top and bottomof a flip-flop symbol—preset at the top and clear at the bottom.Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.1 Sequential Circuit Documentation Standards 563DOThe logic symbols forNOTlarger-scale sequential elements,COPYsuch as thecounters and shift register described later in this <strong>chapter</strong>, are generally drawnwith all inputs, including presets and clears, on the left, and all outputs on theright. Bidirectional signals may be drawn on the left or the right, whichever isconvenient.DO NOT COPYLike individual flip-flops, larger-scale sequential elements use a dynamicindicator to indicate edge-triggered clock inputs. In “traditional” symbols, thenames of the inputs and outputs give a clue of their function, but they are sometimesambiguous. For example, two elements described later in this <strong>chapter</strong>, the74x161DOand 74x163 4-bit counters,NOThave exactly the same traditionalCOPYsymbol,even though the behavior of their CLR inputs is completely different.IEEE STANDARD IEEE standard symbols, which we show in Appendix A for all of the sequentialDOSYMBOLS elementsNOTin this <strong>chapter</strong>, have a rich set ofCOPYnotation that can provide an unambiguousdefinition of every signal’s function.8.1.3 State-Machine DescriptionsSoDOfar we have dealt with sixNOTdifferent representations of stateCOPYmachines:• Word descriptions• State tables• State diagramsDO NOT COPY• Transition lists• ABEL programs• VHDL programsYouDOmight think that havingNOTall these different ways to representCOPYstate machinesis a problem—too much for you to learn! Well, they’re not all that difficult tolearn, but there is a subtle problem here.Consider a similar problem in programming, where high-level “pseudocode”or perhaps a flowchart might be used to document how a program works.TheDOpseudo-code may expressNOTthe programmer’s intentions veryCOPYwell, but errors,misinterpretations, and typos can occur when the pseudo-code is translated intoreal code. In any creative process, inconsistencies can occur when there aremultiple representations of how things work.The same kind of inconsistencies can occur in state-machine design. A inconsistentlogicDOdesigner may documentNOTa machine’s desired behavior withCOPYa 100%-correct state-machinehand-drawn state diagram, but you can make mistakes translating the diagram representationsinto a program, and there are lots of opportunities to mess up if you have to“turning the crank” manually to translate the state diagram into a state table,transition table, excitation equations, and logic diagram.Copyright © 1999 by John F. WakerlyCopying Prohibited

564 Chapter 8 Sequential Logic Design PracticesDO NOTThe solution to this problem isCOPYsimilar to the one adopted by programmerswho write self-documenting code using a high-level language. The key is toselect a representation that is both expressive of the designer’s intentions andthat can be translated into a physical realization using an error-free, automatedDOprocess.NOT(You don’t hear many programmersCOPYscreaming “Compiler bug!” whentheir programs don’t work the first time.)The best solution (for now, at least) is to write state-machine “programs”directly in a high-level state-machine description language like ABEL orVHDL, and to avoid alternate representations, other than general, summaryDOwordNOTdescriptions. Languages like ABELCOPYand VHDL are easily readable andallow automatic conversion of the description into a PLD-, FPGA-, or ASICbasedrealization. Some CAD tools allow state machines to be specified andsynthesized using state diagrams, or even using sample timing diagrams, butthese can often lead to ambiguities and unanticipated results. Thus, we’ll useDOABEL/VHDLNOTapproach exclusively forCOPYthe rest of this book.8.1.4 Timing Diagrams and SpecificationsWe showed many examples of timing diagrams in Chapters 5 and 7. In thedesign of synchronous systems, most timing diagrams show the relationshipDObetweenNOTthe clock and various input,COPYoutput, and internal signals.Figure 8-1 shows a fairly typical timing diagram that specifies the requirementsand characteristics of input and output signals in a synchronous circuit.The first line shows the system clock and its nominal timing parameters. Theremaining lines show a range of delays for other signals.DO NOT COPYFor example, the second line shows that flip-flops change their outputs atsome time between the rising edge of CLOCK and time t ffpd afterward. Externalcircuits that sample these signals should not do so while they are changing. Thetiming diagram is drawn as if the minimum value of tDO NOT COPYffpd is zero; a completeFigure 8-1CLOCKA detailed timingtDO NOTH tdiagram showingpropagation delaysCOPYLt clkflip-flopand setup and holdoutputstimes with respect tot ffpdthe clock.combinationaloutputsDO NOTt combCOPYflip-flopinputst setupsetup-time marginCopyright © 1999 by John F. Wakerlyt holdCopying Prohibited

Section 8.1 Sequential Circuit Documentation Standards 565documentationDOpackage wouldNOTinclude a timing table indicatingCOPYthe actualminimum, typical, and maximum values of t ffpd and all other timing parameters.The third line of the timing diagram shows the additional time, t comb ,required for the flip-flop output changes to propagate through combinationallogicDOelements, such as flip-flopNOTexcitation logic. The excitationCOPYinputs of flipflopsand other clocked devices require a setup time of t setup , as shown in thefourth line. For proper circuit operation we must have t clk − t ffpd − t comb > t setup .Timing margins indicate how much “worse than worst-case” the individual timing margincomponents of a circuit can be without causing the circuit to fail. Well-designedsystemsDOhave positive, nonzeroNOTtiming margins to allow for unexpectedCOPYcircumstances(marginal components, brown-outs, engineering errors, etc.) and clockskew (Section 8.8.1).The value tDOclk − t ffpd(max) − tNOTcomb(max) − t setup is called the setup-time margin; setup-time marginif this is negative, the circuit won’t work. Note that maximum propagation delaysare used to calculate setup-time margin. Another timing marginCOPYinvolves thehold-time requirement t hold ; the sum of the minimum values of t ffpd and t combmust be greater than t hold , and the hold-time margin is t ffpd(min) + t comb(min) − t hold . hold-time marginThe timing diagram in Figure 8-1 does not show the timing differencesbetween different flip-flop inputs or combinational-logic signals, even thoughsuchDOdifferences exist in mostNOTcircuits. For example, one flip-flop’sCOPYQ outputmay be connected directly to another flip-flop’s D input, so that t comb forthat path is zero, while another’s may go the ripple-carry path of a 32-bitadder before reaching a flip-flop input. When proper synchronous designmethodology is used, these relative timings are not critical, since none of theseDO NOT COPYsignals affect the state of the circuit until a clock edge occurs. You merely haveto find the longest delay path in one clock period to determine whether thecircuit will work. However, you may have to analyze several different paths inorder to find the worst-case one.DOAnother, perhaps moreNOTcommon, type of timing diagramCOPYshows onlyfunctional behavior and is not concerned with actual delay amounts; an exampleis shown in Figure 8-2. Here, the clock is “perfect.” Whether to show signalchanges as vertical or slanted lines is strictly a matter of personal taste in this andall other timing diagrams, unless rise and fall times must be explicitly indicated.ClockDOtransitions are shownNOTas vertical lines in this and other figuresCOPYin keepingwith the idea that the clock is a “perfect” reference signal.CLOCKFigure 8-2DO NOT COPYFunctional timing of aSYNC_Lsynchronous circuit.SIG1DBUS DATA1 DATA2Copyright © 1999 by John F. WakerlyCopying Prohibited

566 Chapter 8 Sequential Logic Design PracticesDO NOT COPYNOTHING’S In reality, there’s no such thing as a perfect clock signal. One imperfection that mostPERFECT designers of high-speed digital circuits have to deal with is “clock skew.” As weshow in Section 8.8.1, a given clock edge arrives at different circuit inputs at differentDO NOTtimes because of differences in wiringCOPYdelays, loading, and other effects.Another imperfection, a bit beyond the scope of this text, is “clock jitter.” A10-MHz clock does not have a period of exactly 100 ns on every cycle—it may be100.05 ns in one cycle, and 99.95 ns in the next. This is not a big deal in such a slowcircuit, but in a 500-MHz circuit, the same 0.1 ns of jitter eats up 5% of the 2-nsDOtimingNOTbudget. And the jitter in some clockCOPYsources is even higher!The other signals in Figure 8-2 may be flip-flop outputs, combinationaloutputs, or flip-flop inputs. Shading is used to indicate “don’t-care” signalvalues; cross-hatching as in Figure 8-1 on the preceding page could be usedDO NOT COPYinstead. All of the signals are shown to change immediately after the clock edge.In reality, the outputs change sometime later, and inputs may change just barelybefore the next clock edge. However, “lining up” everything on the clock edgeallows the timing diagram to display more clearly which functions areDOperformedNOTduring each clock period.COPYSignals that are lined up with the clock aresimply understood to change sometime after the clock edge, with timing thatmeets the setup- and hold-time requirements of the circuit. Many timingdiagrams of this type appear in this <strong>chapter</strong>.Table 8-1 shows manufacturer’s timing parameters for commonly usedDOflip-flops,NOTregisters, and latches in CMOSCOPYand TTL. “Typical” values are forTable 8-1 Propagation delay in ns of selected CMOS flip-flops, registers, and latches.74HCT 74AHCT 74FCT 74LSPart Parameter Typ. Max. Typ. Max. Min. Max. Typ. Max.DO NOT COPY’74 t pd , CLK↑ to Q or Q 35 44 6.3 10 25 40t pd , PR↓ or CLR↓ to Q or Q 40 50 8.1 13 25 40tDOs , D to CLK↑ 12 15 5 20t h , D from CLK↑ 3 3 0 5t rec , CLK↑ from PR↑ orNOTCLR↑ 6 8COPY3.5t w , CLK low or high 18 23 5 25t w , PR or CLR low 16 20 5 25’174 tDOpd , CLK↑ to Q 40 50 6.3 10 21 30t pd , CLR↓ to Q 44 55 8.1 13 23 35t s , D to CLK↑NOT16 20COPY5 20t h , D from CLK↑ 5 5 0 5t rec , CLK↑ from CLR↑ 12 15 3.5 25t w , CLK low or high 20 25 5 20t w , CLR low 25 31 5 20Copyright © 1999 by John F. WakerlyCopying Prohibited

568 Chapter 8 Sequential Logic Design PracticesDOdevicesNOToperating at 25ºC but, dependingCOPYon the logic family, they could be for atypical part and nominal power-supply voltage, or they could be for a worst-casepart at worst-case supply voltage. “Maximum” values are generally valid overthe commercial operating range of voltage and temperature, except TTL values,DOwhichNOTare specified at 25ºC. Also noteCOPYthat the “maximum” values of t s , t h , t rec ,or t w are the maximum values of the minimum setup time, hold time, recoverytime, or pulse width that the specified part will exhibit.Different manufacturers may use slightly different definitions for the sametiming parameters, and they may specify different numbers for the same part. ADOgivenNOTmanufacturer may even use differentCOPYdefinitions for different families orpart numbers in the same family. Thus, all of the specifications in Table 8-1 aremerely representative; for exact numbers and their definitions, you must consultthe data sheet for the particular part and manufacturer.DO8.2NOTLatches and Flip-FlopsCOPY8.2.1 SSI Latches and Flip-FlopsSeveral different types of discrete latches and flip-flops are available as SSIparts. These devices are sometimes used in the design of state machines andDO“unstructured”NOTsequential circuits thatCOPYdon’t fall into the categories of shiftregisters, counters, and other sequential MSI functions presented later in this<strong>chapter</strong>. However, SSI latches and flip-flops have been eliminated to a largeextent in modern designs as their functions are embedded in PLDs and FPGAs.Nevertheless, a handful of these discrete building blocks still appear in manyDO NOT COPYdigital systems, so it’s important to be familiar with them.Figure 8-3 shows the pinouts for several SSI sequential devices. The only74x375latch in the figure is the 74x375, which contains four D latches, similar infunction to the “generic” D latches described in Section 7.2.4. Because of pinDOlimitations,NOTthe latches are arrangedCOPYin pairs with a common C control line foreach pair.74x74Among the devices in Figure 8-3, the most important is the 74x74, whichcontains two independent positive-edge-triggered D flip-flops with preset andclear inputs. We described the functional operation, timing, and internalDOstructureNOTof edge-triggered D flip-flopsCOPYin general, and the 74x74 in particular, inSection 7.2.5. Besides the 74x74’s use in “random” sequential circuits, fast74F74versions of the part, such as the 74F74 and 74ACT74, find application in74ACT74synchronizers for asynchronous input signals, as discussed in Section 8.9.74x109The 74x109 is a positive-edge-triggered J-K flip-flop with an active-low KDOinputNOT(named K or K_L). We discussedCOPYthe internal structure of the ’109 in74x112Section 7.2.10. Another J-K flip-flop is the 74x112, which has an active-lowclock input.Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.2 Latches and Flip-Flops 569DO NOT COPY45474x7474x10974x11274x3752 PR 52 PR 63 PR 54D QJQJQ1,2C3411 1Q3CLKCLK1D2CLK637261QQK QK QDO NOT COPY5CLRCLRCLR7 2Q2D62Q1115123,4C119 3Q3D101011103Q74x7474x10974x1121315 4QDO12 PR 9NOT14 PR 1011COPYPR 94D14D QJQJQ4Q121311CLKCLKCLK8139127QK QK QCLRCLRCLRFigure 8-3131514DO NOT COPYPinouts for SSIlatches and flip-flops.*8.2.2 Switch DebouncingA common application of simple bistables and latches is switch debouncing.We’reDOall familiar with electricalNOTswitches from experience withCOPYlights, garbagedisposals, and other appliances. Switches connected to sources of constant logic0 and 1 are often used in digital systems to supply “user inputs.” However, indigital logic applications we must consider another aspect of switch operation,the time dimension. A simple make or break operation, which occurs instantlyas farDOas we slow-moving humansNOTare concerned, actually has severalCOPYphases thatare discernible by high-speed digital logic.Figure 8-4(a) shows how a single-pole, single-throw (SPST) switch mightbe used to generate a single logic input. A pull-up resistor provides a logic-1value when the switch is opened, and the switch contact is tied to ground toprovideDOa logic-1 value whenNOTthe switch is pushed.COPYAs shown in (b), it takes a while after a push for the wiper to hit the bottomcontact. Once it hits, it doesn’t stay there for long; it bounces a few times beforefinally settling. The result is that several transitions are seen on the SW_L andDSW logic signals for each single switch push. This behavior is called contact contact bouncebounce.DOTypical switches bounceNOTfor 10–20 ms, a very long timeCOPYcompared to theswitching speeds of logic gates.Contact bounce may or may not be a problem, depending on the switchapplication. For example, some computers have configuration informationspecifiedDOby small switches,NOTcalled DIP switches because theyCOPYare the same size DIP switchas a dual in-line package (DIP). Since DIP switches are normally changed onlywhen the computer is inactive, there’s no problem. Contact bounce is a problem* Throughout this book, optional sections are marked with an asterisk.Copyright © 1999 by John F. WakerlyCopying Prohibited

570 Chapter 8 Sequential Logic Design PracticesDO NOT COPY+5V(a)push74LS04DO NOTSW_LCOPYDSWfirst contact bouncepush(b)DO NOT COPY+5VSW_LGNDFigure 8-4Switch input without1DO NOTDSWdebouncing.COPY0if a switch is being used to count or signal some event (e.g., laps in a race). Thenwe must provide a circuit (or, in microprocessor-based systems, software) todebouncedebounce the switch—to provide just one signal change or pulse for eachDOexternalNOTevent.COPY*8.2.3 The Simplest Switch DebouncerSwitch debouncing is a good application for the simplest sequential circuit, thebistable element of Section 7.1, which can be used as shown in Figure 8-5. ThisDOcircuitNOTuses a single-pole, double-throwCOPY(SPDT) switch. The switch contacts andwiper have a “break before make” behavior, so the wiper terminal is “floating”at some time halfway through the switch depression. iBefore the button is pushed, the top contact holds SW at 0 V, a valid logic0, and the top inverter produces a logic 1 onDO NOT COPYSW_L and on the bottom contact.When the button is pushed and contact is broken, feedback in the bistable holdsSW at V OL ( ≤ 0.5 V for LS-TTL), still a valid logic 0.Next, when the wiper hits the bottom contact, the circuit operates quiteunconventionally for a moment. The top inverter in the bistable is trying toDOmaintainNOTa logic 1 on the SW_L signal;COPYthe top transistor in its totem-pole outputis “on” and connecting SW_L through a small resistance to +5 V. Suddenly,the switch contact makes a metallic connection of SW_L to ground, 0.0 V. Notsurprisingly, the switch contact wins.A short time later (30 ns for the 74LS04), the forced logic 0 on SW_LDOpropagatesNOTthrough the two invertersCOPYof the bistable, so that the top inverter givesup its vain attempt to drive a 1, and instead drives a logic 0 onto SW_L. At thispoint, the top inverter output is no longer shorted to ground, and feedback in thebistable maintains the logic 0 on SW_L even if the wiper bounces off the bottomcontact, as it does. (It does not bounce far enough to touch the top contact again.)Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.2 Latches and Flip-Flops 571DO NOT COPY74LS0474LS04push SWSW_LDSW(a)DO NOTSW_LSWCOPYVDO NOTOH pushSWV OLCOPYGNDfirst contact(b)bounceV OHSW_LVDOOLFigure 8-5GNDSwitch input usingNOT COPY1a bistable forDSW0debouncingAdvantages of this circuit compared to other debouncing approaches arethatDOit has a low chip countNOT(one-third of a 74LS04), no pull-upCOPYresistors arerequired, and both polarities of the input signal (active-high and active-low)are produced. In situations where momentarily shorting gate outputs must beavoided, a similar circuit can be designed using a S-R latch and pull-up resistors,as suggested in Figure 8-6.DO NOT COPY+5 VFigure 8-6Switch input using74LS00an S-R latch forSWU_LDO NOTDSW_L debouncing.COPYpush+5 VDSWSWD_LDO NOT COPYWHERE WIMPY The circuit in Figure 8-5, while elegant, should not be used with high-speed CMOSWORKS WELL devices, like the 74ACT04, whose outputs are capable of sourcing large amounts ofDOcurrentNOTin the HIGH state. While shortingCOPYsuch outputs to ground momentarily willnot cause any damage, it will generate a noise pulse on power and ground signals thatmay trigger improper operation of the circuit elsewhere. The debouncing circuit inthe figure works well with wimpy logic families like HCT and LS-TTL.Copyright © 1999 by John F. WakerlyCopying Prohibited

572 Chapter 8 Sequential Logic Design PracticesDO*8.2.4NOTBus Holder CircuitCOPYIn Sections 3.7.3 and 5.6 we described three-state outputs and how they are tiedtogether to create three-state buses. At any time, at most one output can drive thebus; sometimes, no output is driving the bus, and the bus is “floating.” WhenDOhigh-speedNOTCMOS inputs are connectedCOPYto a bus that is left floating for a longtime (in the fastest circuits, more than a clock tick or two), bad things canhappen. In particular, noise, crosstalk, and other effects can drive the highimpedancefloating bus signals to a voltage level near the CMOS devices’ inputswitching threshold, which in turn allows excessive current to flow in the deviceDOoutputs.NOTFor this reason, it is desirableCOPYand customary to provide pull-up resistorsthat quickly pull a floating bus to a valid HIGH logic level.Pull-up resistors aren’t all goodness—they cost money and they occupyvaluable printed-circuit-board real estate. A big problem they have in very highspeedcircuits is the choice of resistance value. If the resistance is too high, whenDOa busNOTgoes from LOW to floating, theCOPYtransition from LOW to pulled-up (HIGH)will be slow due to the high RC time constant, and input levels may spend toomuch time near the switching threshold. If the pull-up resistance is too low,devices trying to pull the bus LOW will have to sink too much current.The solution to this problem is to eliminate pull-up resistors in favor of anDO NOT COPYbus holder circuit active bus holder circuit, shown in Figure 8-7. This is nothing but a bistable witha resistor R in one leg of the feedback loop. The bus holder’s INOUT signal isconnected to the three-state bus line which is to be held. When the three-stateoutput currently driving the line LOW or HIGH changes to floating, the busDOholder’sNOTright-hand inverter holds theCOPYline in its current state. When a three-stateoutput tries to change the line from LOW to HIGH or vice versa, it must source orsink a small amount of additional current through R to overcome the bus holder.This additional current flow persists only for the short time that it takes for thebistable to flip into its other stable state.DO NOTThe choice of the value of R in theCOPYbus holder is a compromise between lowoverride current (high R) and good noise immunity on the held bus line (low R).A typical example, bus holder circuits in the 3.3-V CMOS LVC family specify amaximum override current of 500 µA, implying R ≈ 3.3 / 0.0005 = 6.6KΩ.Bus holder circuits are often built into another MSI device, such as an octalDOCMOSNOTbus driver or transceiver. TheyCOPYrequire no extra pins and require verylittle chip area, so they are essentially free. And there’s no real problem in havingmultiple (n) bus holders on the same signal line, as long as the bus drivers canprovide n times the override current for a few nanoseconds during switching.Note that bus holders normally are not effective on buses that have TTL inputsDOattachedNOTto them (see Exercise 8.14).COPYFigure 8-7Bus holder circuit.RINOUTCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.2 Latches and Flip-Flops 5738.2.5DOMultibit RegistersNOTand LatchesCOPYA collection of two or more D flip-flops with a common clock input is called aregister. Registers are often used to store a collection of related bits, such as a registerbyte of data in a computer. However, a single register can also be used to storeunrelatedDObits of data or controlNOTinformation; the only real constraintCOPYis that allof the bits are stored using the same clock signal.Figure 8-8 shows the logic diagram and logic symbol for a commonly usedMSI register, the 74x175. The 74x175 contains four edge-triggered D flip-flops 74x175with a common clock and asynchronous clear inputs. It provides both activehighDOand active-low outputs atNOTthe external pins of the device.COPYThe individual flip-flops in a ’175 are negative-edge triggered, as indicatedby the inversion bubbles on their CLK inputs. However, the circuit also containsan inverter that makes the flip-flops positive-edge triggered with respect to thedevice’s external CLK input pin. The common, active-low, clear signal (CLR_L)is connectedDOto the asynchronousNOTclear inputs of all four flip-flops.COPYBoth CLK andCLR_L are buffered before fanning out to the four flip-flops, so that a devicedriving one of these inputs sees only one unit load instead of four. This isespecially important if a common clock or clear signal must drive many suchregisters.DO NOT COPY(4)(2)1DD Q1QFigure 8-8(3)CLK Q1Q_LThe 74x175 4-bit register:DO NOT(a)COPY(a) logic diagram, includingCLRpin numbers for a standard16-pin dual in-line package;(b) traditional logic symbol.(5)(7)2DD Q2Q(6)DO NOTCLK Q2Q_LCOPYCLR74x175(b) 9CLK(12)(10)13DD Q3QCLRDO NOT COPY2(11)4 1QCLK Q3Q_L1D31QCLR75 2Q2D62Q1012 3Q3D11DO(13)NOT(15)4DCOPYD Q4Q3Q15(14)13 4Q(9)CLK Q4Q_L4D14CLK4QCLR(1)CLR_LCopyright © 1999 by John F. WakerlyCopying Prohibited

574 Chapter 8 Sequential Logic Design PracticesDO NOT COPY74x174The logic symbol for the 74x174, 6-bit register is shown in Figure 8-9. The9internal structure of this device is similar to the 74x175’s, is similar, except thatCLK1it eliminates the active-low outputs and provides two more flip-flops instead.CLRMany digital systems, including computers, telecommunications devices,321D 1Q4DOandNOTstereo equipment, process informationCOPY8, 16, or 32 bits at a time; as a result,2D 2Q 56ICs that handle eight bits are very popular. One such MSI IC is the 74x374 octal3D 3Q 71110 edge-triggered D flip-flop, also known simply as an 8-bit register. (Once again,4D 4Q13“octal” means that the device has eight sections.)5D 5Q 121415As shown in Figure 8-10, the 74x374 contains eight edge-triggered D flipflops6D 6QDO NOTthat all sample their inputs andCOPYchange their outputs on the rising edge of aFigure 8-9 common CLK input. Each flip-flop output drives a three-state buffer that in turnLogic symbol for the drives an active-high output. All of the three-state buffers are enabled by a74x174 6-bit register.(1)OE_LDO NOT COPY(a)(3)1DD(2)CLK QFigure 8-101QThe 74x374 8-bit register:(a)DOlogic diagram, including pin(4)NOT2DCOPYDnumbers for a standard 20-pin(5)CLK Q2Qdual in-line package;(b) traditional logic symbol.(7)3DD(6)DO NOT COPYCLK Q3Q(8)4DD(b)(9)CLK Q4Q74x374DO NOT COPY11(13)CLK5DD1(12)OECLK Q5Q321D 1Q42D 2Q 5(14)DO73DNOT3Q 6 6DDCOPY(15)89CLK Q6Q4D 4Q135D 5Q 12(17)14156D 6Q7DD17 16(16)7D 7QCLK Q7Q18 19DO8DNOT8QCOPY(18)8DD(19)CLK Q8Q(11)CLKCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.2 Latches and Flip-Flops 575common,DOactive-lowNOT COPYOE_L (output enable) input. As in the other registers thatwe’ve studied, the control inputs (CLK and OE_L) are buffered so that theypresent only one unit load to a device that drives them.One variation of the 74x374 is the 74x373, whose symbol is shown inFigureDO8-11. The ’373 uses DNOTlatches instead of edge-triggeredCOPYflip-flops. Therefore,its outputs follow the corresponding inputs whenever C is asserted, andlatch the last input values when C is negated. Another variation is the 74x273,shown in Figure 8-12. This octal register has non-three-state outputs and noOE_L input; instead it uses pin 1 for an asynchronous clear input CLR_L.DOThe 74x377, whose symbolNOTis shown in Figure 8-13(a),COPYis an edgetriggeredregister like the ’374, but it does not have three-state outputs. Instead,pin 1 is used as an active-low clock enable input EN_L. If EN_L is asserted(LOW) at the rising edge of the clock, then the flip-flops are loaded from the datainputs; otherwise, they retain their present values, as shown logically in (b).DO NOT COPY74x37374x273Figure 8-11Figure 8-121111CLogic symbol for theCLogic symbol for the11OE74x373 8-bit latch.CLR74x273 8-bit register.3232DO1D 1QNOT COPY1D 1Q42D 2Q 542D 2Q 573D 3Q 6 73D 3Q 689894D 4Q4D 4Q135D 5Q 12135D 5Q 12141514156D 6Q6D 6QDO NOT COPY17 1617 167D 7Q7D 7Q18 1918 198D 8Q8D 8QFigure 8-13 The 74x377 8-bit register with gated clock:DO(a) logic symbol;NOT(b) logical behavior of one bit.COPY(a)(b)74x37711CLK1DOENNOT COPY(19)32D Q 8Q1D 1Q4(18)CK2D 2Q 58D73D 3Q 6894D 4Q13DO5D 5Q 12NOT COPY(1)1415 EN_L6D 6Q17 167D 7Q18 19(11)8D 8QCLKCopyright © 1999 by John F. WakerlyCopying Prohibited

576 Chapter 8 Sequential Logic Design PracticesDO NOTHigh pin-count surface-mountCOPYpackaging supports even wider registers,drivers, and transceivers. Most common are 16-bit devices, but there are alsodevices with 18 bits (for byte parity) and 32 bits. Also, the larger packages canoffer more control functions, such as clear, clock enable, multiple outputDOenables,NOTand even a choice of latchingCOPYvs. registered behavior all in one device.8.2.6 Registers and Latches in ABEL and PLDsAs we showed in Section 7.11, registers are very easy to specify in ABEL. Forexample, Table 7-33 on page 543 showed an ABEL program for an 8-bit registerDOwithNOTenable. Obviously, ABEL allowsCOPYthe functions performed at the D inputs ofregister to be customized in almost any way desired, limited only by the numberof inputs and product terms in the targeted PLD. We describe sequential PLDsin Section 8.3.With most sequential PLDs, few if any customizations can be applied to aDOregister’sNOTclock input (e.g, polarity choice)COPYor to the asynchronous inputs (e.g.,different preset conditions for different bits). However, ABEL does provideappropriate syntax to apply these customizations in devices that support them, asdescribed in Section 7.11.1.Very few PLDs have latches built in; edge-triggered registers are muchDOmoreNOTcommon, and generally more useful.COPYHowever, you can also synthesize alatch using combinational logic and feedback. For example, the excitation equationfor an S-R latch isQ∗ = S + R′⋅QDOThus,NOTyou could build an S-R latchCOPYusing one combinational output of a PLD,using the ABEL equation “Q = S # !R & Q.” Furthermore, the S and R signalsabove could be replaced with more complex logic functions of the PLD’s inputs,limited only by the availability of product terms (seven per output in a 16V8Cor 16L8) to realize the final excitation equation. The feedback loop can beDOcreatedNOTonly when Q is assigned to aCOPYbidirectional pin (in a 16V8C or 16L8, pinsIO2–IO7, not O1 or O8). Also, the output pin must be continuously outputenabled;otherwise, the feedback loop would be broken and the latch’s state lost.Probably the handiest latch to build out of a combinational PLD is a Dlatch. The basic excitation equation for a D latch isDO NOT COPYQ∗ = C ⋅ D + C′⋅QHowever, we showed in Section 7.10.1 that this equation contains a static hazard,and the corresponding circuit does not latch data reliably. To build a reliableD latch, we must include a consensus term in the excitation equation:DO NOTQ∗ = C ⋅ DCOPY+ C′⋅Q + D ⋅ QThe D input in this equation may be replaced with a more complicated expression,but the equation’s structure remains the same:Q∗ = C ⋅ expression + C′⋅Q + expression ⋅ QCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.2 Latches and Flip-Flops 577DO NOT COPYABUS ADDR1 ADDR2AVALIDDOREAD_LNOT COPYROMCS_LFigure 8-14Timing diagram for aDBUS DATA1 DATA2 microprocessor readDOfrom ROMNOTfrom a different deviceCOPYoperation.It is also possible to use a more complex expression for the C input, as weshowed in Section 7.10.1. In any case, it is very important for the consensus termto be included in the PLD realization. The compiler can work against you in thiscase,DOsince its minimizationNOTstep will find that the consensusCOPYterm is redundantand remove it.Some versions of the ABEL compiler let you prevent elimination ofconsensus terms by including a keyword “retain” in the property list of the retain propertyistype declaration for any output which is not to be minimized. In otherDO NOT COPYversions, your only choice is to turn off minimization for the entire design.Probably the most common use of a PLD-based latch is to simultaneouslydecode and latch addresses in order to select memory and I/O devices in microprocessorsystems. Figure 8-14 is a timing diagram for this function in a typicalsystem.DOThe microprocessorNOTselects a device and a location withinCOPYthe device byplacing an address on its address bus (ABUS) and asserting an “address valid”signal (AVALID). A short time later, it asserts a read signal (READ_L), and theselected device responds by placing data on the data bus (DBUS).Notice that the address does not stay valid on ABUS for the entire operation.DOThe microprocessor busNOTprotocol expects the address toCOPYbe latched usingAVALID as an enable, then decoded, as shown in Figure 8-15. The decoderselects different devices to be enabled or “chip-selected” according to the highorderbits of the address (the 12 high-order bits in this example). The low-orderbits are used to address individual locations of a selected device.DO NOT COPY32-bit latchdecoderto individual Figure 8-15device MicroprocessorQ[31:20]chip-select address latching andinputsDO NOT COPYdecoding circuit.ABUS[31:0] D[31:0]to deviceQ[19:0]addressAVALID GinputsCopyright © 1999 by John F. WakerlyCopying Prohibited

578 Chapter 8 Sequential Logic Design PracticesDO NOT COPYWHY A LATCH? The microprocessor bus protocol in Figure 8-14 raises several questions:• Why not keep the address valid on ABUS for the entire operation? In a realsystem using this protocol, the functions of ABUS and DBUS are combinedDO NOT(multiplexed) onto one three-state busCOPYto save pins and wires.• Why not use AVALID as the clock input to a positive-edge-triggered register tocapture the address? There isn’t enough setup time; in a real system, the addressmay first be valid at or slightly after the rising edge of AVALID.• OK, so why not use AVALID to clock a negative-edge-triggered register? ThisDO NOTworks, but the latched outputs are availableCOPYsooner; valid values on ABUS flowthrough a latch immediately, without waiting for the falling clock edge. Thisrelaxes the access-time requirements of memories and other devices driven bythe latched outputs.DO NOT COPYUsing a PLD, the latching and decoding functions for the high-order bitscan be combined into a single device, yielding the block diagram in Figure 8-16.Compared with Figure 8-15, the “latching decoder” saves devices and pins, andmay produce a valid chip-select output more quickly (see Exercise 8.1).DO NOTTable 8-2 is an ABEL programCOPYfor the latching decoder. Since it operateson only the high-order bits ABUS[31..20], it can decode addresses only in1-Mbyte or larger chunks (2 20 = 1M). A read-only memory (ROM) is locatedin the highest 1-Mbyte chunk, addresses 0xfff00000–0xffffffff, and isselected by ROMCS. Three 16-Mbyte banks of read/write memory (RAM) areDO NOT COPYlocated at lower addresses, starting at addresses 0x00000000, 0x00100000, and0x00200000, respectively. Notice how don’t-cares are used in the definitions ofthe RAM bank address ranges to decode a chunk larger than 1 Mbyte. Otherapproaches to these definitions are also possible (e.g., see Exercise 8.2).DO NOTThe equations in Table 8-2 forCOPYthe chip-select outputs follow the D-latchtemplate that we gave on page 576. The expressions that select a device, such as“ABUS==ROM,” each generate a single product term, and each equation generatesthree product terms. Notice the use of the “retain” property in the pin declarationsto prevent the compiler from optimizing away the consensus terms.DO NOT COPYFigure 8-16latchingto individualUsing a combined ABUS[31:20]decoderdeviceaddress latching andchip-selectdecoding circuit.GinputsDO NOT20-bit latchCOPYABUS[19:0] D[19:0]to deviceQ[19:0]addressAVALID GinputsCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.2 Latches and Flip-Flops 579DO NOT COPYmodule latchdecTable 8-2title 'Latching Microprocessor Address Decoder'ABEL programfor a latching" Inputsaddress decoder.AVALID, ABUS31..ABUS20pin;" LatchedDOand decoded outputsNOT COPYROMCS, RAMCS0, RAMCS1, RAMCS2 pin istype 'com,retain';ABUS = [ABUS31..ABUS20];ROM = ^hFFF;RAMBANK0DO= [0,0,0,0,0,0,0,0,.X.,.X.,.X.,.X.];NOT COPYRAMBANK1 = [0,0,0,0,0,0,0,1,.X.,.X.,.X.,.X.];RAMBANK2 = [0,0,0,0,0,0,1,0,.X.,.X.,.X.,.X.];equationsROMCSDO= AVALID & (ABUS==ROM)NOT# !AVALID & ROMCSCOPY# (ABUS==ROM) & ROMCS;RAMCS0 = AVALID & (ABUS==RAMBANK0) # !AVALID & RAMCS0# (ABUS==RAMBANK0) & RAMCS0;RAMCS1 = AVALID & (ABUS==RAMBANK1) # !AVALID & RAMCS1# (ABUS==RAMBANK1) & RAMCS1;RAMCS2DO= AVALID & (ABUS==RAMBANK2)NOT# !AVALID & RAMCS2COPY# (ABUS==RAMBANK2) & RAMCS2;end latchdecDO NOT COPYAfter seeing how easy it is to build S-R and D latches using combinationalPLDs, you might be tempted to go further and try to build an edge-triggered Dflip-flop. Although this is possible, it is expensive because an edge-triggeredflip-flop has four internal states and thus two feedback loops, consuming twoPLDDOoutputs. Furthermore, theNOTsetup and hold times and propagationCOPYdelays ofsuch a flip-flop would be quite poor compared to those of a discrete flip-flop inthe same technology. Finally, as we discussed in Section 7.10.6, the flow tablesof all edge-triggered flip-flops contain essential hazards, which can be maskedonly by controlling path delays, difficult in a PLD-based design.DO NOT COPY8.2.7 Registers and Latches in VHDLRegister and latch circuits can be specified using structural VHDL. For example,Table 8-3 is a structural VHDL program corresponding to the D latch circuit ofFigure 7-12 on page 443. However, writing structural programs is not really ourmotivationDOfor using VHDL;NOTour goal is to use behavioral programsCOPYto model theoperation of circuits more intuitively.Table 8-4 is a process-based behavioral architecture for the D latch thatrequires, in effect, just one line of code to describe the latch’s behavior. Note thatthe VHDL compiler “infers” a latch from this description—since the codeCopyright © 1999 by John F. WakerlyCopying Prohibited

580 Chapter 8 Sequential Logic Design PracticesDO NOT COPYTable 8-3 VHDL structural program for the D latch in Figure 7-12.library IEEE;use IEEE.std_logic_1164.all;entity Vdlatch isDOport (D, C: inNOTSTD_LOGIC;COPYQ, QN: buffer STD_LOGIC );end Vdlatch;architecture Vdlatch_s of Vdlatch issignal DN, SN, RN: STD_LOGIC;DOcomponent inv portNOT(I: in STD_LOGIC; O: outCOPYSTD_LOGIC ); end component;component nand2b port (I0, I1: in STD_LOGIC; O: buffer STD_LOGIC ); end component;beginU1: inv port map (D,DN);U2: nand2b port map (D,C,SN);DOU3: nand2b portNOTmap (C,DN,RN);COPYU4: nand2b port map (SN,QN,Q);U5: nand2b port map (Q,RN,QN);end Vdlatch_s;DO NOTTable 8-4 VHDL behavioral architectureCOPYfor a D latch.architecture Vdlatch_b of Vdlatch isbeginprocess(C, D, Q)DObeginNOT COPYif (C='1') then Q

Section 8.2 Latches and Flip-Flops 581DO NOT COPYBUFFS ‘N’ STUFF Note that in Table 8-3 we defined the type of Q and QN to be buffer rather than out,since these signals are used as inputs as well as outputs in the architecture definition.Then we had to define a special 2-input NAND gate nand2b with output type buffer,DOto avoidNOThaving a type mismatch (out vs.COPYbuffer) in the component instantiationsfor U4 and U5. Alternatively, we could have used internal signals to get around theproblem as shown in Table 8-5. As you know by now, VHDL has many differentways to express the same thing.DO NOT COPYTable 8-5 Alternative VHDL structural program for the D latch in Figure 7-12.library IEEE;use IEEE.std_logic_1164.all;entityDOVdlatch isNOT COPYport (D, C: in STD_LOGIC;Q, QN: out STD_LOGIC );end Vdlatch;architecture Vdlatch_s2 of Vdlatch issignal DN, SN, RN, IQ, IQN: STD_LOGIC;DO NOT COPYcomponent inv port (I: in STD_LOGIC; O: out STD_LOGIC ); end component;component nand2 port (I0, I1: in STD_LOGIC; O: out STD_LOGIC ); end component;beginU1: inv port map (D,DN);U2: nand2 port map (D,C,SN);U3:DOnand2 port map (C,DN,RN);NOT COPYU4: nand2 port map (SN,IQN,IQ);U5: nand2 port map (IQ,RN,IQN);Q

582 Chapter 8 Sequential Logic Design PracticesDO NOT COPYTable 8-7 VHDL model of a 74x74-like D flip-flop with preset and clear.library IEEE;use IEEE.std_logic_1164.all;DOentityNOTVdff74 isCOPYport (D, CLK, PR_L, CLR_L: in STD_LOGIC;Q, QN: out STD_LOGIC );end Vdff74;architecture Vdff74_b of Vdff74 issignal PR, CLR: STD_LOGIC;DObeginNOT COPYprocess(CLR_L, CLR, PR_L, PR, CLK)beginPR

Section 8.3 Sequential PLDs 583DOThe D-flip-flop modelNOTcan be augmented to include asynchronousCOPYinputsand a complemented output as in the 74x74 discrete flip-flop, as shown inTable 8-7. This more detailed functional model shows the non-complementarybehavior of the Q and QN outputs when preset and clear are asserted simultaneously.DOHowever, it doesNOTnot include timing behavior suchCOPYas propagationdelay and setup and hold times, which are beyond the scope of the VHDLcoverage in this book.Larger registers can of course be modeled by defining the data inputs andoutputs to be vectors, and additional functions can also be included. Forexample,DOTable 8-8 models aNOT16-bit register with three-state outputsCOPYand clockenable,output-enable, and clear inputs. An internal signal vector IQ is used tohold the flip-flop outputs, and three-state outputs are defined and enabled as inSection 5.6.4.DO NOT COPYSYNTHESIS In Table 8-8, the first elsif statement theoretically could have included all of theRESTRICTIONS conditions needed to assign D to IQ. That is, it could have read “elsif (CLK'event)and (CLK='1') and (CLKEN='1') then ...” instead of using a nested if statementDOto checkNOTCLKEN. However, it was writtenCOPYas shown for a very pragmatic reason.Only a subset of the VHDL language can be synthesized by the VHDLcompiler that was used to prepare this <strong>chapter</strong>; this is true of any VHDL compilertoday. In particular, use of the “event” attribute is limited to the form shown in theexample, and a few others, for detecting simple edge-triggered behavior. This getsmapped into edge-triggeredDO NOTD flip-flops during synthesis. The nested IF statementCOPYthat checks CLKEN in the example leads to the synthesis of multiplexer logic on theD inputs of these flip-flops.DO NOT COPY8.3 Sequential PLDs8.3.1 Bipolar Sequential PLDsThe PAL16R8, shown in Figure 8-17, is representative of the first generation of PAL16R8sequentialDOPLDs, which usedNOTbipolar (TTL) technology. ThisCOPYdevice has eightprimary inputs, eight outputs, and common clock and output-enable inputs, andfits in a 20-pin package.The PAL16R8’s AND-OR array is exactly the same as the one found in thePAL16L8 combinational PLD. However, the PAL16R8 has edge-triggered DDO NOT COPYflip-flops between the AND-OR array and its eight outputs, O1–O8. All of theflip-flops are connected to a common clock input, CLK, and change state on therising edge of the clock. Each flip-flop drives an output pin through a 3-statebuffer; the buffers have a common output-enable signal, OE_L. Notice that, likeCopyright © 1999 by John F. WakerlyCopying Prohibited

584 Chapter 8 Sequential Logic Design PracticesDOtheNOTcombinational output pins of a PAL16L8,COPYthe registered output pins of thePAL16R8 contain the complement of the signal produced by the AND-OR array.The possible inputs to the PAL16R8’s AND-OR array are eight primaryinputs (I1–I8) and the eight D flip-flop outputs. The connection from the D flipflopDO NOToutputs into the AND-OR arrayCOPYmakes it easy to design shift registers,counters, and general state machines. Unlike the PAL16L8’s combinationaloutputs, the PAL16R8’s D-flip-flop outputs are available to the AND-OR arraywhether or not the O1–O8 three-state drivers are enabled. Thus, the internal flipflopscan go to a next state that is a function of the current state even when theDOO1–O8NOToutputs are disabled.COPYMany applications require combinational as well as sequential PLDoutputs. The manufacturers of bipolar PLDs addressed this need by providing afew variants of the PAL16R8 that omitted the D flip-flops on some output pins,and instead provided input and output capability identical to that of theDOPAL16L8’sNOTbidirectional pins. For example,COPYFigure 8-18 is the logic diagram ofPAL16R6the PAL16R6, which has only six registered outputs. Two pins, IO1 and IO8, arebidirectional, serving both as inputs and as combinational outputs with separate3-state enables, just like the PAL16L8’s bidirectional pins. Thus, the possibleinputs to the PAL16R6’s AND-OR array are the eight primary inputs (I1–I8), theDOsixNOTD-flip-flop outputs, and the two bidirectionalCOPYpins (IO1, IO8).PAL16L8 PAL16R4Table 8-9 shows eight standard bipolar PLDs with differing numbers andPAL16R8types of inputs and outputs. All of the PAL16xx parts in the table use the samePAL20L8AND-OR array, where each output has eight AND gates, each with 16 variablesPAL20R4and their complements as possible inputs. The PAL20xx parts use a similarDO NOT COPYTable 8-9 Characteristics of standard bipolar PLDs.Inputs to AND arrayDO NOT COPYBidirectionalPart Package AND-gate Primary combinational Registered Combinationalnumber pins inputs inputs outputs outputs outputsPAL16L8 20 16 10 6 0 2DOPAL16R4NOT20 16 8COPY4 4 0PAL16R6 20 16 8 2 6 0PAL16R8 20 16 8 0 8 0PAL20L8 24 20 14 6 0 2DO NOT COPYPAL20R4 24 20 12 4 4 0PAL20R6 24 20 12 2 6 0PAL20R8 24 20 12 0 8 0Copyright © 1999 by John F. WakerlyCopying Prohibited

CLKI1I2I3I4I5I6I7I8Section 8.3 Sequential PLDs 585DO NOT COPY(1)0 1 2 3 4 5 6 7 8 9 1011 12131415 16171819 20212223 24252627 28293031012(19)3D Q4O15DO6NOT COPYQ7(2)8910(18)11D Q12O213DO NOT COPY14Q15(3)161718(17)19D Q20O3DO21NOT COPY22Q23(4)242526(16)27D Q28O4DO29NOT COPY30Q31(5)323334(15)35D QO5DO36NOT COPY3738Q39(6)404142(14)43D QDO44NOT COPYO64546Q47(7)484950(13)51DO NOT COPYD Q52O75354Q55(8)565758(13)DO59NOT COPYD Q60O86162Q63(9) (11)OE_LFigure 8-17 PAL16R8 logic diagram.Copyright © 1999 by John F. WakerlyCopying Prohibited

586 Chapter 8 Sequential Logic Design PracticesDO NOT COPY(1)CLK0 1 2 3 4 5 6 7 8 9 1011 12131415 16171819 20212223 24252627 282930310123(19)45DO6NOT COPY7(2)I18910(18)11D Q1213DO NOT COPY14Q15(3)I2161718(17)19D Q20DO21NOT COPY22Q23(4)I3242526(16)27D Q28DO29NOT COPY30Q31(5)I4323334(15)35D QDO36NOT COPY3738Q39(6)I5404142(14)43D QDO44NOT COPY4546Q47(7)I6484950(13)51DO NOT COPYD Q525354Q55(8)I7565758DO59NOT COPY(12)60616263(9) (11)I8Figure 8-18 PAL16R6 logic diagram.IO1O2O3O4O5O6O7IO8OE_LCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.3 Sequential PLDs 587DO NOT COPYPAL16L8PAL16R4PAL16R6PAL16R81111I1CLKCLKCLK219219219219I2 O1I1 IO1I1 IO1I1 O1318318318318I3 IO2I2 IO2I2 O2I2 O2417417417417DOI4 IO3NOTI3 O3I3COPYO3I3 O3516516516516I5 IO4I4 O4I4 O4I4 O4615615615615I6 IO5I5 O5I5 O5I5 O5714714714714I7 IO6I6 O6I6 O6I6 O6813813813813I8 IO7I7 IO7I7 O7I7 O7912912912912DOI9 O8NOTI8 IO8I8COPYIO8I8 O811111111I10OEOEOEPAL20L8PAL20R4PAL20R6PAL20R81111DOI1NOTCLKCLKCOPYCLK2222I2I1I1I13333I3I2I2I2422422422422I4 O1I3 IO1I3 IO1I3 O15 21521521521I5 IO2I4 IO2I4 O2I4 O2620620620620I6 IO3I5 O3I5 O3I5 O37DO19NOT7197COPY19719I7 IO4I6 O4I6 O4I6 O4818818818818I8 IO5I7 O5I7 O5I7 O5917917917917I9 IO6I8 O6I8 O6I8 O61016101610161016I10 IO7I9 IO7I9 O7I9 O71115111511151115I11 O8I10 IO8I10 IO8I10 O813DO14NOT14COPY14I12I11I11I1114232323I13I12I12I1223131313I14OEOEOEFigure 8-19 Logic symbols for bipolar combinational and sequential PLDs.DO NOT COPYAND-OR array with 20 variables and their complements as possible inputs. PAL20R6Figure 8-19 shows logic symbols for all of the PLDs in the table.PAL20R88.3.2DOSequential GAL DevicesNOT COPYThe GAL16V8 electrically erasable PLD was introduced in Section 5.3.3. Two“architecture-control” fuses are used to select among three basic configurationsof this device. Section 5.3.3 described the 16V8C (“complex”) configuration, 16V8Cshown in Figure 5-27 on page 307, a structure similar to that of a bipolarcombinationalDOPAL device, theNOTPAL16L8. The 16V8S (“simple”)COPYconfiguration 16V8Sprovides a slightly different combinational logic capability (see box onpage 589).The third configuration, called the 16V8R, allows a flip-flop to be provided 16V8Ron any or all of the outputs. Figure 8-20 shows the structure of the device whenCopyright © 1999 by John F. WakerlyCopying Prohibited

588 Chapter 8 Sequential Logic Design PracticesDO NOT COPY(1)CLK0 1 2 3 4 5 6 7 8 9 1011 12131415 16171819 20212223 24252627 282930310123(19)4D Q56DO NOT COPY7Q(2)I1891011(18)12D Q13DO14NOT COPY15QI2 (3)16171819(17)20D Q21DO NOT COPY2223QI3(4)24252627(16)28D QDO29NOT COPY3031Q(5)I432333435(15)36D QDO NOT COPY373839Q(6)I540414243(14)DO44NOT COPYD Q454647Q(7)I648495051(13)DO NOT COPY52D Q535455Q(8)I7565758DO59NOT COPY(12)60D Q616263QI8 (9)(11)Figure 8-20 Logic diagram for the 16V8 in the “registered” configuration.O1O2O3O4O5O6O7O8OE_LCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.3 Sequential PLDs 589DO NOT COPYRegisteredCombinationalOE CLKoutput logic macrocellOE CLKoutput logic macrocellDO NOT COPYD QQ(a)(b)Figure 8-21 Output logic macrocells for the 16V8R: (a) registered; (b) combinational.DO NOT COPYflip-flops are provided on all outputs. Notice that all of the flip-flops arecontrolled by a common clock signal on pin 1, as in the bipolar devices of thepreceding subsection. Likewise, all of the output buffers are controlled by acommon output-enable signal on pin 11.DO NOT COPYThe circuitry inside each dotted box in Figure 8-20 is called an output logic output logic macrocellmacrocell. The 16V8R is much more flexible than a PAL16R8 because eachmacrocell may be individually configured to bypass the flip-flop, that is, toproduce a combinational output. Figure 8-21 shows the two macrocell configurationsDOthat are possibleNOTin the 16V8R; (a) is registeredCOPYand (b) iscombinational. Thus, it is possible to program the device to have any set ofregistered and combinational outputs, up to eight total.The 20V8 is similar to the 16V8, but comes in a 24-pin package with four 20V8extra input-only pins. Each AND gate in the 20V8 has 20 inputs, hence the “20”in “20V8.”DO NOT COPYTHE “SIMPLE” The “simple” 16V8S configuration of the GAL16V8 is not often used, because itsDO16V8S capabilitiesNOTare mostly a subset of the 16V8C’s.COPYInstead of an AND term, the 16V8Suses one fuse per output to control whether the output buffers are enabled. That is,each output pin may be programmed either to be always enabled or to be always disabled(except pins 15 and 16, which are always enabled). All of the output pins(except 15 and 16) are available as inputs to the AND array regardless of whether theDOoutputNOTbuffer is enabled.COPYThe only advantage of a 16V8S compared to a 16V8C is that it has eight, notseven, AND terms as inputs to the OR gate on each output. The 16V8S architecturewas designed mainly for emulation of certain now-obsolete bipolar PAL devices,some of which either had eight product terms per output or had inputs on pins 12 andDO19,NOTwhich are not inputs in the 16V8CCOPYconfiguration. With appropriate programming,the 16V8S can be used as a pin-for-pin compatible replacement for thesedevices, which included the PAL10H8, PAL12H6, PAL14H4, PAL16H2,PAL10L8, PAL12L6, PAL14L4, and PAL16L2.Copyright © 1999 by John F. WakerlyCopying Prohibited

590 Chapter 8 Sequential Logic Design PracticesDO NOT COPYclock (to all macrocells)(1)I1/CLKasynchronous reset(to all macrocells)8(23)OutputDO NOT COPYlogicmacrocell10(22)Outputlogic(2)macrocellDOI2NOT COPY12(21)Outputlogic(3)macrocellI3DO NOT COPY14(20)Outputlogic(4)macrocellI416(19)DO NOT COPYOutputlogic(5)macrocellI5ProgrammableAND Array16(18)Output(132 x 44)logicDO NOT(6)COPYmacrocellI614(17)Outputlogic(7)macrocellI7DO NOT COPY12(16)Outputlogic(8)macrocellI8DO NOT COPY10(15)Outputlogic(9)macrocellI98(14)OutputDO NOT COPYlogic(10)macrocellI10Figure 8-22synchronous preset(to all macrocells)(11)(13)Logic diagram forI11the 22V10.IO1IO2IO3IO4IO5IO6IO7IO8IO9IO10I12Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.3 Sequential PLDs 591DOThe 22V10, whose basicNOTstructure is shown in Figure 8-22,COPYalso comes in a 22V1024-pin package, but is somewhat more flexible than the 20V8. The 22V10 doesnot have “architecture control” bits like the 16V8’s and 20V8’s, but it can realizeany function that is realizable with a 20V8, and more. It has more product terms,twoDOmore general-purposeNOTinputs, and better output-enableCOPYcontrol than the20V8. Key differences are summarized below:• Each output logic macrocell is configurable to have a register or not, as inthe 20V8R architecture. However, the macrocells are different from the16V8’s and 20V8’s, as shown in Figure 8-23.DO NOT COPY• A single product term controls the output buffer, regardless of whether theregistered or the combinational configuration is selected for a macrocell.• Every output has at least eight product terms available, regardless ofwhether the registered or the combinational configuration is selected. EvenDOmore product terms areNOTavailable on the inner pins, withCOPY16 available oneach of the two innermost pins. (“Innermost” is with respect to the righthandside of the Figure 8-22, which also matches the arrangement of thesepins on a 24-pin dual-inline package.)• The clock signal on pin 1 is also available as a combinational input to anyDO NOT COPYproduct term.• A single product term is available to generate a global, asynchronous resetsignal that resets all internal flip-flops to 0.• A single product term is available to generate a global, synchronous presetDOsignal that sets all internalNOTflip-flops to 1 on the rising edgeCOPYof the clock.• Like the 16V8 and 20V8, the 22V10 has programmable output polarity.However, in the registered configuration, the polarity change is made at theoutput, rather than the input, of the D flip-flop. This affects the details ofprogramming when the polarity is changed but does not affect the overallDO NOT COPYcapability of the 22V10 (i.e., whether a given function can be realized). Infact, the difference in polarity-change location is transparent when you usea PLD programming language such as ABEL.FigureDO8-23 Output logicNOTmacrocells for the 22V10: (a) registered;COPY(b) combinational.(a) CLKRegistered(b) CLKCombinationalSP AR output logic macrocellSP AR output logic macrocellDO NOT COPY8–16D Q8–16QCopyright © 1999 by John F. WakerlyCopying Prohibited

592 Chapter 8 Sequential Logic Design PracticesDO NOT COPYGAL16V8CGAL16V8RGAL20V8CGAL20V8RGAL22V1011111I1CLKI1CLKCLK/I1219 219 22223I2 O1I1 IO1I2I1I2 IO1318 318 33322I3 IO2I2 IO2I3I2I3 IO2417 417 422 422 421DOI4 IO3I3NOTIO3I4 O1COPYI3 IO1I4 IO3516 516 521 521 520I5 IO4I4 IO4I5 IO2I4 IO2I5 IO4615 615 620 620 619I6 IO5I5 IO5I6 IO3I5 IO3I6 IO5714 714 719 719 718I7 IO6I6 IO6I7 IO4I6 IO4I7 IO6813 813 818 818 817I8 IO7I7 IO7I8 IO5I7 IO5I8 IO7912 912 917 917 916I9 O8I8 IO8I9 IO6I8 IO6I9 IO811DO11NOT1016COPY1016 1015I10OEI10 IO7I9 IO7I10 IO91115 1115 11I11 O8I10 IO8I11 IO10 14131413I12I11I121423I13I122313I14OEDO NOT COPYFigure 8-24 Logic symbols for popular GAL devices.For most of the 1990s, the 16V8, 20V8, and 22V10 were the most popularDOandNOTcost-effective PLDs (but see theCOPYbox on page 595). Figure 8-24 showsgeneric logic symbols for these three devices. Most of the examples in the rest ofthis <strong>chapter</strong> can fit into the smallest of the three devices, the 16V8.DOPALS? GALS? LatticeNOTSemiconductor introduced GALCOPYdevices including the GAL16V8 andGAL20V8 in the mid-1980s. Advanced Micro Devices later followed up with a pincompatibledevice which they call the PALCE16V8 (“C” is for CMOS, “E” is forerasable). Several other manufacturers make differently numbered but compatibledevices as well. Rather than get caught up in the details of different manufacturers’DOnames,NOTin this <strong>chapter</strong> we usually referCOPYto commonly used GAL devices with theirgeneric names, 16V8, 20V8, and 22V10.DO8.3.3NOTPLD Timing SpecificationsCOPYSeveral timing parameters are specified for combinational and sequential PLDs.The most important ones are illustrated in Figure 8-25 and are explained below:t PDtDO NOTPD This parameter applies to combinational outputs. It is the propagationdelay from a primary input pin,COPYbidirectional pin, or “feedback” input tofeedback inputthe combinational output. A feedback input is an internal input of theAND-OR array that is driven by the registered output of an internalmacrocell.Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.3 Sequential PLDs 593DOt CO This parameter appliesNOTto registered outputs. It is the propagationCOPYdelay t from the rising edge of CLK to a primary output.tDOCF This parameter also applies to registered outputs. It is the propagation tNOT COPYCFdelay from the rising edge of CLK to a macrocell’s registered output thatconnects back to a feedback input. If specified, t CF is normally less thant CO . However, some manufacturers do not specify t CF , in which case youmust assume that t CF = t CO .tDOSU This parameter applies to primary, bidirectional, and feedback inputs tNOT COPYSUthat propagate to the D inputs of flip-flops. It is the setup time that theinput signal must be stable before the rising edge of CLK.t H This parameter also applies to signals that propagate to the D inputs of t Hflip-flops. It is the hold time that the input signal must be stable after therising edge of CLK.fDOmax This parameter appliesNOTto clocked operation. It is theCOPYhighest frequency f maxat which the PLD can operate reliably, and is the reciprocal of theminimum clock period. Two versions of this parameter can be derivedfrom the previous specifications, depending on whether the device isoperating with external feedback or internal feedback.DO NOT COPYExternal feedback refers to a circuit in which a registered PLD output is external feedbackconnected to the input of another registered PLD with similar timing; forproper operation, the sum of t CO for the first PLD and t SU for the secondmust not exceed the clock period.DOInternal feedback refersNOTto a circuit in which a registeredCOPYPLD output is fed internal feedbackback to a register in the same PLD; in this case, the sum of t CF and t SU mustnot exceed the clock period.Each of the PLDs that we described in previous sections is available inseveralDOdifferent speed grades.NOTThe speed grade is usually indicatedCOPYby a suffixon the part number, such as “16V8-10”; the suffix usually refers to the t PDinput orfeedbackDO NOTt SUCOPYt Hinput orCLKCLKfeedbacktDOPDtcombinationaloutputNOTCOtCOPYCF t SUregisteredregisteredoutputfeedback(a) (b)1/ f max(c)1/f max(external feedback)(internal feedback)Figure 8-25 PLD timing parameters.Copyright © 1999 by John F. WakerlyCopying Prohibited

594 Chapter 8 Sequential Logic Design PracticesDO NOT COPYTable 8-10 Timing specifications, in nanoseconds, of popular bipolar and CMOS PLDs.Part numbers Suffix tDO NOT COPYPD t t CF t SU t HPAL16L8, PAL16Rx, PAL20L8, PAL20Rx -5 5 4 – 4.5 0PAL16L8, PAL16Rx, PAL20L8, PAL20Rx -7 7.5 6.5 – 7 0PAL16L8, PAL16Rx, PAL20L8, PAL20Rx -10 10 8 – 10 0PAL16L8, PAL16Rx, PAL20L8, PAL20Rx B 15 12 – 15 0DO NOT COPYPAL16L8, PAL16Rx, PAL20L8, PAL20Rx B-2 25 15 – 25 0PAL16L8, PAL16Rx, PAL20L8, PAL20Rx A 25 15 – 25 0PALCE16V8, PALCE20V8 -5 5 4 – 3 0DO NOT COPYGAL16V8, GAL20V8 -7 7.5 5 3 5 0GAL16V8, GAL20V8 -10 10 7.5 6 7.5 0GAL16V8, GAL20V8 -15 15 10 8 12 0DO NOT COPYGAL16V8, GAL20V8 -25 25 12 10 15 0PALCE22V10 -5 5 4 – 3 0PALCE22V10 -7 7.5 4.5 – 4.5 0DO NOT COPYGAL22V10 -10 10 7 2.5 7 0GAL22V10 -15 15 8 2.5 10 0GAL22V10 -25 25 15 13 15 0DO NOT COPYspecification, in nanoseconds. Table 8-10 shows the timing of several popularbipolar and CMOS PLDs. Note that only the tDO NOT COPYPD column applies to the combinationaloutputs of a device, while the last four columns apply to registeredoutputs. All of the timing specifications are worst-case numbers over thecommercial operating range.When sequential PLDs are used in applications with critical timing, it’simportant to remember that they normally have longer setup times than discreteedge-triggered registers in the same technology, owing to the delay of the AND-DOORNOTarray on each D input. Conversely,COPYunder typical conditions, a PLD actuallyhas a negative hold-time requirement because of the delay through AND-ORarray. However, you can’t count on it having a negative hold time—the worstcasespecification is normally zero.Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.4 Counters 595NOT COPYHOW MUCH Once you understand the capabilities of different PLDs, you might ask, “Why notDOES IT COST? just always use the most capable PLD available?” For example, even if a circuit fitsin a 20-pin 16V8, why not specify the slightly larger, 24-pin 20V8 so that spareDOinputsNOTare available in case of trouble? And,COPYonce you’ve specified a 20V8, why notuse the somewhat more capable 22V10 which comes in the same 24-pin package?In the real world of product design and engineering, the constraint is cost.Otherwise, the argument of the previous paragraph could be extended ad nauseum,using CPLDs and FPGAs with even more capability (see \chapref{CPLDsFPGAs}).DO NOTLike automobiles and fine wines,COPYdigital devices such as PLDs, CPLDs, andFPGAs are not always priced proportionally to their capabilities and benefits. Inparticular, the closer a device’s capability is to the “bleeding edge,” the higher thepremium you can expect to pay. Thus, when selecting a devices to realize a design,you must evaluate many trade-offs. For example, a high-density, high-cost CPLD orFPGA may allow a design to be realized in a single device whose internal functionsDO NOT COPYare easily changed if need be. On the other hand, using two or more lower densityPLDs, CPLDs, or FPGAs may save component cost but increase board area andpower consumption, while making it harder to change the design later (since thedevice interconnections must be fixed when the board is fabricated).What this goes to show is that overall cost must always be considered alongDO NOT COPYwith design elegance and convenience to create a successful (i.e., profitable)product. And minimizing the cost of a product usually involves a plethora of common-senseeconomic and engineering considerations that are far removed from theturn-the-crank, algorithmic gate minimization methods of Chapter 4.DO NOT COPY8.4 CountersThe name counter is generally used for any clocked sequential circuit whose counterstateDOdiagram contains a singleNOTcycle, as in Figure 8-26. TheCOPYmodulus of a moduluscounter is the number of states in the cycle. A counter with m states is called amodulo-m counter or, sometimes, a divide-by-m counter. A counter with a nonpower-of-2modulus has extra states that are not used in normal operation. divide-by-m countermodulo-m counterDO NOT COPYFigure 8-26S2S1General structureS3 of a counter’s statediagram—a singlecycle.DO NOT COPYSmS4S5Copyright © 1999 by John F. WakerlyCopying Prohibited

596 Chapter 8 Sequential Logic Design PracticesDO NOT COPYQQ0CLKTQDO NOT COPYQQ1TQQQ2TDO NOT COPYQFigure 8-27A 4-bit binaryQQ3Tripple counter.QDO NOT COPYn-bit binary counter Probably the most commonly used counter type is an n-bit binary counter.Such a counter has n flip-flops and has 2 n states, which are visited in thesequence 0, 1, 2, … , 2 n −1, 0, 1, … . Each of these states is encoded as thecorresponding n-bit binary integer.DO NOT COPY8.4.1 Ripple CountersAn n-bit binary counter can be constructed with just n flip-flops and no othercomponents, for any value of n. Figure 8-27 shows such a counter for n = 4.Recall that a T flip-flop changes state (toggles) on every rising edge of its clockDO NOT COPYinput. Thus, each bit of the counter toggles if and only if the immediatelypreceding bit changes from 1 to 0. This corresponds to a normal binary countingsequence—when a particular bit changes from 1 to 0, it generates a carry to theripple counter next most significant bit. The counter is called a ripple counter because the carryDOinformationNOTripples from the less significantCOPYbits to the more significant bits, onebit at a time.8.4.2 Synchronous CountersAlthough a ripple counter requires fewer components than any other type ofDObinaryNOTcounter, it does so at a price—itCOPYis slower than any other type of binarycounter. In the worst case, when the most significant bit must change, the outputis not valid until time n ⋅ t TQ after the rising edge of CLK, where t TQ is thepropagation delay from input to output of a T flip-flop.synchronous counter A synchronous counter connects all of its flip-flop clock inputs to the sameDOcommonNOTCLK signal, so that all of theCOPYflip-flop outputs change at the same time,after only t TQ ns of delay. As shown in Figure 8-28, this requires the use ofT flip-flops with enable inputs; the output toggles on the rising edge of T if andonly if EN is asserted. Combinational logic on the EN inputs determines which,if any, flip-flops toggle on each rising edge of T.Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.4 Counters 597DO NOT COPYCNTENEN Q Q0CLKTDO NOTEN Q Q1COPYTEN Q Q2DO NOTTCOPYFigure 8-28EN Q Q3 A synchronous 4-bitbinary counter withTserial enable logic.DO NOT COPYAs shown in Figure 8-28, it is also possible to provide a master countenablesignal CNTEN. Each T flip-flop toggles if and only if CNTEN is assertedand all of the lower-order counter bits are 1. Like the binary ripple counter, asynchronousDOn-bit binary counterNOTcan be built with a fixed amountCOPYof logic perbit—in this case, a T flip-flop with enable and a 2-input AND gate.The counter structure in Figure 8-28 is sometimes called a synchronous synchronous serialserial counter because the combinational enable signals propagate serially from counterthe least significant to the most significant bits. If the clock period is too short,thereDOmay not be enough timeNOTfor a change in the counter’s LSBCOPYto propagate tothe MSB. This problem is eliminated in Figure 8-29 by driving each EN inputwith a dedicated AND gate, just a single level of logic. Called a synchronous synchronous parallelparallel counter, this is the fastest binary counter structure.counterDO NOT COPYCNTENEN Q Q0 Figure 8-29CLKA synchronous 4-bitTbinary counter withparallel enable logicDO NOTEN Q Q1COPYTEN Q Q2DO NOT COPYTEN Q Q3TCopyright © 1999 by John F. WakerlyCopying Prohibited

598 Chapter 8 Sequential Logic Design PracticesDO8.4.3NOTMSI Counters and ApplicationsCOPY74x163The most popular MSI counter is the 74x163, a synchronous 4-bit binary counterwith active-low load and clear inputs, with the traditional logic symbol shown inFigure 8-30. Its function is summarized by the state table in Table 8-11, and itsDOinternalNOTlogic diagram is shown in FigureCOPY8-31.74x163The ’163 uses D flip-flops rather than T flip-flops internally to facilitate the2CLKload and clear functions. Each D input is driven by a 2-input multiplexer consistingof an OR gate and two AND gates. The multiplexer output is 0 if the CLR_L1CLR9LDinput is asserted. Otherwise, the top AND gate passes the data input (A, B, C,7DOENPor D)NOTto the output if LD_L is asserted.COPYIf neither CLR_L nor LD_L is asserted, the10ENT314 bottom AND gate passes the output of an XNOR gate to the multiplexer output.A QA413B QB512 Table 8-11 State table for a 74x163 4-bit binary counter.C QC611DOD QDNOTInputs CurrentCOPY15State Next StateRCOCLR_L LD_L ENT ENP QD QC QB QA QD∗ QC∗ QB∗ QA∗Figure 8-30Traditional logic 0 x x x x x x x 0 0 0 0symbol forDO1NOT0 x x x xCOPYx x D C B Athe 74x163.1 1 0 x x x x x QD QC QB QA1 1 x 0 x x x x QD QC QB QA1 1 1 1 0 0 0 0 0 0 0 1DO NOT1 1 1 1 0 0COPY0 1 0 0 1 01 1 1 1 0 0 1 0 0 0 1 11 1 1 1 0 0 1 1 0 1 0 01 1 1 1 0 1 0 0 0 1 0 1DO NOT1 1 1 1 0 1COPY0 1 0 1 1 01 1 1 1 0 1 1 0 0 1 1 11 1 1 1 0 1 1 1 1 0 0 01 1 1 1 1 0 0 0 1 0 0 1DO NOT COPY1 1 1 1 1 0 0 1 1 0 1 01 1 1 1 1 0 1 0 1 0 1 11 1 1 1 1 0 1 1 1 1 0 01 1 1 1 1 1 0 0 1 1 0 1DO NOT COPY1 1 1 1 1 1 0 1 1 1 1 01 1 1 1 1 1 1 0 1 1 1 11 1 1 1 1 1 1 1 0 0 0 0Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.4 Counters 599DO NOT COPY(2)CLK(9)LD_LDO NOT COPY(1)CLR_L(3)A(14)D QQADO NOT COPYCK QDO(4)NOT COPYB(13)D QQBCK QDO NOT COPY(5)C(12)D QQCCK QDO NOT COPY(6)D(11)D QQDDO NOT COPYCK QDO NOT COPY(15)RCO(7)ENPDO(10)ENTNOT COPYFigure 8-31 Logic diagram for the 74x163 synchronous 4-bit binary counter,including pin numbers for a standard 16-pin dual in-line package.Copyright © 1999 by John F. WakerlyCopying Prohibited

600 Chapter 8 Sequential Logic Design PracticesDO NOT COPY74x1632CLOCKCLK1CLR9LD+5 V7DO NOTRENPCOPYRPU 10ENT314A QAQA413B QBQB512C QCQC Figure 8-32611DO NOTD QDCOPYQD Connections for the1574x163 to operate inRCORCOa free-running mode.U1The XNOR gates perform the counting function in the ’163. One input ofDOeachNOTXNOR is the corresponding countCOPYbit (QA, QB, QC, or QD); the other inputis 1, which complements the count bit, if and only if both enables ENP and ENTare asserted and all of the lower-order count bits are 1. The RCO (“ripple carryout”) signal indicates a carry from the most significant bit position, and is 1when all of the count bits are 1 and ENT is asserted.DO NOTEven though most MSI countersCOPYhave enable inputs, they are often used infree-running counter a free-running mode in which they are enabled continuously. Figure 8-32 showsthe connections to make a ’163 operate in this way, and Figure 8-33 shows theresulting output waveforms. Notice that starting with QA, each signal has halfthe frequency of the preceding one. Thus, a free-running ’163 can be used as aDOdivide-by-2,NOT-4, -8, or -16 counter,COPYby ignoring any unnecessary high-orderoutput bits.Note that the ’163 is fully synchronous; that is, its outputs change only onthe rising edge of CLK. Some applications need an asynchronous clear function,DO NOT COPYFigure 8-33 Clock and output waveforms for a free-running divide-by-16 counter.CLKDOQANOT COPYQBQCDO NOT COPYQDRCOCOUNT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0Copyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.4 Counters 601DO NOT COPYCLOCKQADOQBNOT COPYQCQDDO NOT COPYRCOCOUNT 0 1 2 3 4 5 6 7 8 9 0Figure 8-34 Clock and output waveforms for a free-running divide-by-10 counter.DO NOT COPYas provided by the 74x161. The ’161 has the same pinout as the ’163, but its 74x161CLR_L input is connected to the asynchronous clear inputs of its flip-flops.The 74x160 and 74x162 are more variations with the same pinouts and 74x160general functions as the ’161 and ’163, except that the counting sequence is 74x162modifiedDOto go to state 0 afterNOTstate 9. In other words, theseCOPYare modulo-10counters, sometimes called decade counters. Figure 8-34 shows the output decade counterwaveforms for a free-running ’160 or ’162. Notice that although the QD and QCoutputs have one-tenth of the CLK frequency, they do not have a 50% duty cycle,and the QC output, with one-fifth of the input frequency, does not have aconstantDOduty cycle. We’ll showNOTthe design of a divide-by-10 counterCOPYwith a 50%duty-cycle output later in this subsection.Although the ’163 is a modulo-16 counter, it can be made to count in amodulus less than 16 by using the CLR_L or LD_L input to shorten the normalcounting sequence. For example, Figure 8-35 shows one way of using the ’163as aDOmodulo-11 counter. TheNOTRCO output, which detects state 15,COPYis used to force74x163Figure 8-352CLOCKCLKUsing the 74x163 asRPU 1CLRa modulo-11 counterDO NOT COPY9LDwith the counting7ENPsequence 5, 6, …, 15,10ENT5, 6, ….314+5 VA QAQ0413B QBQ1DO NOT512COPYC QCQ2611RD QD Q315 74x04RCOCNT15 1 2U1CNT15_L U2Copyright © 1999 by John F. WakerlyCopying Prohibited

602 Chapter 8 Sequential Logic Design PracticesDO NOT COPY74x1632CLOCKCLK1CLRRPU 9LD+5 V7DO NOTRENPCOPY10ENT314A QAQ0413B QBQ1512Figure 8-36C QCQ2611UsingDOthe 74x163 asNOTDCOPYQDQ315a modulo-11 counterRCO74x001with the counting32sequence 0, 1, 2,U1…,10, 0, 1, ….CNT10_LU2DO NOT COPYthe next state to 5, so that the circuit will count from 5 to 15 and then start at 5again, for a total of 11 states per counting cycle.A different approach for modulo-11 counting with the ’163 is shown inFigure 8-36. This circuit uses a NAND gate to detect state 10 and force the nextDOstateNOTto 0. Notice that only a 2-input gateCOPYis used to detect state 10 (binary 1010).Although a 4-input gate would normally be used to detect the condition CNT10= Q3 ⋅ Q2′ ⋅ Q1 ⋅ Q0′, the 2-input gate takes advantage of the fact that no otherstate in the normal counting sequence of 0–10 has Q3 = 1 and Q1 = 1. In general,to detect state N in a binary counter that counts from 0 to N, we need to ANDDOonlyNOTthe state bits that are 1 in the binaryCOPYencoding of N.There are many other ways to make a modulo-11 counter using a ’163. Thechoice of approach—one of the preceding or a combination of them (as inExercise 8.25)—depends on the application. As another example, inSection 2.10 we promised to show you how to build a circuit that counts in theDO NOT COPY74x163Figure 8-372CLOCKCLKA 74x163 used as an1CLRexcess-3 decimal9DO NOTLDcounter.COPY7ENP10ENT+5 V314RA QAQ0RPU413B QBQ1512C QCQ2DO NOT6COPY11D QDQ315RCO74x0013U12U2S11XX_LCopyright © 1999 by John F. WakerlyCopying Prohibited

Section 8.4 Counters 603DO NOT COPYCLOCKQ0DOQ1NOT COPYQ2Q3DO NOT COPYCOUNT 3 4 5 6 7 8 9 10 11 12 3Figure 8-38 Timing waveforms for the ’163 used as an excess-3 decimal counter.excess-3 decimal code, shown in Table 2-9 on page 45. Figure 8-37 shows theconnectionsDOfor a ’163 to countNOTin the excess-3 sequence. A NANDCOPYgate detectsstate 1100 and forces 0011 to be loaded as the next state. Figure 8-38 shows theresulting timing waveforms. Notice that the Q3 output has a 50% duty cycle,which may be desirable for some applications.A binary counter with a modulus greater than 16 can be built by cascading74x163s.DOFigure 8-39 showsNOTthe general connections for suchCOPYa counter. TheCLK, CLR_L, and LD_L inputs of all the ’163s are connected in parallel, so thatall of them count or are cleared or loaded at the same time. A master countenable(CNTEN) signal is connected to the low-order ’163. The RCO4 output isasserted if and only if the low-order ’163 is in state 15 andDO NOTCNTEN is asserted;COPYRCO4 is connected to the enable inputs of the high-order ’163. Thus, both thecarry information and the master count-enable ripple from the output of oneFigure 8-39 General cascading connections for 74x163-based counters.DO NOT COPY74x16374x16322CLOCKCLKCLK11RESET_LCLRCLRDO9NOT COPY9LOAD_LLDLD77CNTENENPENP1010ENTENT314314D0A QAQ0 D4A QAQ4413413D1B QBQ1 D5B QBQ5DO5NOT12COPY512D2C QCQ2 D6C QCQ6611611D3D QD Q3 D7D QDQ715RCO415RCORCORCO8U1U2Copyright © 1999 by John F. WakerlyCopying Prohibited

604 Chapter 8 Sequential Logic Design PracticesDO4-bitNOTcounter stage to the next. LikeCOPYthe synchronous serial counter ofFigure 8-28, this scheme can be extended to build a counter with any desirednumber of bits; the maximum counting speed is limited by the propagation delayof the ripple carry signal through all of the stages (but see Exercise 8.27).DO NOTEven experienced digital designersCOPYare sometimes confused about thedifference between the ENP and ENT enable inputs of the ’163 and similarcounters, since both must be asserted for the counter to count. However, aglance at the 163’s internal logic diagram, Figure 8-31 on page 599, shows thedifference quite clearly—ENT goes to the ripple carry output as well. In manyDOapplications,NOTthis distinction is important.COPYFor example, Figure 8-40 shows an application that uses two ’163s as amodulo-193 counter that counts from 63 to 255. The MAXCNT output detectsstate 255 and stops the counter until GO_L is asserted. When GO_L is asserted,the counter is reloaded with 63 and counts up to 255 again. (Note that the valueDOof GO_LNOTis relevant only when the counterCOPYis in state 255.) To keep the counter74x163Figure 8-40+5 V2Using 74x163s as aCLKDO NOT COPY1modulo-193 counterCLRR9with the countingLD7sequence 63, 64, …,ENP10255, 63, 64, ….RPUENT314A QAQ0DO NOT COPY413B QBQ1512C QCQ2611D QDQ315RCOCLOCKDO NOT COPYU2RESET_LRCO474x001GO_L3 CNTEN74x16322CLKU1 74x001DO NOT4COPYCLR6 RELOAD_L95LD7ENPU110ENT314A QA Q4413DO NOT COPYB QB Q5512C QC Q6611D QD Q715RCO MAXCNTU3Copyright © 1999 by John F. WakerlyCopying Prohibited