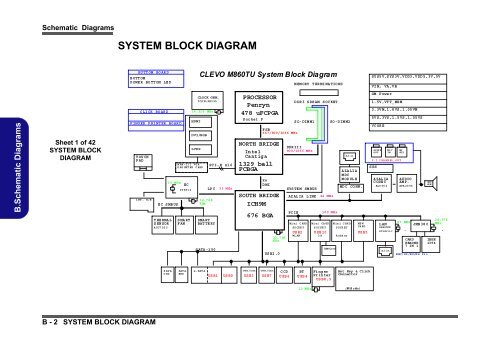

B.Schematic Diagrams Schematic Diagrams Sheet 1 of 42 SYSTEM BLOCK DIAGRAM B - 2 SYSTEM BLOCK DIAGRAM SYSTEM BLOCK DIAGRAM BU TT OM BO AR D B OTT OM P OWE R BO TT OM LE D CLICK BOARD F ING ER P RI NT ER BO AR D TOUCH PAD INT. K/B THERMAL SENSOR ASC7525 SATA ODD 10 MHz EC SMBUS IT 851 2 SMART FAN 14.318 MHz HDMI LVDS M XM -II I VG A D AU GHT ER C ARD SAT A HDD EC e- SAT A CLEVO M860TU System Block Diagram CLOCK GEN. ICS 9L PR3 95 DVI/RGB LP C 32.768 KHz SMA RT BAT TE RY S ATA -1 50 PC I- E x1 6 US B1 33 MHz US B0 PROCESSOR Penryn 478 uFCPGA Socket P NORTH BRIDGE Intel Cantiga 1329 ball FCBGA SOUTH BRIDGE ICH9M 676 BGA USB_Conn. US B3 FSB 667/800/1066 MHz X4 DMI USB_Conn. US B7 32.768 KHz US B2 .0 CCD USB6 MEMORY TERMINATIONS DDR3 SDRAM SOCKET S O- DIM M1 DDRIII 800/1066 MHz SYSTEM SMBUS AZ AL IA L INK PC IE Mi ni C ARD SO CKE T US B2 WL AN BT USB4 12 MHz 24 MHz 100 MHz Mi ni CA RD SOCKET USB10 3G SIM Card Fi ng er Pr in ter US B8 ,9 SO -D IM M2 RJ-11 AZALIA MDC MODULE MD C CO NN . Mini CARD S OCK ET R obs on (M/B s<strong>id</strong>e) NE W CA RD US B5 Hot Key & Click Connector SY S5 V,S YS 3V ,V DD3 ,V DD 5, 3V ,5V VI N, VA ,V B GM P owe r 1. 5V ,VT T_ ME M 3. 3V M,1 .8 VS ,1 .05 VM 5V S, 3VS ,1 .5 VS ,1. 05 VS VC OR E SPDIF OUT 5. 1 C HA NN EL OU T SRS LAN MIC IN A ZAL IA C ODE C ALC662 REALTEK RTL8111C RJ-45 HP OUT AU DIO AM P. APA2056 25 MHz CARD READER 7 IN 1 JMB 38 0 M MC/ SD /M S/M S Pr o INT. SPK IEEE 1394 24.576 MHz

Penryn 1/2 1.05V S 4 4 H_ADSTB#0 4 H _R EQ# [4 :0 ] 4 4 13 13 13 13 13 13 13 H_ A# [3 5:3 ] H_ADSTB#1 H_ A2 0M # H _ F ERR # H_ IG NNE # H_STPCLK# H_ INTR H _N MI H_ SMI # 3 H _TH ERM DA2 3 H _ TH ERM DC2 C PU_ GT L REF 2 3 3 R 358 R 52 56_04 H_ IER R# 54.9_1%_04 H_PR EQ# R 369 56_04 H_ PR OCH OT# R 32 6 R 32 9 5 4 .9 _1 % _ 04 H_ TMS 5 4 .9 _1 % _ 04 H_ TDI R 32 7 5 4 .9 _1 % _ 04 H_ TCK R 64 1 5 4 .9 _1 % _ 04 H_ TRST# D VT H_ A# [3 5:3 ] TD O _ M TD I _ M 3.3VS R 357 1K_04 H_ A# 3 H_ A# 4 H_ A# 5 H_ A# 6 H_ A# 7 H_ A# 8 H_ A# 9 H_A#10 H_A#11 H_A#12 H_A#13 H_A#14 H_A#15 H_A#16 H_ RE Q# 0 H_ RE Q# 1 H_ RE Q# 2 H_ RE Q# 3 H_ RE Q# 4 H_A#17 H_A#18 H_A#19 H_A#20 H_A#21 H_A#22 H_A#23 H_A#24 H_A#25 H_A#26 H_A#27 J4 L5 L4 K5 M3 N 2 J1 N 3 P5 P2 L2 P4 P1 R 1 M1 K3 H 2 K2 J3 L1 Y 2 U 5 R 3 W6 U 4 Y 5 U 1 R 4 T5 T3 W2 U22A A[3]# A[4]# A[5]# A[6]# A[7]# A[8]# A[9]# A[10]# A[11]# A[12]# A[13]# A[14]# A[15]# A[16]# ADSTB[0]# REQ [0]# REQ [1]# REQ [2]# REQ [3]# REQ [4]# A[17]# A[18]# A[19]# A[20]# A[21]# A[22]# A[23]# A[24]# A[25]# A[26]# AD S# BNR # BPR I# DEFER # D RDY # DBSY # BR0# IERR # INIT# LOC K# RESET# RS[0 ]# RS[1 ]# RS[2 ]# TRDY # HIT# H ITM # BPM[0]# BPM[1]# BPM[2]# BPM[3]# PRDY # PREQ # TC K TD I H1 E2 G5 H5 F21 E1 F1 D2 0 B3 H4 C1 F3 F4 G3 G2 G6 E4 AD4 AD3 AD1 AC4 AC2 AC1 AC5 AA6 AB3 H_A#28 H_A#29 H_A#30 H_A#31 H_A#32 H_A#33 H_A#34 H_A#35 W5 Y 4 U 2 V4 W3 AA4 AB2 AA3 V1 A6 A5 C 4 A[27]# TDO A[28]# TM S A[29]# TRST# A[30]# DBR # A[31]# A[32]# A[33]# THERMAL A[34]# A[35]# PR OCH OT# ADSTB[1]# THER MD A TH E R M D C A20M # FERR # TH ERM TR IP# IGN NE# AB5 AB6 C2 0 D2 1 A24 B25 C7 D 5 STP CLK# C 6 B4 LI N T 0 LI N T 1 A3 SMI# H_BPM _2#1 H_BPM _2#0 M4 N 5 T2 V3 B2 D 2 ADDR GROUP_0 ADDR GROUP_1 ICH Layout Note: XDP/ITP SIGNALS CONTROL RES ERV ED SOC KET G 479P H CLK BCLK[0] BCLK[1] RSVD [01]/BPM _2#[1] RSVD [02]/BPM _2#[0] RSVD [03]/THR MD A_2 RSVD [04 ]/THR MD C_ 2 RSVD [05]BPM _2#[2] RSVD [06] H_BPM _2#2 Z0206 D2 2 RSVD [07] D 3 F6 RSVD [08 ]/TDO _M RSVD [09 ]/TDI_ M ITP_ DBRS T# A22 A21 PV T H_BPM 0# H_BPM 1# H_BPM 2# H_BPM 3# H_ PR DY# H_PR EQ# H_ TCK H_ TDI H_ TDO H_ TMS H_ TRST# ITP_ DBRS T# H_ PR OCH OT# H_THER MD A1 H_ THER MD C1 If P ROC HO T# is n ot ur ed, th en it m ust b e terminated with 56-Ohm pull-up to VCCP. Within 2.0" of the CPU 3.3V Layout Note: H_ IER R# R 3 73 *1 0m i l _s h or t H_ADS# 4 H_ BNR # 4 H_ BPRI# 4 H_ DEFER # 4 H_ DR DY# 4 H_ DBSY # 4 H_ BR0 # 4 H_ INIT# 1 3 H_ L OCK# 4 H_ CPU RST# 4 H_ RS# 0 4 H_ RS# 1 4 H_ RS# 2 4 H_ TRDY # 4 H_ HIT# 4 H_ HITM# 4 PM_ THRM TRIP# 5 ,13 CL K_ CPU_ BC LK 18 CL K_ CPU_ BC LK# 1 8 H _TH ERMD A1 H _T H ERMD C1 Route H_THERMDA and H_THERMDC on same layer. 10 mil trace on 10 mil spacing. 10mils V_THR M 1 2 U2 4 VDD D+ 1000p_50V_04 3 D- 5 GND ASC7525 Near to Thermal IC 4 4 4 4 4 4 4 4 C PU_ GT L REF 1 R3 55 C4 6 3 100K_04 10u_10V_08 Near toCPU C 47 8 Layout Note: H _D ST BN# 1 H_ D STBP #1 H _D INV# 1 7 8 R3 8 0 2K _1 % _0 4 4 TH E R M 6 H _ ALER T 1 ALERT S DAT A SCLK H _D#[63:0] H _D ST BN# 0 H_ D STBP #0 H _D INV# 0 H _D#[63:0] V_THR M DVT H_ D# 0 H_ D# 1 H_ D# 2 H_ D# 3 H_ D# 4 H_ D# 5 H_ D# 6 H_ D# 7 H_ D# 8 H_ D# 9 H_ D# 1 0 H_ D# 1 1 H_ D# 1 2 H_ D# 1 3 H_ D# 1 4 H_ D# 1 5 H_ D# 1 6 H_ D# 1 7 H_ D# 1 8 H_ D# 1 9 H_ D# 2 0 H_ D# 2 1 H_ D# 2 2 H_ D# 2 3 H_ D# 2 4 H_ D# 2 5 H_ D# 2 6 H_ D# 2 7 H_ D# 2 8 H_ D# 2 9 H_ D# 3 0 H_ D# 3 1 R3 7 6 *1K_ 0 4 R3 7 5 *1K_ 0 4 C4 6 8 * 0.1 u _ X7 R_ 0 4 18 C PU_BSEL0 18 C PU_BSEL1 18 C PU_BSEL2 A D2 6 CPU _TEST1 C2 3 CPU _TEST2 D2 5 Z0210 C2 4 CPU _TEST4 AF26 Z0211 AF1 Z0212 A26 Z0213 C 3 B22 B23 C2 1 R 2 6 GT LR EF C OMP [0] MI SC U 2 6 TEST1 C OMP [1] A A1 TEST2 C OMP [2] Y 1 TEST3 C OMP [3] TEST4 E 5 TEST5 DPR STP# B 5 TEST6 D PSLP# D 2 4 TEST7 DPW R # D 6 BSEL[ 0] PW R GO OD D 7 BSEL[ 1] SLP# A E6 BSEL[ 2] P SI# Layout note: Zo=55 ohm, 0.5"max for GTLREF SOC KET G 479P R 3 88 *10K_04 R379 1K_1%_04 VD D3 N2 2 K25 P26 R2 3 L23 M2 4 L22 M2 3 P25 P23 P22 T24 R2 4 1.05VS R3 9 2 *10K_1%_04 R 38 9 *1 0m il_s h ort R 39 0 * 0 _0 4 R 391 * 10K_04 R 383 4.7K_04 R 387 4.7K_04 U2 2 B E22 F24 D[0 ]# D[1 ]# E26 G2 2 D[2 ]# F23 D[3 ]# D[4 ]# G2 5 E25 D[5 ]# D[6 ]# E23 K24 D[7 ]# D[8 ]# G2 4 J24 D[9 ]# D[1 0]# J23 H2 2 D[1 1]# F26 D[1 2]# K22 D[1 3]# H2 3 D[1 4]# D[1 5]# J26 H2 6 DSTBN[0 ]# DSTBP[0]# H2 5 DINV[ 0]# D[1 6]# D[1 7]# D[1 8]# D[1 9]# D[2 0]# D[2 1]# D[2 2]# D[2 3]# D[2 4]# D[2 5]# D[2 6]# D[2 7]# D[2 8]# L25 T25 D[2 9]# D[3 0]# N2 5 L26 D[3 1]# DSTBN[1 ]# M2 6 N2 4 DSTBP[1]# DINV[ 1]# RT2 * NTC_100K_06 ? ? ? VGA? ? thermal IC ? ? ? ? 1 2 A DM 103 1 SM bu s = 9 8h G7 81- 1 SM bu s = 4 Dh CPU _TH ERM 22 VD D3 H_D#32 H_D#33 H_D#34 H_D#35 H_D#36 H_D#37 H_D#38 H_D#39 H_D#40 H_D#41 H_D#42 H_D#43 H_D#44 H_D#45 H_D#46 H_D#47 H_D#48 H_D#49 H_D#50 H_D#51 H_D#52 H_D#53 H_D#54 H_D#55 H_D#56 H_D#57 H_D#58 H_D#59 H_D#60 H_D#61 H_D#62 H_D#63 Layout note: SMD_THERM1 3,22 SMC_THERM1 3,22 14,15, 16,19,21,27,28,29,30,31,32,34,36,37,38 3.3V 3,5,9,12,13,14,15,16,19,20,21, 22,23,24,25,26,28,30,32,33,35,36,37,38 3.3VS VD D3 13,19,22,24,29,32,33,34,37 VDD 3 PVT DATA GRP 0 DATA GRP 2 DATA GRP 1 Y 2 2 D[32]# A B24 D[33]# V 24 D[34]# V 26 D[35]# V 23 D[36]# T22 D[37]# U 2 5 D[38]# U 2 3 D[39]# Y 2 5 D[40]# W 22 D[41]# Y 2 3 D[42]# W 24 D[43]# W 25 D[44]# A A23 D[45]# A A24 D[46]# A B25 D[47]# Y 2 6 D STBN [2 ]# A A26 D ST BP[2 ]# U 2 2 DIN V[2 ]# A E24 D[48]# A D2 4 D[49]# A A21 D[50]# A B22 D[51]# A B21 D[52]# A C2 6 D[53]# A D2 0 D[54]# A E22 D[55]# A F 23 D[56]# A C2 5 D[57]# A E21 D[58]# A D2 1 D[59]# A C2 2 D[60]# A D2 3 D[61]# A F 22 D[62]# A C2 3 D[63]# A E25 D STBN [3 ]# A F 24 D ST BP[3 ]# A C2 0 DIN V[3 ]# DATA GRP 3 PM_THRM # 3,15,22 CO MP0 CO MP1 CO MP2 CO MP3 C OMP 0 C OMP 1 C OMP 2 C OMP 3 R5 6 54 . 9 _1 % _ 04 H_ D# [6 3 :0] 4 H_ DS TBN #2 4 H_ DS TBP# 2 4 H_ DI NV# 2 4 H_ D# [6 3 :0] 4 H_ DS TBN #3 4 H_ DS TBP# 3 4 H_ DI NV# 3 4 H_ DP RSTP# 5,1 3 ,3 5 H_ DP SLP# 1 3 H_ DP W R# 4 H_ PW R GD 13 H_ CP USL P# 4 PSI# 35 COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms COMP1, COMP3: 0.5" Max, Zo=55 Ohms Best es<strong>tim</strong>ate is 18 mils w<strong>id</strong>e trace for outer layers and 14 mils w<strong>id</strong>e trace if on internal layers. R5 7 R382 R 3 81 27.4_1%_04 54.9_1%_04 27.4_1%_04 3 V_THR M 3 CPU _ GTLR EF2 3,4,5,9,13,16,18,33 1.05VS Schematic Diagrams Sheet 2 of 42 Penryn 1/2 Penryn 1/2 B - 3 B.Schematic Diagrams

- Page 3 and 4:

Notebook Computer M860TU Service Ma

- Page 5 and 6:

About this Manual This manual is in

- Page 7 and 8: Instructions for Care and Operation

- Page 9 and 10: Battery Precautions • Only use ba

- Page 11 and 12: Introduction ......................

- Page 13 and 14: 1: Introduction Overview This manua

- Page 15 and 16: Feature Specification Video Adapter

- Page 17 and 18: Feature Specification Power Full Ra

- Page 19 and 20: External Locator - Front and Rear V

- Page 21 and 22: External Locator - Bottom View 1 1

- Page 23 and 24: Introduction Mainboard Overview - B

- Page 25 and 26: Introduction Mainboard Overview - B

- Page 27 and 28: 2: Disassembly Overview This chapte

- Page 29 and 30: Maintenance Precautions The followi

- Page 31 and 32: Removing the Battery 1. Turn the co

- Page 33 and 34: 6. Remove screws 11 - 12 from the h

- Page 35 and 36: Removing the System Memory (RAM) Th

- Page 37 and 38: 5. Turn the release latch 11 toward

- Page 39 and 40: Removing the VGA Card 1. Turn off t

- Page 41 and 42: Removing the Wireless LAN Module 1.

- Page 43 and 44: Removing the Inverter Board 1. Turn

- Page 45 and 46: Removing the Modem 1. Turn off the

- Page 47 and 48: Appendix A:Part Lists This appendix

- Page 49 and 50: Top without Fingerprint 切除按

- Page 51 and 52: Bottom 無鉛 無鉛 無鉛 無鉛

- Page 53 and 54: DVD-ROM Drive 無鉛 無鉛 無鉛

- Page 55 and 56: HDD 無鉛 (無鉛) Figure A - 6 HD

- Page 57: Appendix B:Schematic Diagrams This

- Page 61 and 62: Cantiga 1/6, Host 1.05V S Layout No

- Page 63 and 64: Cantiga 3/6, DDR 10 M_A_DQ[63: 0] M

- Page 65 and 66: Schematic Diagrams Cantiga 5/6, GND

- Page 67 and 68: DDR3 SO-DIMM 1 SO-DIMM 0 Layout Not

- Page 69 and 70: LCD PANEL PVT 37 EX_ENAVD D PVT: De

- Page 71 and 72: ICH9-M 2/4, PCI, USB SPI _S I i TPM

- Page 73 and 74: ICH9-M 4/4, Power R T CVC C 20mils

- Page 75 and 76: Clock Generator CLOCK GENERATOR 2 L

- Page 77 and 78: Card Reader & 1394 JMB380 IEEE1394

- Page 79 and 80: KBC-ITE IT8512 PVT VDD 3 C1 4 0.01u

- Page 81 and 82: LED, Screw Hole 22 LED _ACIN # R 63

- Page 83 and 84: Audio AMP 25 15 25 L_ H P _ O U T _

- Page 85 and 86: DVI, INV 37 EX_DAC _R 37 EX_DAC _G

- Page 87 and 88: Power GPU 5 DFGT_VID_4 5 DFGT_VID_3

- Page 89 and 90: Power 3.3VM/1.8VS/1.05VM P C 18 3 0

- Page 91 and 92: Power VDD3/VDD5/3.3V/5V EN_15V 22,3

- Page 93 and 94: Mini Card/WLAN MINI-PCIE CARD 15,19

- Page 95 and 96: Board to Board CON/TPM HOT KEY (M/B

- Page 97 and 98: Click Board TG ND GCO N1 TC9 33P_50

- Page 99 and 100: SIM Card Board MUIM_PWR MGND 2 MC5