Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

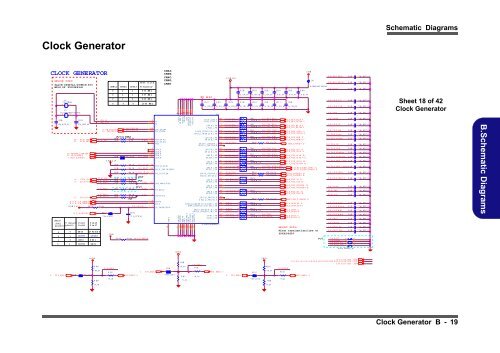

Clock Generator<br />

CLOCK GENERATOR<br />

2<br />

Layout note:<br />

PLACE CRYSTAL WITHIN 500<br />

MILS OF ICS9LPR363<br />

X4<br />

* 1 4. 3 1 8M H z<br />

2<br />

1<br />

X3<br />

14.318181M20FAQ M Hz<br />

2<br />

1<br />

C5 25<br />

27p_N PO_04<br />

38<br />

22<br />

PC LK_TPM<br />

PC LK_KBC<br />

36 R O B S O N _C LK R E Q #<br />

23 3G_CLKREQ #<br />

5 MC H_ CL KREQ #<br />

C 5 40 *1 0p _ N P O _0 4<br />

R 4 19<br />

PC LK_ICH<br />

R6 63<br />

14 PCLK_ICH<br />

C LK_ ICH 4 8 R4 21<br />

15 CL K_IC H4 8<br />

C LK_BSEL0 R422<br />

C LK_BSEL1 R 4 17<br />

C LK_BSEL2 R 4 11<br />

C LK_ ICH 1 4 R4 13<br />

15 CL K_IC H1 4<br />

10 , 1 1 , 15 IC H_SMBD AT0<br />

10 , 1 1 , 15 IC H_SMBC LK0<br />

3. 3 V M _C LK R405 10K_04<br />

15 C LK_PW R GD<br />

R4 0 2<br />

*10m il_short<br />

SE L27<br />

_S RC1 27 _Se le ct Pi n23 Pin26<br />

(p in6 6) (p in1 6) Pi n24 Pin27<br />

10 K _ 04 CLK_ITP_EN 17<br />

22 _ 04 DVT<br />

33 _ 04 PVT<br />

2.2K_04<br />

F SLA 21<br />

DVT<br />

10 K _ 04<br />

F SLB 14<br />

10 K _ 04<br />

F SLC 8<br />

33 _ 04<br />

PVT<br />

9<br />

10<br />

C LK _PW R GD _T 1<br />

C5 2 0<br />

*0 .1 u_ X 7 R_ 04<br />

PCI_ F5 /ITP_EN<br />

USB_ 4 8M Hz /FSLA<br />

FSLB/PCI2<br />

REF0 /FSL C<br />

SDATA<br />

SCLK<br />

CK_ PW RG D/PD #<br />

46<br />

SRC T6_LPR/CR #_J<br />

45<br />

SRC C6 _ LPR /CR #_ I<br />

43<br />

SRC T5_LPR 44<br />

SR CC5_LPR<br />

41<br />

SRC T4_LPR 42<br />

SR CC4_LPR<br />

38<br />

SRC T3_LPR 39<br />

SR CC3_LPR<br />

36<br />

SR CT2_ L PR/C R# _ G<br />

37<br />

S RCC 2_ L PR/C R# _ H<br />

26<br />

27MHz_NonSS/SRCT1/LCD-SST_LPR 27<br />

27MH z_SS/SR CC1/LCD -SSC_LPR<br />

23<br />

SRCT0_LPR /DOTT_96_LPR 24<br />

SR CC0_LPR/DOTC_96_LPR 32<br />

SATAT_LPR 33<br />

SATAC_LPR<br />

IC S9LPR S395BKLFT<br />

C L K_C RJ #<br />

Z1823<br />

4<br />

CLK_ PCIE_ 3G<br />

CLK_ PCIE_ 3G# 3<br />

CLK_ PCIE_ CR 4<br />

3<br />

CLK_ PCIE_ CR#<br />

Z1831<br />

Z1832 4<br />

Z1833 3<br />

Z1834 4<br />

Z1835 3<br />

CLK_ SATA 4<br />

3<br />

CLK_ SATA#<br />

R691 475_1%_04<br />

R151 475_1%_04<br />

1 RN1 0<br />

2 *4P2RX0_04 1 RN1 2<br />

2 *4P2RX0_04 R420 475_1%_04<br />

1 RN1 4<br />

2 *4P2RX0_04 1 RN1 3<br />

2 *4P2RX0_04 1 RN1 5<br />

CLK_SATA<br />

2 *4P2RX0_04 CLK_SATA#<br />

GLAN_CLKREQ # 19<br />

WLAN_CLKREQ # 36<br />

CLK_PCIE_3G 23<br />

CLK_PCIE_3G# 23<br />

CLK_PCIE_RO BSON 36<br />

CLK_PCIE_RO BSON # 36<br />

CLK_PCIE_CR 20<br />

CLK_PCIE_CR # 20<br />

NEW C ARD _C LKREQ# 21<br />

CL K_ DR EF_SS 5<br />

CL K_ DR EF_SS # 5<br />

CL K_ DR EF 5<br />

CL K_ DR EF# 5<br />

CLK_SATA 13<br />

CLK_SATA# 13<br />

Layout note:<br />

C LK_ PC IE_3 GPL L<br />

C LK_ PC IE_3 GPL L #<br />

C LK_ ICH 4 8<br />

PC LK_KBC<br />

PC LK_IC H<br />

C LK _ P C I E _G LA N<br />

C LK _ P C I E _G LA N #<br />

C LK_ PC IE_M XM<br />

C LK_ PC IE_M XM #<br />

C LK_DR EF<br />

C LK_DR EF#<br />

C LK_DR EF_SS<br />

C 5 05<br />

C 5 06<br />

C 5 41<br />

C 5 39<br />

C 5 37<br />

C 5 19<br />

C 5 15<br />

C 5 07<br />

C 5 08<br />

C 5 42<br />

C 5 43<br />

C 5 44<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

*1 0p _ N P O _0 4<br />

0<br />

0<br />

0<br />

1<br />

SR C0<br />

DO T96<br />

27 FI X/S S<br />

LC DS S<br />

3. 3 V M<br />

Place terminationclose to<br />

ICS9LPR395<br />

C LK_DR EF_SS# C 5 45 *1 0p _ N P O _0 4<br />

1<br />

0 SRC 0 SRC1<br />

R140 10K_04 MC H_ CL KREQ #<br />

PVT CL K_D REF<br />

CL K_D REF#<br />

4<br />

3<br />

5<br />

6<br />

1<br />

1 DO T96 SR C1<br />

CL K_D REF_ SS 2<br />

CLK_D REF_SS# 1<br />

7<br />

8<br />

CP U_BSEL0<br />

C5 2 2<br />

27p_NPO_04 1.05VS<br />

R 40 0<br />

*56_04<br />

R 1 33 *1 0m i l _s h or t<br />

R 39 9<br />

1K_04<br />

XT A L _I N<br />

XT A L _O U T<br />

BSE L2 BS EL1 BS EL 0<br />

Ho st Cl oc k<br />

Fr eq uen cy<br />

0 0 1 533 MHz<br />

0 1 1 667 MHz<br />

0 1 0 800 MHz<br />

0 0 0 10 66 MH z<br />

15 PM _STPC PU#<br />

15 PM_STPP CI#<br />

PC LK_KBC<br />

3.3VM _C LK<br />

C LK_BSEL0<br />

R 13 2<br />

1K_04<br />

PM _STPCP U#<br />

PM _STPPC I#<br />

PVT: for ETPM<br />

R 6 92 *3 3_ 0 4<br />

R4 16 22 _ 04<br />

R 1 44 *1 0m i l _s h or t<br />

5<br />

4<br />

X1<br />

X2<br />

65<br />

40 CPU _STO P#<br />

PCI_STOP#<br />

11<br />

Z 18 0 2 13<br />

15<br />

PCI0 /CR # _C<br />

PCI1 /CR # _D<br />

PCI3<br />

2<br />

CR #_A 7<br />

19 CR #_B 31 CR #_E CR #_F CL K_ CRM # 60<br />

CR #_M 2<br />

C PU_BSEL1<br />

CR# A:<br />

CR# B:<br />

CR# C:<br />

CR# D:<br />

CR# E:<br />

R 4 18 10 K _ 04 CL K_ 27 _ SEL 16<br />

PCI4 /2 7_ Se lec t<br />

R 1 45 10 K _ 04 CLK_SEL27 66<br />

SEL27_SRC 1/R ESET#<br />

M CH _BSEL0 5<br />

SGN D<br />

73<br />

R1 34<br />

* 10 m il_ s ho rt<br />

34<br />

6<br />

12<br />

20<br />

25<br />

29<br />

54<br />

72<br />

VDD A<br />

VD DRE F<br />

VDD PCI<br />

VD D48<br />

VDD<br />

VDD SRC 0<br />

VD DSR C1<br />

VDD CPU<br />

GN DREF<br />

G NDPC I<br />

GND 4 8<br />

GN D<br />

GND SRC 0<br />

GN DA<br />

G ND SRC1<br />

GN DSRC 2<br />

G NDC PU<br />

3<br />

18<br />

22<br />

28<br />

30<br />

35<br />

47<br />

57<br />

69<br />

1. 0 5 V S<br />

R3 98<br />

1K _ 0 4<br />

R 39 7<br />

*0 _ 0 4<br />

C2 4 1<br />

C 21 5<br />

C2 2 9<br />

C 2 42<br />

C2 4 3<br />

C2 44<br />

C2 1 1<br />

C5 49<br />

0.1u_10V_04 0.1u_10V_04 0.1u_10V_04 0.1u_10V_04 0.1u_10V_04 0.1u_10V_04 0.1u_10V_04 0.1u_10V_04<br />

U2 6<br />

CP UT1_ L PR_ F<br />

C PUC 1_ L PR_ F<br />

CPU T0_LPR<br />

C PUC0_LPR<br />

C PUT2_ITP/SR CT13_LPR<br />

CPU C2 _ ITP/SR CC 13_ L PR<br />

C LK_BSEL1<br />

R1 35<br />

1K _ 0 4<br />

40 m il<br />

SR CT12_LPR<br />

SR CC 12_LPR<br />

SR CT11_LPR/CR #_L<br />

SR CC11_LPR /CR #_K<br />

SR CT10_LPR<br />

SR CC 10_LPR<br />

SRC T9_LPR<br />

SR CC9_LPR<br />

SRC T8_LPR<br />

SR CC8_LPR<br />

SRC T7_LPR<br />

SR CC7_LPR<br />

68<br />

67<br />

71<br />

70<br />

64<br />

63<br />

62<br />

61<br />

59<br />

58<br />

56<br />

55<br />

52<br />

53<br />

50<br />

51<br />

48<br />

49<br />

MCH _BSEL1 5<br />

3.3VM_CLK<br />

CLK_MCH_BCLK 1<br />

2 CLK_MCH_BCLK#<br />

4 RN3<br />

CL K_ MC H_ BCL K<br />

3 *4P2RX0_04 CL K_ MC H_ BCL K#<br />

CLK_CPU_BCLK 1 4 RN2<br />

CL K_ CPU _ BCL K<br />

CLK_CPU_BCLK# 2 3 *4P2RX0_04 CL K_ CPU _ BCL K#<br />

1 CLK_PCIE_3GPLL<br />

CLK_PCIE_3GPLL# 2<br />

4 RN4<br />

CLK_PCIE _3GPLL<br />

3 *4P2RX0_04 CLK_PCIE _3GPLL#<br />

CLK_PCIE_MXM 1 4 RN5<br />

CLK_PCIE _M XM<br />

CLK_PCIE_MXM# 2 3 *4P2RX0_04 CLK_PCIE _M XM #<br />

C L K_C RL #<br />

CLK_PCIE_ICH<br />

CLK_PCIE_ICH#<br />

1<br />

2<br />

4 RN6<br />

3 *4P2RX0_04 4<br />

CLK_PCIE_GLAN<br />

CLK_PCIE_GLAN# 3<br />

1 RN7<br />

2 *4P2RX0_04 CLK_PCIE_WLAN 4<br />

CLK_PCIE_WLAN# 3<br />

CLK_PCIE_NEW_CARD 4<br />

3<br />

CLK_PCIE_NEW_CARD#<br />

2<br />

CPU_ BSEL 2<br />

R690 475_1%_04<br />

R1 3 7<br />

*1 0m i l_ s h ort<br />

CLK_PCIE _IC H<br />

CLK_PCIE _IC H#<br />

CLK_PCIE _G LAN<br />

CLK_PCIE _G LAN #<br />

R3 9 6<br />

*1 K _ 0 4<br />

R3 95<br />

1K_04<br />

CL K_BSE L2<br />

R1 3 6<br />

1K_04<br />

CL K_ MC H_ BCL K 4<br />

CL K_ MC H_ BCL K# 4<br />

CL K_ CPU _BC L K 2<br />

CL K_ CPU _BC L K# 2<br />

CLK_PCIE_3GPLL 5<br />

CLK_PCIE_3GPLL# 5<br />

CLK_PCIE_MXM 37<br />

CLK_PCIE_MXM # 37<br />

MXM_CLKREQ # 37<br />

CLK_PCIE_ICH 14<br />

CLK_PCIE_ICH # 14<br />

CLK_PCIE_GLAN 19<br />

CLK_PCIE_GLAN # 19<br />

3.3VM<br />

1 RN8<br />

2 *4P2RX0_04 CLK_PCIE_W LAN 36<br />

CLK_PCIE_W LAN# 36<br />

1 RN9<br />

CLK_PCIE _N EW _C ARD<br />

2 *4P2RX0_04 CLK_PCIE _N EW _C ARD #<br />

C LK_PC IE_N EW _CARD 21<br />

C LK_PC IE_N EW _CARD # 21<br />

1.05VS<br />

L47<br />

C LK_ MC H_ BCL K<br />

C LK_ MC H_ BCL K#<br />

H CB2012KF-500T40<br />

C LK_ ICH 1 4<br />

C 5 50<br />

C5 5 3<br />

C5 52<br />

C2 2 0<br />

C5 51<br />

C 54 8<br />

10u_10V_08 10 u _1 0 V _ 08 10u_10V_08 1u _ 6 . 3V _ 0 4 1u_6.3V_04 1u _ 6 . 3V _ 0 4<br />

C LK_ PC IE_IC H<br />

C LK_ PC IE_IC H#<br />

C LK_ SAT A<br />

C LK_ SAT A#<br />

C LK_ PC IE_3 G<br />

C LK_ PC IE_3 G#<br />

CLK_PCIE_WLAN#<br />

CL K_ PCIE_ CR #<br />

CLK_PCIE_RO BSON<br />

CLK_PCIE_RO BSON #<br />

C 5 03 *1 0p _ N P O _0 4<br />

C 5 09 *1 0p _ N P O _0 4<br />

C 5 46 *1 0p _ N P O _0 4<br />

C 5 47 *1 0p _ N P O _0 4<br />

C 5 29 *1 0p _ N P O _0 4<br />

C 5 23 *1 0p _ N P O _0 4<br />

C 5 21 *1 0p _ N P O _0 4<br />

C 5 38 *1 0p _ N P O _0 4<br />

C 5 35 *1 0p _ N P O _0 4<br />

CLK_PCIE_NEW _C ARD C 5 26 *1 0p _ N P O _0 4<br />

CLK_PCIE_NEW _C ARD# C 5 24 *1 0p _ N P O _0 4<br />

R N24 8P4RX0_04<br />

C 5 04 *1 0p _ N P O _0 4<br />

C 5 32 *1 0p _ N P O _0 4<br />

C 5 10 *1 0p _ N P O _0 4<br />

C 5 30 *1 0p _ N P O _0 4<br />

C 5 33 *1 0p _ N P O _0 4<br />

10,11,14,15,16,32 3.3VM<br />

2,3,5,9,12,13,14,15,16,19,20,21,22,23,24,25,26,28,30,32,33,35,36,37,38 3.3VS<br />

2,3,4,5,9,13,16,331.05VS<br />

MC H_BSEL2 5<br />

CLK_PCIE_WLAN<br />

CL K_ PCIE_ CR<br />

Schematic Diagrams<br />

Sheet 18 of 42<br />

Clock Generator<br />

Clock Generator B - 19<br />

B.Schematic Diagrams