Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

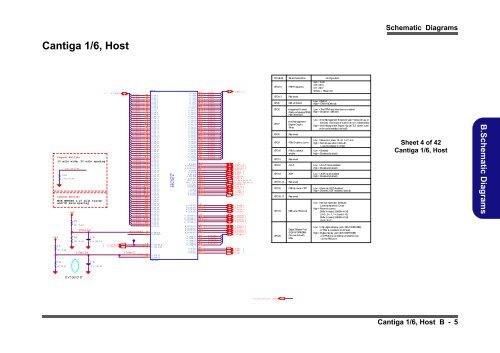

Cantiga 1/6, Host<br />

1.05V S<br />

Layout Notice:<br />

10 mils w<strong>id</strong>e, 20 mils spacing<br />

R 10 4<br />

24. 9_1%_04<br />

Layout Notice:<br />

MCH_HSWING a 10 mils traces<br />

and 20 mils spacing<br />

R 9 1<br />

1K_1%_04<br />

R 9 0<br />

2K_1%_04<br />

M CH _ HR CO MP<br />

1.05VS<br />

R9 6<br />

221_1%_04<br />

R9 5<br />

100_1%_04<br />

10mils<br />

D VT: De l C1 27<br />

10mils<br />

C 1 36<br />

0.1u_10V_04<br />

C 1 28<br />

* 0.1u_10V_04<br />

2<br />

2<br />

2<br />

H_D #[63:0]<br />

H_ C PUR ST#<br />

H _ CPU SL P#<br />

H _D # 0<br />

H _D # 1<br />

H _D # 2<br />

H _D # 3<br />

H _D # 4<br />

H _D # 5<br />

H _D # 6<br />

H _D # 7<br />

H _D # 8<br />

F2<br />

G8<br />

F8<br />

E6<br />

G2<br />

H6<br />

H2<br />

F6<br />

D4<br />

H_D#_0<br />

H_D#_1<br />

H_D#_2<br />

H_D#_3<br />

H_D#_4<br />

H_D#_5<br />

H_D#_6<br />

H_D#_7<br />

H _D # 9<br />

H _D # 1 0<br />

H _D # 1 1<br />

H _D # 1 2<br />

H _D # 1 3<br />

H _D # 1 4<br />

H _D # 1 5<br />

H _D # 1 6<br />

H _D # 1 7<br />

H _D # 1 8<br />

H _D # 1 9<br />

H _D # 2 0<br />

H _D # 2 1<br />

H _D # 2 2<br />

H3<br />

M9<br />

M11<br />

J1<br />

J2<br />

N 12<br />

J6<br />

P2<br />

L2<br />

R2<br />

N9<br />

L6<br />

M5<br />

J3<br />

H_D#_8<br />

H_D#_9<br />

H_D#_10<br />

H_D#_11<br />

H_D#_12<br />

H_D#_13<br />

H_D#_14<br />

H_D#_15<br />

H_D#_16<br />

H_D#_17<br />

H_D#_18<br />

H_D#_19<br />

H_D#_20<br />

H_D#_21<br />

H _D # 2 3<br />

H _D # 2 4<br />

H _D # 2 5<br />

H _D # 2 6<br />

H _D # 2 7<br />

H _D # 2 8<br />

H _D # 2 9<br />

N2<br />

R1<br />

N5<br />

N6<br />

P13<br />

N8<br />

L7<br />

H_D#_22<br />

H_D#_23<br />

H_D#_24<br />

H_D#_25<br />

H_D#_26<br />

H_D#_27<br />

H_D#_28<br />

H _D # 3 0<br />

H _D # 3 1<br />

H _D # 3 2<br />

H _D # 3 3<br />

H _D # 3 4<br />

H _D # 3 5<br />

H _D # 3 6<br />

N 10<br />

M3<br />

Y3<br />

AD 14<br />

Y6<br />

Y 10<br />

Y 12<br />

H_D#_29<br />

H_D#_30<br />

H_D#_31<br />

H_D#_32<br />

H_D#_33<br />

H_D#_34<br />

H_D#_35<br />

H _D # 3 7<br />

H _D # 3 8<br />

H _D # 3 9<br />

H _D # 4 0<br />

H _D # 4 1<br />

H _D # 4 2<br />

H _D # 4 3<br />

Y 14<br />

Y7<br />

W2<br />

AA8<br />

Y9<br />

A A13<br />

AA9<br />

H_D#_36<br />

H_D#_37<br />

H_D#_38<br />

H_D#_39<br />

H_D#_40<br />

H_D#_41<br />

H_D#_42<br />

H _D # 4 4<br />

H _D # 4 5<br />

H _D # 4 6<br />

H _D # 4 7<br />

H _D # 4 8<br />

H _D # 4 9<br />

H _D # 5 0<br />

A A11<br />

AD 11<br />

AD 10<br />

AD 13<br />

A E12<br />

AE9<br />

AA2<br />

H_D#_43<br />

H_D#_44<br />

H_D#_45<br />

H_D#_46<br />

H_D#_47<br />

H_D#_48<br />

H_D#_49<br />

H _D # 5 1<br />

H _D # 5 2<br />

H _D # 5 3<br />

H _D # 5 4<br />

H _D # 5 5<br />

H _D # 5 6<br />

H _D # 5 7<br />

AD8<br />

AA3<br />

AD3<br />

AD7<br />

A E14<br />

AF3<br />

AC1<br />

H_D#_50<br />

H_D#_51<br />

H_D#_52<br />

H_D#_53<br />

H_D#_54<br />

H_D#_55<br />

H_D#_56<br />

H _D # 5 8<br />

H _D # 5 9<br />

H _D # 6 0<br />

H _D # 6 1<br />

H _D # 6 2<br />

H _D # 6 3<br />

AE3<br />

AC3<br />

A E11<br />

AE8<br />

AG2<br />

AD6<br />

H_D#_57<br />

H_D#_58<br />

H_D#_59<br />

H_D#_60<br />

H_D#_61<br />

H_D#_62<br />

H_D#_63<br />

Z0401<br />

A11<br />

B11<br />

U2 5 A<br />

M CH _H SW IN G C5<br />

M CH _H RC OM P E3 H_ SW IN G<br />

H_ RC OM P<br />

100mil<br />

C 12<br />

H_ CPU RS T#<br />

E11<br />

H_ CPU SL P#<br />

H_AVR EF<br />

H_ DVR EF<br />

CAN TIGA<br />

HOST<br />

A14<br />

H _ A#_ 3<br />

C 1 5<br />

H _ A#_ 4<br />

H _ A#_ 5<br />

H _ A#_ 6<br />

H _ A#_ 7<br />

H _ A#_ 8<br />

H _ A#_ 9<br />

H _ A# _1 0<br />

H _ A# _1 1<br />

F16<br />

H 1 3<br />

C 1 8<br />

M16<br />

J13<br />

P16<br />

R 1 6<br />

N 1 7<br />

H _ A# _1 2<br />

H _ A# _1 3<br />

H _ A# _1 4<br />

H _ A# _1 5<br />

H _ A# _1 6<br />

H _ A# _1 7<br />

H _ A# _1 8<br />

H _ A# _1 9<br />

H _ A# _2 0<br />

H _ A# _2 1<br />

H _ A# _2 2<br />

H _ A# _2 3<br />

H _ A# _2 4<br />

H _ A# _2 5<br />

M13<br />

E17<br />

P17<br />

F17<br />

G 2 0<br />

B19<br />

J16<br />

E20<br />

H 1 6<br />

J20<br />

L17<br />

A17<br />

B17<br />

L16<br />

H _ A# _2 6<br />

H _ A# _2 7<br />

H _ A# _2 8<br />

H _ A# _2 9<br />

H _ A# _3 0<br />

H _ A# _3 1<br />

H _ A# _3 2<br />

C 2 1<br />

J17<br />

H 2 0<br />

B18<br />

K17<br />

B20<br />

F21<br />

H _ A# _3 3<br />

H _ A# _3 4<br />

H _ A# _3 5<br />

K21<br />

L20<br />

H 1 2<br />

H _A DS#<br />

H_AD STB#_0<br />

H_AD STB#_1<br />

B16<br />

G 1 7<br />

A9<br />

H_ BN R#<br />

H _B PRI#<br />

H_BR EQ#<br />

H_ DEF ER#<br />

H_ DB SY#<br />

HPLL_CLK<br />

HPLL_CLK#<br />

F11<br />

G 1 2<br />

E9<br />

B10<br />

AH 7<br />

AH 6<br />

J11<br />

H_ DP W R#<br />

H_ D RD Y#<br />

H_ HIT#<br />

H _H IT M#<br />

H _L O CK#<br />

H_ TRD Y#<br />

F9<br />

H 9<br />

E12<br />

H 1 1<br />

C 9<br />

H _D IN V#_ 0<br />

H _D IN V#_ 1<br />

H _D IN V#_ 2<br />

H _D IN V#_ 3<br />

H _ DST BN #_ 0<br />

H _ DST BN #_ 1<br />

H _ DST BN #_ 2<br />

H _ DST BN #_ 3<br />

H_ DS TB P#_ 0<br />

H_ DS TB P#_ 1<br />

H_ DS TB P#_ 2<br />

H_ DS TB P#_ 3<br />

J8<br />

L3<br />

Y 1 3<br />

Y 1<br />

L10<br />

M7<br />

AA 5<br />

AE 6<br />

L9<br />

M8<br />

AA 6<br />

AE 5<br />

B15<br />

H _ REQ #_ 0<br />

H _ REQ #_ 1<br />

H _ REQ #_ 2<br />

K13<br />

F13<br />

B13<br />

H _ REQ #_ 3<br />

H _ REQ #_ 4<br />

B14<br />

H_ R S#_ 0<br />

H_ R S#_ 1<br />

H_ R S#_ 2<br />

B6<br />

F12<br />

C 8<br />

H_ A# 3<br />

H_ A# 4<br />

H_ A# 5<br />

H_ A# 6<br />

H_ A# 7<br />

H_ A# 8<br />

H_ A# 9<br />

H_A#10<br />

H_A#11<br />

H_A#12<br />

H_A#13<br />

H_A#14<br />

H_A#15<br />

H_A#16<br />

H_A#17<br />

H_A#18<br />

H_A#19<br />

H_A#20<br />

H_A#21<br />

H_A#22<br />

H_A#23<br />

H_A#24<br />

H_A#25<br />

H_A#26<br />

H_A#27<br />

H_A#28<br />

H_A#29<br />

H_A#30<br />

H_A#31<br />

H_A#32<br />

H_A#33<br />

H_A#34<br />

H_A#35<br />

H_ RE Q# 0<br />

H_ RE Q# 1<br />

H_ RE Q# 2<br />

H_ RE Q# 3<br />

H_ RE Q# 4<br />

H _A #[35:3] 2<br />

H _A DS# 2<br />

H _A DSTB#0 2<br />

H _A DSTB#1 2<br />

H _B NR # 2<br />

H _B PRI# 2<br />

H _B R0 # 2<br />

H _D EF ER # 2<br />

H _D BSY # 2<br />

CL K_ MC H_ BC LK 18<br />

C LK _M CH _ BCL K# 1 8<br />

H _D PW R # 2<br />

H _D RD Y# 2<br />

H _H IT # 2<br />

H _H IT M# 2<br />

H _L O CK# 2<br />

H _T R DY # 2<br />

H _D IN V#0 2<br />

H _D IN V#1 2<br />

H _D IN V#2 2<br />

H _D IN V#3 2<br />

H _D ST BN #0 2<br />

H _D ST BN #1 2<br />

H _D ST BN #2 2<br />

H _D ST BN #3 2<br />

H _D STBP#0 2<br />

H _D STBP#1 2<br />

H _D STBP#2 2<br />

H _D STBP#3 2<br />

H _R EQ #[4 :0 ] 2<br />

H _R S# 0<br />

H _R S# 1<br />

2<br />

2<br />

H _R S# 2 2<br />

Pin Name<br />

CFG2: 0<br />

CFG4: 3<br />

CFG5<br />

CFG6<br />

CFG7<br />

CFG8<br />

CFG9<br />

CFG10<br />

CFG11<br />

CFG12<br />

CFG13<br />

CFG15 :14<br />

FSB Fr eguency<br />

Res erved<br />

DMI x2 Select<br />

Res erved<br />

PCIe Gr aphics Lan e<br />

ALLZ<br />

Res erved<br />

DMI Lane Rever sal<br />

Digital Display Port<br />

(SDVO/ DP/iHDMI)<br />

Con curr ent w ith<br />

PCIe<br />

Co nfigur ation<br />

Low = DMI x2<br />

High = DMI x4 (Defa ult)<br />

Low = The ITPM Host Inter face is e nabled<br />

High = Disabled ( Def <strong>au</strong>lt)<br />

Low = Reve rse L anes, 15 ->0, 1 4->1 e tc<br />

High = Normal ope ration ( defa ult ):<br />

L ane Numbered in Or der<br />

Low = ALLZ mod e enabled<br />

High = Disabled (d ef<strong>au</strong>lt)<br />

Low = XOR mo de enab led<br />

High = Disabled (d ef<strong>au</strong>lt)<br />

CFG16 FSB Dy namic ODT Low = Dyna mic ODT disabled<br />

High = Dynamic ODT enabled ( defa ult)<br />

CFG18 :17 Res erved<br />

CFG19<br />

CFG20<br />

2,3,5,9,13, 16,18,33 1.05VS<br />

Str ap Description<br />

In tegra ted Tr usted<br />

Platfor m Module(ITPM)<br />

Hos t Interface<br />

Intel Ma nagement<br />

Engine Crypt o<br />

Str ap<br />

PCIe Lo opback<br />

enable<br />

Res erved<br />

XOR<br />

000 = 10 66<br />

010 = 80 0<br />

011 = 66 7<br />

Others = Rese rved<br />

Low = Intel Ma nagement Engine Cr ypto Transp ort Lay er<br />

Secur ity (TLS) c iph er suite w ith no c onf<strong>id</strong>entiality<br />

High = Intel Manag ement Engine Cry pto TLS cipher suite<br />

w ith conf <strong>id</strong> entiality ( def <strong>au</strong>lt)<br />

Low = Enabled<br />

High = Disabled (d ef<strong>au</strong>lt)<br />

Low = Nor mal opera tion (Def<strong>au</strong>lt) :<br />

L ane Numb ered in Or der<br />

High = Rever se Lane s<br />

DMI x 4 mode [( G)MCH->ICH]:<br />

( 3->0 , 2-> 1, 1-> 2 and 0- >3)<br />

DMI x 2 mode [( G)MCH->ICH]:<br />

( 3->0 , 2->1 )<br />

Low = Only dig ita l display port ( SDVO/DP/iHDMI)<br />

o r PCIe is o perat ion al ( def <strong>au</strong>lt)<br />

High = Digita l d isp lay port ( SDVO/DP/iHDMI)<br />

a nd PCIe a re op erating s imultaneo usly<br />

v ia t he PEG por t<br />

Schematic Diagrams<br />

Sheet 4 of 42<br />

Cantiga 1/6, Host<br />

Cantiga 1/6, Host B - 5<br />

B.Schematic Diagrams