Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

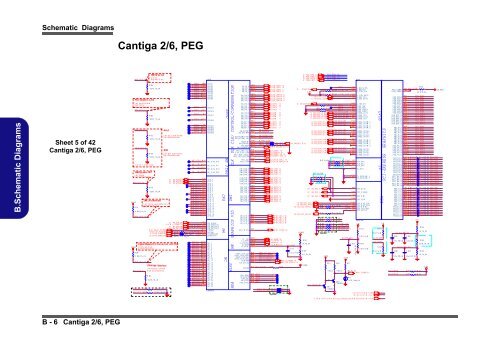

B.Schematic Diagrams<br />

Schematic Diagrams<br />

Sheet 5 of 42<br />

Cantiga 2/6, PEG<br />

B - 6 Cantiga 2/6, PEG<br />

Cantiga 2/6, PEG<br />

MCH _CF G _5<br />

DMI X2 se lect<br />

Lo w = X 2<br />

H i gh =X 4( D ef <strong>au</strong> lt )<br />

U 25 B<br />

37 PEG_TXP[0..15]<br />

37 PEG_TXN[0..15]<br />

37 PEG_RXP[0..15]<br />

37 PEG_R XN[0 ..1 5]<br />

i l<br />

i<br />

Z0501 M3 6 RSVD1<br />

R 36 6<br />

Z0502 N3 6<br />

Z0503 R3 3 RSVD2<br />

* 2. 2 1K _ 1 %_ 04<br />

Z0504 T33 RSVD3<br />

Z0505 AH 9 RSVD4<br />

Z0506 AH10 RSVD5<br />

RSVD6<br />

Z0507 AH12<br />

Z0508 AH13 RSVD7<br />

Z0509 K12 RSVD8<br />

RSVD9<br />

PCIe Graphics Lane<br />

Low= Reverse Lanes<br />

H gh = N or m a<br />

Operation(Def<strong>au</strong>lt)<br />

Z0510 T24<br />

RSVD1 4<br />

MCH _CF G _9<br />

Z0511 B31<br />

RSVD1 5<br />

Z0512 M1<br />

R 36 2<br />

RSVD1 7<br />

* 2. 2 1K _ 1 %_ 04<br />

Z0513 AY21<br />

RSVD2 0<br />

Z0514 B2<br />

Z0515 BG23 RSVD2 1<br />

Z0516 BF23 RSVD2 2<br />

MCH _CF G _1 2<br />

ALLZ<br />

Z0517 BH18 RSVD2 3<br />

Z0518 BF18 RSVD2 4<br />

RSVD2 5<br />

R 12 2<br />

Low= ALLZ mode enabled<br />

High = Dis a ble (D ef <strong>au</strong> lt)<br />

* 2. 2 1K _ 1 %_ 04<br />

MC H_ CFG_ 13<br />

XOR<br />

R 12 9<br />

Low= XOR mode enabled<br />

High = Dis a ble (D ef <strong>au</strong> lt)<br />

* 2. 2 1K _ 1 %_ 04<br />

ME _ J_ TC K AL 3 4<br />

ME _ JT A G_ TC K<br />

clo ck u n-ga ting<br />

ME _ J_ TD I AK34<br />

ME _ JT A G_ TD I<br />

ME _ J_ TD O AN35<br />

ME _ JT A G_ TD O<br />

FSB Dynamic ODT<br />

ME _ J_ TM S AM35 ME _ JT A G_ TM S<br />

Low= disable<br />

High=enable(Def<strong>au</strong>lt)<br />

T25<br />

18 MC H_BSEL0<br />

R2 5 CFG_ 0<br />

18 MC H_BSEL1<br />

CFG_ 1<br />

MCH_ CF G_ 1 6<br />

18 MC H_BSEL2<br />

P25<br />

MCH_ CF G_ 3 P20 CFG_ 2<br />

MCH_ CF G_ 4 P24 CFG_ 3<br />

R 11 0<br />

MCH_ CF G_ 5 C2 5 CFG_ 4<br />

MCH_ CF G_ 6 N2 4 CFG_ 5<br />

CFG_ 6<br />

* 2. 2 1K _ 1 %_ 04<br />

MCH_ CF G_ 7 M2 4 CFG_ 7<br />

MCH_ CF G_ 8 E21<br />

MCH_ CF G_ 9 C2 3 CFG_ 8<br />

MCH_ CF G_ 1 0 C2 4 CFG_ 9<br />

MCH_ CF G_ 1 1 N2 1 CFG_10<br />

DMI Ln e Rever sal<br />

MCH_ CF G_ 1 2 P21 CFG_11<br />

CFG_12<br />

3. 3 V S<br />

MCH_ CF G_ 1 3 T21<br />

L ow = N or m al o pe r at o n( D e f a ul t )<br />

MCH_ CF G_ 1 4 R2 0 CFG_13<br />

High=Reverse Lanes<br />

MCH_ CF G_ 1 5 M2 0 CFG_14<br />

R7 9<br />

MCH_ CF G_ 1 6 L21 CFG_15<br />

MCH_ CF G_ 1 7 H2 1 CFG_16<br />

CFG_17<br />

*4.02K_1%_04<br />

MCH_ CF G_ 1 8 P29 CFG_18<br />

MCH_ CF G_ 1 9 R2 8<br />

MCH_ CF G_ 2 0 T28 CFG_19<br />

MCH _CF G _1 9<br />

CFG_20<br />

15 PM _S Y N C #<br />

R2 9<br />

2,13,35 H_ DPRSTP#<br />

B7 PM_SYNC#<br />

PM_EXTTS0# N3 3 PM_DPRSTP#<br />

10 PM _E X TT S 0#<br />

PM_EXTTS1# P32 PM_EXT_TS#_0<br />

11 PM _E X TT S 1#<br />

AT 4 0 PM_EXT_TS#_1<br />

15 , 35 DELAY _PW RGD<br />

PW ROK<br />

14,22,37,38 PLT_R ST#<br />

PM_RSTIN# AT 1 1<br />

2,13 PM_TH RMTRIP#<br />

R148 100_1%_04 Z0534 T20 RSTIN#<br />

R1 2 6 *10m il_ s hort Z0535 R3 2 THERMTRIP#<br />

15 , 3 5 PM_DPRSLPVR<br />

R359 0_04<br />

DPRSL PVR<br />

PM_NC1 BG48<br />

Digital Dispaly Po rt Concu rr ent wiht PCie<br />

PM_NC2 BF48 NC _1<br />

PM_NC3 BD48 NC _2<br />

3. 3 V S Low=Only(Def<strong>au</strong>lt) PM_NC4 BC48 NC _3<br />

H ig h= s im ul t a ne ou s ly<br />

PM_NC5 BH47 NC _4<br />

NC _5<br />

PM_NC6 BG47<br />

R3 67<br />

PM_NC7 BE47 NC _6<br />

PM_NC8 BH46 NC _7<br />

*4.02K_1%_04<br />

PM_NC9 BF46 NC _8<br />

PM_NC10 BG45 NC _9<br />

NC _10 PM_NC11 BH44 NC _11 MCH _CF G _2 0<br />

PM_NC12 BH43<br />

PM_NC13 BH 6 NC _12 ITPM Hos t Interface<br />

PM_NC14 BH 5 NC _13 PM_NC15 BG 4 NC _14 Low=Interface is enable<br />

PM_NC16 BH 3 NC _15 NC _16 MCH_ CF G_ 6 H igh= disable(Def<strong>au</strong>lt)<br />

PM_NC17 BF3<br />

PM_NC18 BH 2 NC _17 PM_NC19 BG 2 NC _18 R 36 4<br />

PM_NC20 BE2 NC _19 PM_NC21 BG 1 NC _20 NC _21 *2.21K_1%_04<br />

PM_NC22 BF1 NC _22 PM_NC23 BD 1<br />

PM_NC24 BC 1 NC _23 PM_NC25 F1 NC _24 NC _25 AP24<br />

SA_CK_0<br />

M_CLK_ DDR 0 1 0<br />

AT21<br />

M_CLK_ DDR 1 1 0<br />

Z0572<br />

L32<br />

SA_CK_1 AV24<br />

M_CLK_ DDR 2 1 1<br />

12 G M_BL ON<br />

G 32 L_ B K LT _C TR L<br />

SB_CK_0 AU20<br />

R 12 0 * 10 K_0 4 L_C TRL_CLK M32 L_ B K LT _E N<br />

SB_CK_1<br />

M_CLK_ DDR 3 1 1<br />

3.3VS<br />

L_ CT RL_ CL K<br />

AR24<br />

M_CLK_ DDR 0# 10<br />

R 11 5 * 10 K_0 4 L_C TRL_DATA M33<br />

SA_C K#_0 AR21<br />

M_CLK_ DDR 1# 10<br />

12 GM _EDID_ CL K<br />

K33 L_ CT RL_ DATA<br />

SA_C K#_1 AU24<br />

J33 L_ DDC _CL K<br />

SB_C K#_0 AV20<br />

M_CLK_ DDR 2# 11 12 GM _EDID_ DAT A<br />

L_ DDC _DAT A<br />

SB_C K#_1<br />

M_CLK_ DDR 3# 11<br />

SA_CKE_0 BC28<br />

M_ CK E 0 1 0<br />

12 GM _ENAVDD<br />

M29 L_VDD_EN<br />

AY28<br />

M_ CK E 1 1 0<br />

R82 *2.37K_1%_04 Z0573<br />

C 44<br />

SA_CKE_1 AY36<br />

M_ CK E 2 1 1<br />

Z0574<br />

B43 LV D S _ I B G<br />

SB_CKE_0 BB36<br />

R93 *0_04<br />

Z0575<br />

E37 LV D S _ V B G<br />

SB_CKE_1<br />

M_ CK E 3 1 1<br />

R98 *0_04<br />

Z0576<br />

E38 LVDS_ VREF H<br />

BA17<br />

GM_LVDS_LCLKN C 41 LVDS_ VREF L<br />

SA_C S#_0<br />

M_ CS 0# 1 0<br />

12 GM_LVDS_LC LKN<br />

LVDSA_ CL K#<br />

AY16<br />

M_ CS 1# 1 0<br />

12 GM_LVDS_LC LKP<br />

GM_LVDS_LCLKP C 40<br />

SA_C S#_1 AV16<br />

M_ CS 2# 1 1<br />

12 GM_LVDS_UCLKN<br />

GM_ LVD S_UC LKN B37 LVDSA_ CL K<br />

SB_C S#_0 AR13<br />

12 GM_LVDS_UCLKP<br />

GM_ LVD S_UC LKP A37 LVDSB_ CL K#<br />

SB_C S#_1<br />

M_ CS 3# 1 1<br />

LVDSB_ CL K<br />

BD17<br />

GM_ LVD S_L 0N H 47<br />

SA_OD T_0<br />

M_ ODT 0 1 0<br />

12 G M_LVDS_L0N<br />

LVDSA_ DAT A# _ 0<br />

SA_OD T_1 AY17<br />

M_ ODT 1 1 0<br />

12 G M_LVDS_L1N<br />

GM_ LVD S_L 1N<br />

E46 LVDSA_ DAT A# _ 1<br />

BF15<br />

12 G M_LVDS_L2N<br />

G 40<br />

SB_OD T_0<br />

M_ ODT 2 1 1<br />

GM_ LVD S_L 2N<br />

AY13<br />

A40 LVDSA_ DAT A# _ 2<br />

SB_OD T_1<br />

M_ ODT 3 1 1<br />

LVDSA_ DAT A# _ 3<br />

BG22 SM_RCOM P<br />

GM_ LVD S_L 0P H 48<br />

SM_RCOMP BH21 SM_RCOM P#<br />

12 G M_LVDS_L0P<br />

GM_ LVD S_L 1P D 45 LVDSA_ DAT A_ 0<br />

SM_RCO MP#<br />

12 G M_LVDS_L1P<br />

LVDSA_ DAT A_ 1<br />

12 G M_LVDS_L2P<br />

GM_ LVD S_L 2P<br />

F40<br />

BF28 SM_RCOMP_VOH B40 LVDSA_ DAT A_ 2<br />

SM_ RCOM P_ VOH BH28 SM_RCOMP_VOL LVDSA_ DAT A_ 3<br />

SM _RC OMP_VOL<br />

12 G M_LVDS_U0N<br />

GM_ LVD S_U0 N A41<br />

AV42 M_ V RE F _M CH<br />

GM_ LVD S_U1 N H 38 LVDSB_ DAT A# _ 0<br />

SM_VR EF<br />

12 G M_LVDS_U1N<br />

LVDSB_ DAT A# _ 1<br />

SM _PWROK AR36 Z0561 R20 7 * 10 mil_s ho rt<br />

1. 5 V _P W R G D 15 , 3 1 12 G M_LVDS_U2N<br />

GM_ LVD S_U2 N G 37 LVDSB_ DAT A# _ 2<br />

BF17 Z0562 R155 499_1%_04<br />

J37<br />

SM_REXT BC36<br />

LVDSB_ DAT A# _ 3<br />

SM_D RAMRST#<br />

DDR3 _ DRAMRST# 1 0 ,11<br />

12 G M_LVDS_U0P<br />

GM_ LVD S_U0 P B42<br />

B38<br />

GM_ LVD S_U1 P G 38 LVDSB_ DAT A_ 0<br />

DPLL_REF_CLK<br />

CL K_ DREF 1 8<br />

12 G M_LVDS_U1P<br />

LVDSB_ DAT A_ 1<br />

D P LL _R E F_ C L K # A38<br />

CL K_ DREF# 18<br />

12 G M_LVDS_U2P<br />

GM_ LVD S_U2 P F37 LVDSB_ DAT A_ 2<br />

E41<br />

CL K_ DREF_ SS 18<br />

K37<br />

DPLL_REF_SSCLK F41<br />

LVDSB_ DAT A_ 3<br />

DPLL_REF_SSCLK#<br />

CL K_ DREF_ SS# 1 8<br />

F43<br />

PEG_CLK E43<br />

CL K_ PCIE_ 3GPL L 1 8<br />

D VT : F or PM R 10 1 0 _ 04 Z0581 F25<br />

PEG_CLK#<br />

CL K_ PCIE_ 3GPL L # 1 8<br />

TVA_DAC<br />

R 10 5 0 _ 04 Z0582 H 25<br />

R 11 1 0 _ 04 Z0583 K25 TVB_DAC<br />

TVC_ DAC<br />

AE41<br />

H 24<br />

DM I_RXN_ 0 AE37<br />

DMI_ TXN0 14<br />

TV _ R T N<br />

DM I_RXN_ 1<br />

DMI_ TXN1 14<br />

DM I_RXN_ 2 AE47<br />

DMI_ TXN2 14<br />

AH39<br />

DMI_ TXN3 14<br />

DVT: F o r PM<br />

DM I_RXN_ 3<br />

C 31<br />

AE40<br />

R119 0_04<br />

E32 TV_DCONSEL_0 D MI_R XP_ 0 AE38<br />

DMI_ TXP0 1 4<br />

R113 0_04<br />

TV_DCONSEL_1 D MI_R XP_ 1 AE48<br />

DMI_ TXP1 1 4<br />

R103 0_04<br />

D MI_R XP_ 2<br />

DMI_ TXP2 1 4<br />

AH40<br />

D MI_R XP_ 3<br />

DMI_ TXP3 1 4<br />

AE35<br />

DMI_ TXN_ 0 AE43<br />

DMI_ RXN0 1 4<br />

E28<br />

DMI_ TXN_ 1 AE46<br />

DMI_ RXN1 1 4<br />

28 GM_ DAC_ B<br />

CRT_BL UE<br />

DMI_ TXN_ 2<br />

DMI_ RXN2 1 4<br />

DMI_ TXN_ 3 AH42<br />

DMI_ RXN3 1 4<br />

28 GM_ DAC_ G<br />

G 28 CRT_G REEN<br />

AD35<br />

J28<br />

DM I_TXP_ 0 AE44<br />

DMI_ RXP0 1 4<br />

28 GM_ DAC_ R<br />

CRT_R ED<br />

DM I_TXP_ 1 AF46<br />

DMI_ RXP1 1 4<br />

G 29<br />

DM I_TXP_ 2 AH43<br />

DMI_ RXP2 1 4<br />

CRT_IRTN<br />

DM I_TXP_ 3<br />

DMI_ RXP3 1 4<br />

28 GM_DDC_CLK<br />

H 32<br />

28 GM_DDC_ DATA<br />

J32 CRT_D DC_ CLK<br />

R 80 * 30 .1_ 1 %_ 04 CH J29 CRT_D DC_ DATA<br />

28 G M_ DAC_ HSYNC<br />

R 94 0 _ 04<br />

Z0585 E29 CRT_H SY NC<br />

CV L29 CRT_TVO_IREF<br />

CRT_VSYN C<br />

R 75 * 30 .1_ 1 %_ 04<br />

B33<br />

28 G M_ DAC_ VSY NC<br />

GFX_VID_0 B32<br />

DF GT_ VID _0 30<br />

GFX_VID_1 G3 3<br />

DF GT_ VID _1 30<br />

R 81 0 _ 04 CH<br />

GFX_VID_2<br />

DF GT_ VID _2 30<br />

GFX_VID_3 F33<br />

DF GT_ VID _3 30<br />

R 74 0 _ 04 CV<br />

CANTIGA<br />

E33<br />

GFX_VID_4<br />

DF GT_ VID _4 30<br />

R 12 7 0 _ 04 L_C TRL_CLK<br />

1.5V<br />

1.5V<br />

R 11 2 0 _ 04 L_C TRL_DATA<br />

R 11 4 0 _ 04 GM _EDID _CL K<br />

C3 4<br />

R 85 0 _ 04 GM _EDID _DAT A<br />

R 15 7<br />

R 16 1<br />

GF X_ VR _EN<br />

DF GT_ VR_EN 3 0<br />

1. 0 5V M<br />

For PM<br />

80 . 6_ 1 %_ 04<br />

1 0 K _1 %_ 04<br />

AH37<br />

M_V R EF _ MCH<br />

SM _RC OMP<br />

CL _ CLK<br />

C L_ CL K0 1 5<br />

C L_ DATA AH36<br />

C L_ DATA0 15<br />

R1 47<br />

AN36<br />

MP W ROK 1 5<br />

SM_R COMP#<br />

CL _PW ROK AJ 35<br />

1K_1%_04<br />

C 25 3 R 15 6<br />

CL_ RST # AH34<br />

CL _R ST # 0 1 5 CL _VREF<br />

CL _VR EF<br />

R 16 0<br />

C2 1 0<br />

1 0 K _1 %_ 04<br />

R 14 6<br />

80 . 6_ 1 %_ 04<br />

N2 8 DDPC _CT_ CLK<br />

0 . 1u _1 0 V _0 4<br />

DDPC_ CTRL CLK M2 8 DDPC _CT_ DATA<br />

511_1%_04<br />

DDPC_CTRLDATA G3 6 SDVO_CT_CLK<br />

3. 3 V S<br />

SDVO_CTRLCLK E36 SDVO_CT_DATA<br />

3. 3 V S<br />

SDVO_CTRLDATA<br />

CL KR EQ# K36 MCH _CLKREQ#<br />

MCH_ CL K RE Q# 18<br />

H3 6<br />

ICH _SYN C#<br />

MCH_ ICH _SYNC # 1 5<br />

R7 2 R7 8<br />

R7 7<br />

1.05VS<br />

B12 MCH_ TS A T N# R3 68 5 6_ 04<br />

TS A T N #<br />

*1 K _0 4 *1 K _0 4 10K_1%_04<br />

MCH_ T HE RM 2 2<br />

B28 Z0 5 67<br />

HDA_ BCLK B30 Z0 5 68<br />

HD A_ RST # B29 Z0 5 69<br />

RT 1<br />

H DA_SDI<br />

HD A_ SDO C2 9 Z0 5 70<br />

B<br />

N TC_100K_06<br />

A28 Z0 5 71<br />

Q2 1<br />

HDA_SYNC<br />

*2 N3 90 4<br />

MCH _T SATN # B<br />

Q5 1<br />

R12 8<br />

T37 PEG _CO MP<br />

PEG_COMPI T36<br />

VCC_PEG<br />

PEG_C OMPO<br />

4 9 . 9_ 1% _0 4<br />

H4 4<br />

PEG_RXN0<br />

PEG_RX#_0 J46<br />

PEG_RXN1<br />

PEG_RX#_1 L44<br />

PEG_RXN2<br />

PEG_RX#_2 L40<br />

PEG_RXN3<br />

PEG_RX#_3<br />

PEG_RX#_4 N4 1<br />

PEG_RXN4<br />

P48<br />

PEG_RXN5<br />

PEG_RX#_5 N4 4<br />

PEG_RXN6<br />

PEG_RX#_6 T43<br />

PEG_RXN7<br />

PEG_RX#_7 U4 3<br />

PEG_RXN8<br />

PEG_RX#_8 Y43<br />

PEG_RXN9<br />

PEG_RX#_9<br />

Y48<br />

PEG_RXN10<br />

PEG_RX#_10 Y36<br />

PEG_RXN11<br />

PEG_RX#_11 AA43<br />

PEG_RXN12<br />

PEG_RX#_12 AD37<br />

PEG_RXN13<br />

PEG_RX#_13 AC47<br />

PEG_RXN14<br />

PEG_RX#_14 PEG_RX#_15 AD39<br />

PEG_RXN15<br />

H4 3<br />

PEG_RXP0<br />

PEG _R X_0 J44<br />

PEG_RXP1<br />

PEG _R X_1 L43<br />

PEG_RXP2<br />

PEG _R X_2 L41<br />

PEG_RXP3<br />

PEG _R X_3<br />

N4 0<br />

PEG_RXP4<br />

PEG _R X_4 P47<br />

PEG_RXP5<br />

PEG _R X_5 N4 3<br />

PEG_RXP6<br />

PEG _R X_6 T42<br />

PEG_RXP7<br />

PEG _R X_7 U4 2<br />

PEG_RXP8<br />

PEG _R X_8<br />

PEG _R X_9 Y42<br />

PEG_RXP9<br />

W47<br />

PEG_RXP10<br />

PEG_RX_10 Y37<br />

PEG_RXP11<br />

PEG_RX_11 AA42<br />

PEG_RXP12<br />

PEG_RX_12 AD36<br />

PEG_RXP13<br />

PEG_RX_13<br />

PEG_RX_14 AC48<br />

PEG_RXP14<br />

AD40<br />

PEG_RXP15<br />

PEG_RX_15<br />

J41 G TN 0 C 1 55 0. 1 u_ 1 0V _ 04 PEG_TXN0<br />

PEG_TX#_0 M4 6 G TN 1 C 1 74 0. 1 u_ 1 0V _ 04 PEG_TXN1<br />

PEG_TX#_1 M4 7 G TN 2 C 1 53 0. 1 u_ 1 0V _ 04 PEG_TXN2<br />

PEG_TX#_2<br />

M4 0 G TN 3 C 1 72 0. 1 u_ 1 0V _ 04 PEG_TXN3<br />

PEG_TX#_3 M4 2 G TN 4 C 1 51 0. 1 u_ 1 0V _ 04 PEG_TXN4<br />

PEG_TX#_4 R4 8 G TN 5 C 1 70 0. 1 u_ 1 0V _ 04 PEG_TXN5<br />

PEG_TX#_5 N3 8 G TN 6 C 1 49 0. 1 u_ 1 0V _ 04 PEG_TXN6<br />

PEG_TX#_6 T40 G TN 7 C 1 68 0. 1 u_ 1 0V _ 04 PEG_TXN7<br />

PEG_TX#_7<br />

PEG_TX#_8 U3 7 G TN 8 C 1 47 0. 1 u_ 1 0V _ 04 PEG_TXN8<br />

U4 0 G TN 9 C 1 67 0. 1 u_ 1 0V _ 04 PEG_TXN9<br />

PEG_TX#_9 Y40 G TN 10 C 1 46 0. 1 u_ 1 0V _ 04 PEG_TXN10<br />

PEG_TX#_10 AA46G<br />

TN 11 C 1 64 0. 1 u_ 1 0V _ 04 PEG_TXN11<br />

PEG_TX#_11 AA37G<br />

TN 12 C 1 62 0. 1 u_ 1 0V _ 04 PEG_TXN12<br />

PEG_TX#_12 AA40G<br />

TN 13 C 1 42 0. 1 u_ 1 0V _ 04 PEG_TXN13<br />

PEG_TX#_13<br />

AD43G<br />

TN 14 C 1 61 0. 1 u_ 1 0V _ 04 PEG_TXN14<br />

PEG_TX#_14 AC46G<br />

TN 15 C 1 44 0. 1 u_ 1 0V _ 04 PEG_TXN15<br />

PEG_TX#_15<br />

J42 G TP0 C 1 56 0. 1 u_ 1 0V _ 04 PEG_TXP0<br />

PEG_TX_0 L46 G TP1 C 1 75 0. 1 u_ 1 0V _ 04 PEG_TXP1<br />

PEG_TX_1<br />

PEG_TX_2 M4 8 G TP2 C 1 54 0. 1 u_ 1 0V _ 04 PEG_TXP2<br />

M3 9 G TP3 C 1 73 0. 1 u_ 1 0V _ 04 PEG_TXP3<br />

PEG_TX_3 M4 3 G TP4 C 1 52 0. 1 u_ 1 0V _ 04 PEG_TXP4<br />

PEG_TX_4 R4 7 G TP5 C 1 71 0. 1 u_ 1 0V _ 04 PEG_TXP5<br />

PEG_TX_5 N3 7 G TP6 C 1 50 0. 1 u_ 1 0V _ 04 PEG_TXP6<br />

PEG_TX_6 T39 G TP7 C 1 69 0. 1 u_ 1 0V _ 04 PEG_TXP7<br />

PEG_TX_7<br />

U3 6 G TP8 C 1 48 0. 1 u_ 1 0V _ 04 PEG_TXP8<br />

PEG_TX_8 U3 9 G TP9 C 1 66 0. 1 u_ 1 0V _ 04 PEG_TXP9<br />

PEG_TX_9 Y39 G TP1 0 C 1 45 0. 1 u_ 1 0V _ 04 PEG_TXP10<br />

PEG_TX_10 Y46 G TP1 1 C 1 65 0. 1 u_ 1 0V _ 04 PEG_TXP11<br />

PEG_TX_11 AA36G<br />

TP1 2 C 1 63 0. 1 u_ 1 0V _ 04<br />

PEG_TXP12<br />

PEG_TX_12<br />

PEG_TX_13 AA39G<br />

TP1 3 C 1 41 0. 1 u_ 1 0V _ 04 PEG_TXP13<br />

AD42G<br />

TP1 4 C 1 60 0. 1 u_ 1 0V _ 04 PEG_TXP14<br />

PEG_TX_14 AD46G<br />

TP1 5 C 1 43 0. 1 u_ 1 0V _ 04 PEG_TXP15<br />

PEG_TX_15<br />

1.5V<br />

R1 6 4<br />

1K_1%_04<br />

SM_RCO MP_VOH<br />

C2 51<br />

C 25 5<br />

0.01u_50V_04 2 . 2u _6 . 3V _ 0 6 R1 6 2<br />

3. 0 1K _ 1% _ 04<br />

SM _RC OMP_VO L<br />

C2 52<br />

C 25 4<br />

R1 6 3<br />

1K_1%_04<br />

0.01u_50V_04 2.2u_6.3V_06<br />

3.3VS<br />

PM _EXTTS0#<br />

R 121 10K_04<br />

PM _EXTTS1#<br />

R 125 10K_04<br />

MCH_ CF G_ 7 R3 63 *2 .21 K_ 1% _0 6<br />

SDVO_CT_CLK R109 *10mil_short<br />

*2 N3 90 4<br />

MCH_ CF G_ 1 0R3<br />

65 *2 .21 K_ 1% _0 6<br />

C ANTIG A<br />

SDVO_CT_DATA R108<br />

For PM<br />

*10mil_short<br />

2 , 3, 4 , 9, 1 3, 1 6 ,18,33 1. 0 5V S<br />

7,9,10,11,27,31,33 1. 5 V<br />

CFG<br />

PM<br />

RSVD<br />

ME J TAG<br />

NC<br />

DDR C LK/ CON TROL/C OMPENSA TION<br />

CLK<br />

DMI<br />

GRAPH ICS VID<br />

ME<br />

MISC<br />

HDA<br />

E C<br />

PEG_TXP[0..15]<br />

PEG_TXN[0..15]<br />

PEG_RXP[0..15]<br />

P E G _ R X N [ 0. . 1 5]<br />

E C<br />

1<br />

2<br />

2,3,9,12,13,14,15,16,1 9 ,20 ,21 ,22 ,2 3,2 4,2 5 ,2 6 , 28 , 30 , 32 , 3 3, 3 5, 3 6 ,37,38 3. 3 V S<br />

2. 2 u _6 . 3V _ 06<br />

U2 5C<br />

LV DS<br />

PC I- EXP RE SS GR AP HIC S<br />

TV<br />

VG A