You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

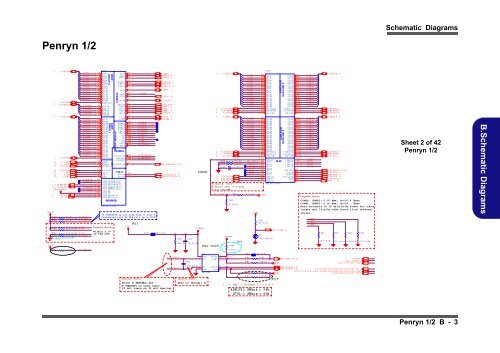

Penryn 1/2<br />

1.05V S<br />

4<br />

4 H_ADSTB#0<br />

4 H _R EQ# [4 :0 ]<br />

4<br />

4<br />

13<br />

13<br />

13<br />

13<br />

13<br />

13<br />

13<br />

H_ A# [3 5:3 ]<br />

H_ADSTB#1<br />

H_ A2 0M #<br />

H _ F ERR #<br />

H_ IG NNE #<br />

H_STPCLK#<br />

H_ INTR<br />

H _N MI<br />

H_ SMI #<br />

3 H _TH ERM DA2<br />

3 H _ TH ERM DC2<br />

C PU_ GT L REF 2<br />

3<br />

3<br />

R 358<br />

R 52<br />

56_04<br />

H_ IER R#<br />

54.9_1%_04 H_PR EQ#<br />

R 369 56_04<br />

H_ PR OCH OT#<br />

R 32 6<br />

R 32 9<br />

5 4 .9 _1 % _ 04 H_ TMS<br />

5 4 .9 _1 % _ 04 H_ TDI<br />

R 32 7 5 4 .9 _1 % _ 04 H_ TCK<br />

R 64 1 5 4 .9 _1 % _ 04 H_ TRST#<br />

D VT<br />

H_ A# [3 5:3 ]<br />

TD O _ M<br />

TD I _ M<br />

3.3VS<br />

R 357 1K_04<br />

H_ A# 3<br />

H_ A# 4<br />

H_ A# 5<br />

H_ A# 6<br />

H_ A# 7<br />

H_ A# 8<br />

H_ A# 9<br />

H_A#10<br />

H_A#11<br />

H_A#12<br />

H_A#13<br />

H_A#14<br />

H_A#15<br />

H_A#16<br />

H_ RE Q# 0<br />

H_ RE Q# 1<br />

H_ RE Q# 2<br />

H_ RE Q# 3<br />

H_ RE Q# 4<br />

H_A#17<br />

H_A#18<br />

H_A#19<br />

H_A#20<br />

H_A#21<br />

H_A#22<br />

H_A#23<br />

H_A#24<br />

H_A#25<br />

H_A#26<br />

H_A#27<br />

J4<br />

L5<br />

L4<br />

K5<br />

M3<br />

N 2<br />

J1<br />

N 3<br />

P5<br />

P2<br />

L2<br />

P4<br />

P1<br />

R 1<br />

M1<br />

K3<br />

H 2<br />

K2<br />

J3<br />

L1<br />

Y 2<br />

U 5<br />

R 3<br />

W6<br />

U 4<br />

Y 5<br />

U 1<br />

R 4<br />

T5<br />

T3<br />

W2<br />

U22A<br />

A[3]#<br />

A[4]#<br />

A[5]#<br />

A[6]#<br />

A[7]#<br />

A[8]#<br />

A[9]#<br />

A[10]#<br />

A[11]#<br />

A[12]#<br />

A[13]#<br />

A[14]#<br />

A[15]#<br />

A[16]#<br />

ADSTB[0]#<br />

REQ [0]#<br />

REQ [1]#<br />

REQ [2]#<br />

REQ [3]#<br />

REQ [4]#<br />

A[17]#<br />

A[18]#<br />

A[19]#<br />

A[20]#<br />

A[21]#<br />

A[22]#<br />

A[23]#<br />

A[24]#<br />

A[25]#<br />

A[26]#<br />

AD S#<br />

BNR #<br />

BPR I#<br />

DEFER #<br />

D RDY #<br />

DBSY #<br />

BR0#<br />

IERR #<br />

INIT#<br />

LOC K#<br />

RESET#<br />

RS[0 ]#<br />

RS[1 ]#<br />

RS[2 ]#<br />

TRDY #<br />

HIT#<br />

H ITM #<br />

BPM[0]#<br />

BPM[1]#<br />

BPM[2]#<br />

BPM[3]#<br />

PRDY #<br />

PREQ #<br />

TC K<br />

TD I<br />

H1<br />

E2<br />

G5<br />

H5<br />

F21<br />

E1<br />

F1<br />

D2 0<br />

B3<br />

H4<br />

C1<br />

F3<br />

F4<br />

G3<br />

G2<br />

G6<br />

E4<br />

AD4<br />

AD3<br />

AD1<br />

AC4<br />

AC2<br />

AC1<br />

AC5<br />

AA6<br />

AB3<br />

H_A#28<br />

H_A#29<br />

H_A#30<br />

H_A#31<br />

H_A#32<br />

H_A#33<br />

H_A#34<br />

H_A#35<br />

W5<br />

Y 4<br />

U 2<br />

V4<br />

W3<br />

AA4<br />

AB2<br />

AA3<br />

V1<br />

A6<br />

A5<br />

C 4<br />

A[27]#<br />

TDO<br />

A[28]#<br />

TM S<br />

A[29]#<br />

TRST#<br />

A[30]#<br />

DBR #<br />

A[31]#<br />

A[32]#<br />

A[33]# THERMAL<br />

A[34]#<br />

A[35]#<br />

PR OCH OT#<br />

ADSTB[1]# THER MD A<br />

TH E R M D C<br />

A20M #<br />

FERR # TH ERM TR IP#<br />

IGN NE#<br />

AB5<br />

AB6<br />

C2 0<br />

D2 1<br />

A24<br />

B25<br />

C7<br />

D 5<br />

STP CLK#<br />

C 6<br />

B4 LI N T 0<br />

LI N T 1<br />

A3<br />

SMI#<br />

H_BPM _2#1<br />

H_BPM _2#0<br />

M4<br />

N 5<br />

T2<br />

V3<br />

B2<br />

D 2<br />

ADDR<br />

GROUP_0<br />

ADDR<br />

GROUP_1<br />

ICH<br />

Layout Note:<br />

XDP/ITP SIGNALS<br />

CONTROL<br />

RES ERV ED<br />

SOC KET G 479P<br />

H CLK<br />

BCLK[0]<br />

BCLK[1]<br />

RSVD [01]/BPM _2#[1]<br />

RSVD [02]/BPM _2#[0]<br />

RSVD [03]/THR MD A_2<br />

RSVD [04 ]/THR MD C_ 2<br />

RSVD [05]BPM _2#[2]<br />

RSVD [06]<br />

H_BPM _2#2<br />

Z0206<br />

D2 2<br />

RSVD [07]<br />

D 3<br />

F6 RSVD [08 ]/TDO _M<br />

RSVD [09 ]/TDI_ M<br />

ITP_ DBRS T#<br />

A22<br />

A21<br />

PV T<br />

H_BPM 0#<br />

H_BPM 1#<br />

H_BPM 2#<br />

H_BPM 3#<br />

H_ PR DY#<br />

H_PR EQ#<br />

H_ TCK<br />

H_ TDI<br />

H_ TDO<br />

H_ TMS<br />

H_ TRST#<br />

ITP_ DBRS T#<br />

H_ PR OCH OT#<br />

H_THER MD A1<br />

H_ THER MD C1<br />

If P ROC HO T# is n ot ur ed, th en it m ust b e<br />

terminated with 56-Ohm pull-up to VCCP.<br />

Within 2.0"<br />

of the CPU<br />

3.3V<br />

Layout Note:<br />

H_ IER R#<br />

R 3 73 *1 0m i l _s h or t<br />

H_ADS# 4<br />

H_ BNR # 4<br />

H_ BPRI# 4<br />

H_ DEFER # 4<br />

H_ DR DY# 4<br />

H_ DBSY # 4<br />

H_ BR0 # 4<br />

H_ INIT# 1 3<br />

H_ L OCK# 4<br />

H_ CPU RST# 4<br />

H_ RS# 0 4<br />

H_ RS# 1 4<br />

H_ RS# 2 4<br />

H_ TRDY # 4<br />

H_ HIT# 4<br />

H_ HITM# 4<br />

PM_ THRM TRIP# 5 ,13<br />

CL K_ CPU_ BC LK 18<br />

CL K_ CPU_ BC LK# 1 8<br />

H _TH ERMD A1<br />

H _T H ERMD C1<br />

Route H_THERMDA and<br />

H_THERMDC on same layer.<br />

10 mil trace on 10 mil spacing.<br />

10mils<br />

V_THR M<br />

1<br />

2<br />

U2 4<br />

VDD<br />

D+<br />

1000p_50V_04 3<br />

D-<br />

5<br />

GND<br />

ASC7525<br />

Near to Thermal IC<br />

4<br />

4<br />

4<br />

4<br />

4<br />

4<br />

4<br />

4<br />

C PU_ GT L REF 1<br />

R3 55 C4 6 3<br />

100K_04 10u_10V_08<br />

Near toCPU<br />

C 47 8<br />

Layout Note:<br />

H _D ST BN# 1<br />

H_ D STBP #1<br />

H _D INV# 1<br />

7<br />

8<br />

R3 8 0<br />

2K _1 % _0 4<br />

4<br />

TH E R M 6 H _ ALER T 1<br />

ALERT<br />

S DAT A<br />

SCLK<br />

H _D#[63:0]<br />

H _D ST BN# 0<br />

H_ D STBP #0<br />

H _D INV# 0<br />

H _D#[63:0]<br />

V_THR M<br />

DVT<br />

H_ D# 0<br />

H_ D# 1<br />

H_ D# 2<br />

H_ D# 3<br />

H_ D# 4<br />

H_ D# 5<br />

H_ D# 6<br />

H_ D# 7<br />

H_ D# 8<br />

H_ D# 9<br />

H_ D# 1 0<br />

H_ D# 1 1<br />

H_ D# 1 2<br />

H_ D# 1 3<br />

H_ D# 1 4<br />

H_ D# 1 5<br />

H_ D# 1 6<br />

H_ D# 1 7<br />

H_ D# 1 8<br />

H_ D# 1 9<br />

H_ D# 2 0<br />

H_ D# 2 1<br />

H_ D# 2 2<br />

H_ D# 2 3<br />

H_ D# 2 4<br />

H_ D# 2 5<br />

H_ D# 2 6<br />

H_ D# 2 7<br />

H_ D# 2 8<br />

H_ D# 2 9<br />

H_ D# 3 0<br />

H_ D# 3 1<br />

R3 7 6 *1K_ 0 4<br />

R3 7 5 *1K_ 0 4<br />

C4 6 8 * 0.1 u _ X7 R_ 0 4<br />

18 C PU_BSEL0<br />

18 C PU_BSEL1<br />

18 C PU_BSEL2<br />

A D2 6<br />

CPU _TEST1 C2 3<br />

CPU _TEST2 D2 5<br />

Z0210<br />

C2 4<br />

CPU _TEST4 AF26<br />

Z0211<br />

AF1<br />

Z0212<br />

A26<br />

Z0213<br />

C 3<br />

B22<br />

B23<br />

C2 1<br />

R 2 6<br />

GT LR EF<br />

C OMP [0]<br />

MI SC<br />

U 2 6<br />

TEST1<br />

C OMP [1]<br />

A A1<br />

TEST2<br />

C OMP [2] Y 1<br />

TEST3<br />

C OMP [3]<br />

TEST4<br />

E 5<br />

TEST5<br />

DPR STP#<br />

B 5<br />

TEST6<br />

D PSLP# D 2 4<br />

TEST7<br />

DPW R #<br />

D 6<br />

BSEL[ 0]<br />

PW R GO OD D 7<br />

BSEL[ 1]<br />

SLP# A E6<br />

BSEL[ 2]<br />

P SI#<br />

Layout note:<br />

Zo=55 ohm, 0.5"max<br />

for GTLREF<br />

SOC KET G 479P<br />

R 3 88<br />

*10K_04<br />

R379 1K_1%_04<br />

VD D3<br />

N2 2<br />

K25<br />

P26<br />

R2 3<br />

L23<br />

M2 4<br />

L22<br />

M2 3<br />

P25<br />

P23<br />

P22<br />

T24<br />

R2 4<br />

1.05VS<br />

R3 9 2<br />

*10K_1%_04<br />

R 38 9 *1 0m il_s h ort<br />

R 39 0 * 0 _0 4<br />

R 391 * 10K_04<br />

R 383 4.7K_04<br />

R 387 4.7K_04<br />

U2 2 B<br />

E22<br />

F24 D[0 ]#<br />

D[1 ]#<br />

E26<br />

G2 2 D[2 ]#<br />

F23 D[3 ]#<br />

D[4 ]#<br />

G2 5<br />

E25 D[5 ]#<br />

D[6 ]#<br />

E23<br />

K24 D[7 ]#<br />

D[8 ]#<br />

G2 4<br />

J24 D[9 ]#<br />

D[1 0]#<br />

J23<br />

H2 2 D[1 1]#<br />

F26 D[1 2]#<br />

K22 D[1 3]#<br />

H2 3 D[1 4]#<br />

D[1 5]#<br />

J26<br />

H2 6 DSTBN[0 ]#<br />

DSTBP[0]#<br />

H2 5<br />

DINV[ 0]#<br />

D[1 6]#<br />

D[1 7]#<br />

D[1 8]#<br />

D[1 9]#<br />

D[2 0]#<br />

D[2 1]#<br />

D[2 2]#<br />

D[2 3]#<br />

D[2 4]#<br />

D[2 5]#<br />

D[2 6]#<br />

D[2 7]#<br />

D[2 8]#<br />

L25<br />

T25 D[2 9]#<br />

D[3 0]#<br />

N2 5<br />

L26 D[3 1]#<br />

DSTBN[1 ]#<br />

M2 6<br />

N2 4 DSTBP[1]#<br />

DINV[ 1]#<br />

RT2<br />

* NTC_100K_06<br />

? ? ? VGA? ? thermal IC ? ? ? ?<br />

1<br />

2<br />

A DM 103 1 SM bu s = 9 8h<br />

G7 81- 1 SM bu s = 4 Dh<br />

CPU _TH ERM 22<br />

VD D3<br />

H_D#32<br />

H_D#33<br />

H_D#34<br />

H_D#35<br />

H_D#36<br />

H_D#37<br />

H_D#38<br />

H_D#39<br />

H_D#40<br />

H_D#41<br />

H_D#42<br />

H_D#43<br />

H_D#44<br />

H_D#45<br />

H_D#46<br />

H_D#47<br />

H_D#48<br />

H_D#49<br />

H_D#50<br />

H_D#51<br />

H_D#52<br />

H_D#53<br />

H_D#54<br />

H_D#55<br />

H_D#56<br />

H_D#57<br />

H_D#58<br />

H_D#59<br />

H_D#60<br />

H_D#61<br />

H_D#62<br />

H_D#63<br />

Layout note:<br />

SMD_THERM1 3,22<br />

SMC_THERM1 3,22<br />

14,15, 16,19,21,27,28,29,30,31,32,34,36,37,38 3.3V<br />

3,5,9,12,13,14,15,16,19,20,21, 22,23,24,25,26,28,30,32,33,35,36,37,38 3.3VS<br />

VD D3<br />

13,19,22,24,29,32,33,34,37 VDD 3<br />

PVT<br />

DATA GRP 0<br />

DATA GRP 2<br />

DATA GRP 1<br />

Y 2 2<br />

D[32]# A B24<br />

D[33]#<br />

V 24<br />

D[34]# V 26<br />

D[35]# V 23<br />

D[36]#<br />

T22<br />

D[37]# U 2 5<br />

D[38]#<br />

U 2 3<br />

D[39]# Y 2 5<br />

D[40]#<br />

W 22<br />

D[41]# Y 2 3<br />

D[42]#<br />

W 24<br />

D[43]# W 25<br />

D[44]# A A23<br />

D[45]# A A24<br />

D[46]# A B25<br />

D[47]#<br />

Y 2 6<br />

D STBN [2 ]# A A26<br />

D ST BP[2 ]#<br />

U 2 2<br />

DIN V[2 ]#<br />

A E24<br />

D[48]# A D2 4<br />

D[49]# A A21<br />

D[50]# A B22<br />

D[51]#<br />

A B21<br />

D[52]# A C2 6<br />

D[53]#<br />

A D2 0<br />

D[54]# A E22<br />

D[55]#<br />

A F 23<br />

D[56]# A C2 5<br />

D[57]# A E21<br />

D[58]# A D2 1<br />

D[59]# A C2 2<br />

D[60]#<br />

A D2 3<br />

D[61]# A F 22<br />

D[62]#<br />

A C2 3<br />

D[63]# A E25<br />

D STBN [3 ]#<br />

A F 24<br />

D ST BP[3 ]# A C2 0<br />

DIN V[3 ]#<br />

DATA GRP 3<br />

PM_THRM # 3,15,22<br />

CO MP0<br />

CO MP1<br />

CO MP2<br />

CO MP3<br />

C OMP 0<br />

C OMP 1<br />

C OMP 2<br />

C OMP 3<br />

R5 6<br />

54 . 9 _1 % _ 04<br />

H_ D# [6 3 :0] 4<br />

H_ DS TBN #2 4<br />

H_ DS TBP# 2 4<br />

H_ DI NV# 2 4<br />

H_ D# [6 3 :0] 4<br />

H_ DS TBN #3 4<br />

H_ DS TBP# 3 4<br />

H_ DI NV# 3 4<br />

H_ DP RSTP# 5,1 3 ,3 5<br />

H_ DP SLP# 1 3<br />

H_ DP W R# 4<br />

H_ PW R GD 13<br />

H_ CP USL P# 4<br />

PSI# 35<br />

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms<br />

COMP1, COMP3: 0.5" Max, Zo=55 Ohms<br />

Best es<strong>tim</strong>ate is 18 mils w<strong>id</strong>e trace for outer<br />

layers and 14 mils w<strong>id</strong>e trace if on internal<br />

layers.<br />

R5 7<br />

R382<br />

R 3 81<br />

27.4_1%_04 54.9_1%_04 27.4_1%_04<br />

3 V_THR M<br />

3 CPU _ GTLR EF2<br />

3,4,5,9,13,16,18,33 1.05VS<br />

Schematic Diagrams<br />

Sheet 2 of 42<br />

Penryn 1/2<br />

Penryn 1/2 B - 3<br />

B.Schematic Diagrams