DATA SHEET - IEETA

DATA SHEET - IEETA

DATA SHEET - IEETA

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Philips Semiconductors Product specification<br />

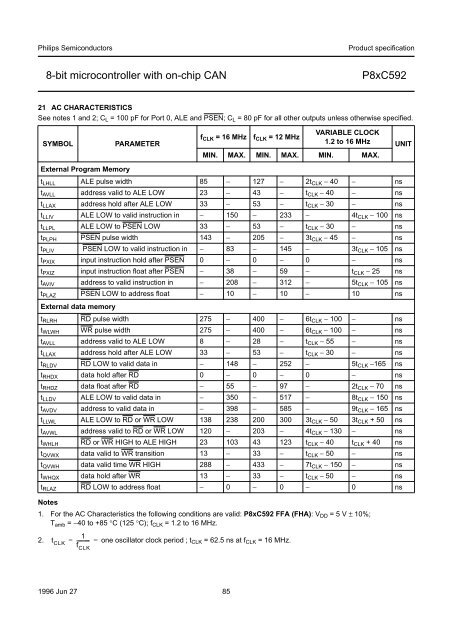

8-bit microcontroller with on-chip CAN P8xC592<br />

21 AC CHARACTERISTICS<br />

See notes 1 and 2; CL = 100 pF for Port 0, ALE and PSEN; CL = 80 pF for all other outputs unless otherwise specified.<br />

SYMBOL PARAMETER<br />

External Program Memory<br />

Notes<br />

1. For the AC Characteristics the following conditions are valid: P8xC592 FFA (FHA): VDD =5V±10%;<br />

Tamb = −40 to +85 °C (125 °C); fCLK = 1.2 to 16 MHz.<br />

2. =<br />

1<br />

---------- =<br />

one oscillator clock period ; tCLK = 62.5 ns at fCLK = 16 MHz.<br />

1996 Jun 27 85<br />

fCLK = 16 MHz fCLK = 12 MHz<br />

VARIABLE CLOCK<br />

1.2 to 16 MHz UNIT<br />

MIN. MAX. MIN. MAX. MIN. MAX.<br />

tLHLL ALE pulse width 85 − 127 − 2tCLK − 40 − ns<br />

tAVLL address valid to ALE LOW 23 − 43 − tCLK − 40 − ns<br />

tLLAX address hold after ALE LOW 33 − 53 − tCLK − 30 − ns<br />

tLLIV ALE LOW to valid instruction in − 150 − 233 − 4tCLK − 100 ns<br />

tLLPL ALE LOW to PSEN LOW 33 − 53 − tCLK − 30 − ns<br />

tPLPH PSEN pulse width 143 − 205 − 3tCLK − 45 − ns<br />

tPLIV PSEN LOW to valid instruction in − 83 − 145 − 3tCLK − 105 ns<br />

tPXIX input instruction hold after PSEN 0 − 0 − 0 − ns<br />

tPXIZ input instruction float after PSEN − 38 − 59 − tCLK − 25 ns<br />

tAVIV address to valid instruction in − 208 − 312 − 5tCLK − 105 ns<br />

tPLAZ PSEN LOW to address float − 10 − 10 − 10 ns<br />

External data memory<br />

tRLRH RD pulse width 275 − 400 − 6tCLK − 100 − ns<br />

tWLWH WR pulse width 275 − 400 − 6tCLK − 100 − ns<br />

tAVLL address valid to ALE LOW 8 − 28 − tCLK − 55 − ns<br />

tLLAX address hold after ALE LOW 33 − 53 − tCLK − 30 − ns<br />

tRLDV RD LOW to valid data in − 148 − 252 − 5tCLK −165 ns<br />

tRHDX data hold after RD 0 − 0 − 0 − ns<br />

tRHDZ data float after RD − 55 − 97 − 2tCLK − 70 ns<br />

tLLDV ALE LOW to valid data in − 350 − 517 − 8tCLK − 150 ns<br />

tAVDV address to valid data in − 398 − 585 − 9tCLK − 165 ns<br />

tLLWL ALE LOW to RD or WR LOW 138 238 200 300 3tCLK − 50 3tCLK +50 ns<br />

tAVWL address valid to RD or WR LOW 120 − 203 − 4tCLK − 130 − ns<br />

tWHLH RD or WR HIGH to ALE HIGH 23 103 43 123 tCLK − 40 tCLK +40 ns<br />

tQVWX data valid to WR transition 13 − 33 − tCLK − 50 − ns<br />

tQVWH data valid time WR HIGH 288 − 433 − 7tCLK − 150 − ns<br />

tWHQX data hold after WR 13 − 33 − tCLK − 50 − ns<br />

tRLAZ RD LOW to address float − 0 − 0 − 0 ns<br />

t CLK<br />

f CLK