TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

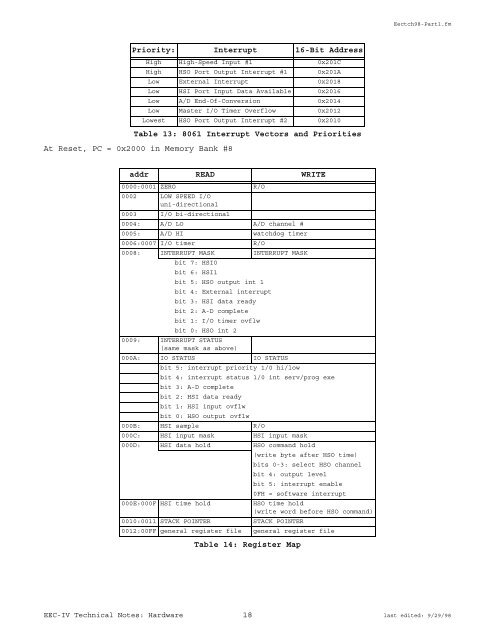

Priority: Interrupt 16-Bit Address<br />

At Reset, PC = 0x2000 in Memory Bank #8<br />

High High-Speed Input #1 0x201C<br />

High HSO Port Output Interrupt #1 0x201A<br />

Low External Interrupt 0x2018<br />

Low HSI Port Input Data Available 0x2016<br />

Low A/D End-Of-Conversion 0x2014<br />

Low Master I/O Timer Overflow 0x2012<br />

Lowest HSO Port Output Interrupt #2 0x2010<br />

Table 13: 8061 Interrupt Vectors and Priorities<br />

addr READ WRITE<br />

0000:0001 ZERO R/O<br />

0002 LOW SPEED I/O<br />

uni-directional<br />

0003 I/O bi-directional<br />

0004: A/D LO A/D channel #<br />

0005: A/D HI watchdog timer<br />

0006:0007 I/O timer R/O<br />

0008: INTERRUPT MASK<br />

bit 7: HSI0<br />

bit 6: HSI1<br />

INTERRUPT MASK<br />

0009:<br />

bit 5: HSO output int 1<br />

bit 4: External interrupt<br />

bit 3: HSI data ready<br />

bit 2: A-D complete<br />

bit 1: I/O timer ovflw<br />

bit 0: HSO int 2<br />

INTERRUPT STATUS<br />

(same mask as above)<br />

000A: IO STATUS IO STATUS<br />

bit 5: interrupt priority 1/0 hi/low<br />

bit 4: interrupt status 1/0 int serv/prog exe<br />

bit 3: A-D complete<br />

bit 2: HSI data ready<br />

bit 1: HSI input ovflw<br />

bit 0: HSO output ovflw<br />

000B: HSI sample R/O<br />

000C: HSI input mask HSI input mask<br />

000D: HSI data hold HSO command hold<br />

(write byte after HSO time)<br />

bits 0-3: select HSO channel<br />

bit 4: output level<br />

bit 5: interrupt enable<br />

0FH = software interrupt<br />

000E:000F HSI time hold HSO time hold<br />

(write word before HSO command)<br />

0010:0011 STACK POINTER STACK POINTER<br />

0012:00FF general register file general register file<br />

Table 14: Register Map<br />

Eectch98-Part1.fm<br />

<strong>EEC</strong>-<strong>IV</strong> Technical Notes: Hardware 18 last edited: 9/29/98