TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Eectch98-Part4.fm<br />

put the next byte of data on the MB bus (if the MEMORY is driving the MB Bus).<br />

• IT can be thought of as the "Instruction Transfer" line. What it really does is<br />

choose whether the 8061 is accessing the SPC (if IT is high) or the DAR (if IT is<br />

low).<br />

• DI can be thought of as the "Direction Indicator" for the MB bus. If DI is high,<br />

then memory has the rights to the MB bus. If DI is low then the processor has<br />

the rights to the MB Bus.<br />

(DAR - data address registerSPC - slave program counter)<br />

An example would be reading a memory location using the DAR. In a "NORMAL" memory<br />

system (one with an address and a data bus) if we were going to read a memory location<br />

we would:<br />

1. Place the address on the address bus.<br />

2. Output the memory "read enable" to "enable" the memory chip.<br />

3. Read the information off of the "DATA" bus.<br />

On an <strong>EEC</strong> MB bus system we would follow the same pattern:<br />

1. Write the DAR (give the memory’s address register the address).<br />

a. Lower DI - this gives the rights to the MB bus to the 8061.<br />

b. Lower IT - this tells the memory system we’re using the DAR, not the SPC.<br />

c. Drive MB bus with low 8 bits of the address.<br />

d. Bring /STB low for a cycle - tells memory to latch the low address.<br />

e. Drive MB bus with high 8 bits of the address.<br />

f. Bring /STB low for a cycle - tells memory to latch the high address.<br />

At this point the memory system has our "ADDRESS" that we want to read.<br />

7. Raise DI - This tells the memory system that it has rights to the MB bus.<br />

This is the same as sending a "memory enable" or "memory read" signal.<br />

8. Read the data off of the MB bus.<br />

a. Read the low byte off the MB bus.<br />

b. Bring /STB low for a cycle.<br />

c. Read the high byte off the MB bus.<br />

One note: The <strong>EEC</strong> uses a "16 bit" memory, so an address didn’t have to be supplied<br />

for the 2nd 8 bits of data, but when using the DAR you must begin reading from an<br />

even address, and the odd address will be available the following /STB. If you use<br />

the SPC to read the memory, you can (in theory) just keep strobing and read the<br />

entire chip. I’ve found that I can only "strobe" about 300 bytes of data out of the<br />

memory before it "clams up". Your results may vary.<br />

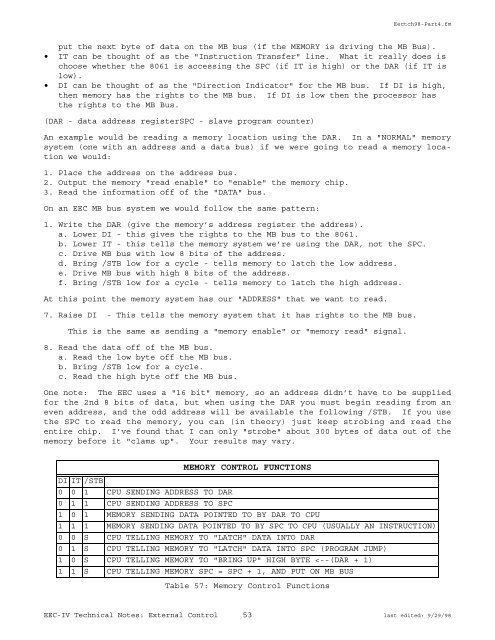

MEMORY C<strong>ON</strong>TROL FUNCTI<strong>ON</strong>S<br />

DI IT /STB<br />

0 0 1 CPU SENDING ADDRESS TO DAR<br />

0 1 1 CPU SENDING ADDRESS TO SPC<br />

1 0 1 MEMORY SENDING DATA POINTED TO BY DAR TO CPU<br />

1 1 1 MEMORY SENDING DATA POINTED TO BY SPC TO CPU (USUALLY AN INSTRUCTI<strong>ON</strong>)<br />

0 0 S CPU TELLING MEMORY TO "LATCH" DATA INTO DAR<br />

0 1 S CPU TELLING MEMORY TO "LATCH" DATA INTO SPC (PROGRAM JUMP)<br />

1 0 S CPU TELLING MEMORY TO "BRING UP" HIGH BYTE