TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

TECHNICAL NOTES ON THE EEC-IV MCU - Auto diagnostics

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

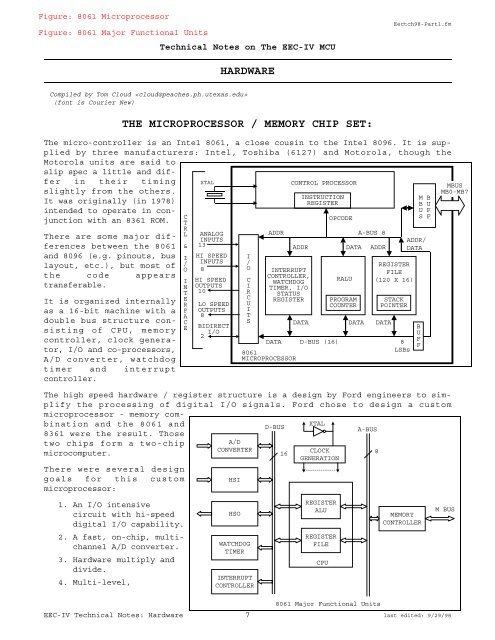

Figure: 8061 Microprocessor<br />

Figure: 8061 Major Functional Units<br />

Technical Notes on The <strong>EEC</strong>-<strong>IV</strong> <strong>MCU</strong><br />

HARDWARE<br />

Compiled by Tom Cloud <br />

(font is Courier New)<br />

<strong>THE</strong> MICROPROCESSOR / MEMORY CHIP SET:<br />

Eectch98-Part1.fm<br />

The micro-controller is an Intel 8061, a close cousin to the Intel 8096. It is supplied<br />

by three manufacturers: Intel, Toshiba (6127) and Motorola, though the<br />

Motorola units are said to<br />

slip spec a little and dif-<br />

fer in their timing<br />

slightly from the others.<br />

It was originally (in 1978)<br />

intended to operate in conjunction<br />

with an 8361 ROM.<br />

There are some major differences<br />

between the 8061<br />

and 8096 (e.g. pinouts, bus<br />

layout, etc.), but most of<br />

the code appears<br />

transferable.<br />

It is organized internally<br />

as a 16-bit machine with a<br />

double bus structure consisting<br />

of CPU, memory<br />

controller, clock generator,<br />

I/O and co-processors,<br />

A/D converter, watchdog<br />

timer and interrupt<br />

controller.<br />

The high speed hardware / register structure is a design by Ford engineers to simplify<br />

the processing of digital I/O signals. Ford chose to design a custom<br />

microprocessor - memory combination<br />

and the 8061 and<br />

8361 were the result. Those<br />

two chips form a two-chip<br />

microcomputer.<br />

There were several design<br />

goals for this custom<br />

microprocessor:<br />

C<br />

T<br />

R<br />

L<br />

&<br />

I<br />

/<br />

O<br />

I<br />

N<br />

T<br />

E<br />

R<br />

F<br />

A<br />

C<br />

E<br />

1. An I/O intensive<br />

circuit with hi-speed<br />

digital I/O capability.<br />

2. A fast, on-chip, multichannel<br />

A/D converter.<br />

3. Hardware multiply and<br />

divide.<br />

4. Multi-level,<br />

XTAL<br />

ANALOG<br />

INPUTS<br />

13<br />

HI SPEED<br />

INPUTS<br />

8<br />

HI SPEED<br />

OUTPUTS<br />

10<br />

LO SPEED<br />

OUTPUTS<br />

8<br />

BIDIRECT<br />

I/O<br />

2<br />

A/D<br />

C<strong>ON</strong>VERTER<br />

HSI<br />

HSO<br />

I<br />

/<br />

O<br />

C<br />

I<br />

R<br />

C<br />

U<br />

I<br />

T<br />

S<br />

WATCHDOG<br />

TIMER<br />

INTERRUPT<br />

C<strong>ON</strong>TROLLER<br />

INTERRUPT<br />

C<strong>ON</strong>TROLLER,<br />

WATCHDOG<br />

TIMER, I/O<br />

STATUS<br />

REGISTER<br />

XTAL<br />

D-BUS A-BUS<br />

REGISTER<br />

ALU<br />

REGISTER<br />

FILE<br />

8061 Major Functional Units<br />

MEMORY<br />

C<strong>ON</strong>TROLLER<br />

<strong>EEC</strong>-<strong>IV</strong> Technical Notes: Hardware 7 last edited: 9/29/98<br />

16<br />

C<strong>ON</strong>TROL PROCESSOR<br />

INSTRUCTI<strong>ON</strong><br />

REGISTER<br />

ADDR A-BUS 8<br />

ADDR DATA<br />

DATA<br />

DATA D-BUS (16)<br />

8061<br />

MICROPROCESSOR<br />

CLOCK<br />

GENERATI<strong>ON</strong><br />

CPU<br />

OPCODE<br />

RALU<br />

PROGRAM<br />

COUNTER<br />

ADDR<br />

DATA DATA<br />

REGISTER<br />

FILE<br />

(120 X 16)<br />

8<br />

STACK<br />

POINTER<br />

8<br />

LSBs<br />

M B<br />

B U<br />

U F<br />

S F<br />

ADDR/<br />

DATA<br />

B<br />

U<br />

F<br />

F<br />

MBUS<br />

MB0-MB7<br />

M BUS