Video and Image Processing Up Conversion Example Design

Video and Image Processing Up Conversion Example Design

Video and Image Processing Up Conversion Example Design

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Video</strong> <strong>and</strong> <strong>Image</strong> <strong>Processing</strong> <strong>Up</strong> <strong>Conversion</strong> <strong>Example</strong> <strong>Design</strong><br />

1 The DSP Builder up conversion subsystem could be built<br />

directly in SOPC Builder by wiring up MegaCore function<br />

blocks from the list of <strong>Video</strong> <strong>and</strong> <strong>Image</strong> <strong>Processing</strong> modules.<br />

However, DSP Builder is required to simulate the data path <strong>and</strong><br />

perform early design verification.<br />

The custom hardware components: example_design_controller,<br />

ntsc_composite_input, openCores_I2c_master, <strong>and</strong> vga_output appear in<br />

the <strong>Video</strong> IP <strong>Example</strong> <strong>Design</strong> module list. The Frame Buffer BETA<br />

MegaCore function block is available in the list of <strong>Video</strong> <strong>and</strong> <strong>Image</strong><br />

<strong>Processing</strong> modules. These components are described in the “Functional<br />

Description” on page 8.<br />

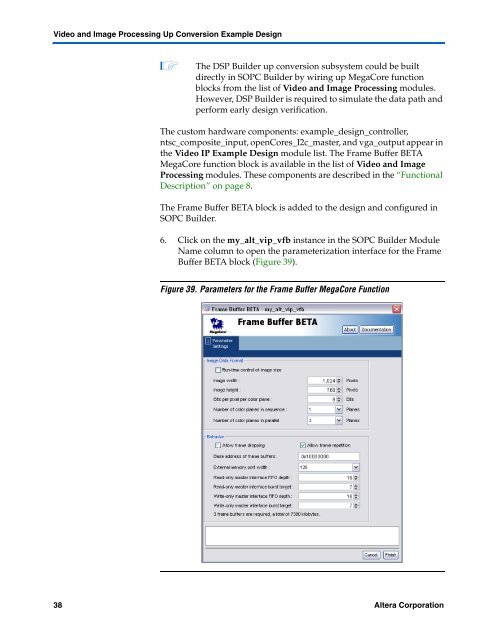

The Frame Buffer BETA block is added to the design <strong>and</strong> configured in<br />

SOPC Builder.<br />

6. Click on the my_alt_vip_vfb instance in the SOPC Builder Module<br />

Name column to open the parameterization interface for the Frame<br />

Buffer BETA block (Figure 39).<br />

Figure 39. Parameters for the Frame Buffer MegaCore Function<br />

38 Altera Corporation<br />

Preliminary