Video and Image Processing Up Conversion Example Design

Video and Image Processing Up Conversion Example Design

Video and Image Processing Up Conversion Example Design

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Video</strong> <strong>and</strong> <strong>Image</strong> <strong>Processing</strong> <strong>Up</strong> <strong>Conversion</strong> <strong>Example</strong> <strong>Design</strong><br />

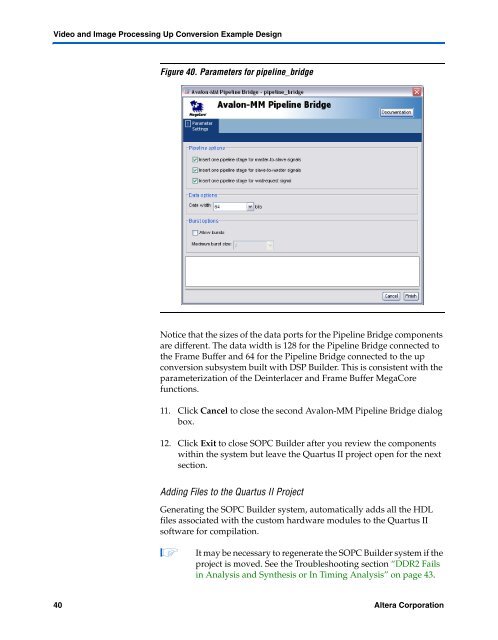

Figure 40. Parameters for pipeline_bridge<br />

Notice that the sizes of the data ports for the Pipeline Bridge components<br />

are different. The data width is 128 for the Pipeline Bridge connected to<br />

the Frame Buffer <strong>and</strong> 64 for the Pipeline Bridge connected to the up<br />

conversion subsystem built with DSP Builder. This is consistent with the<br />

parameterization of the Deinterlacer <strong>and</strong> Frame Buffer MegaCore<br />

functions.<br />

11. Click Cancel to close the second Avalon-MM Pipeline Bridge dialog<br />

box.<br />

12. Click Exit to close SOPC Builder after you review the components<br />

within the system but leave the Quartus II project open for the next<br />

section.<br />

Adding Files to the Quartus II Project<br />

Generating the SOPC Builder system, automatically adds all the HDL<br />

files associated with the custom hardware modules to the Quartus II<br />

software for compilation.<br />

1 It may be necessary to regenerate the SOPC Builder system if the<br />

project is moved. See the Troubleshooting section “DDR2 Fails<br />

in Analysis <strong>and</strong> Synthesis or In Timing Analysis” on page 43.<br />

40 Altera Corporation<br />

Preliminary