EO18-12003 - toshiba tec europe

EO18-12003 - toshiba tec europe

EO18-12003 - toshiba tec europe

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

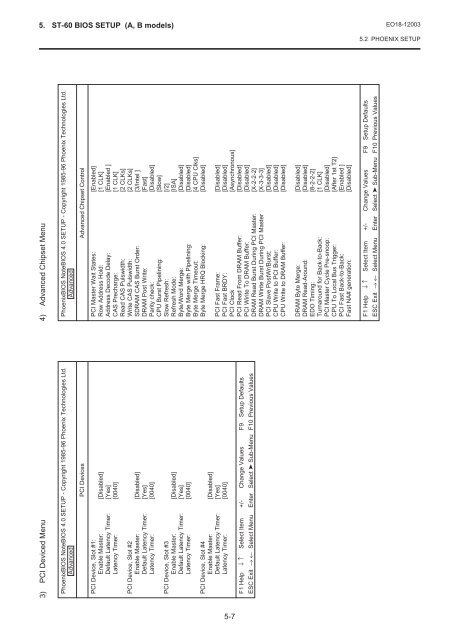

5. ST-60 BIOS SETUP (A, B models) <strong>EO18</strong>-<strong>12003</strong>5.2 PHOENIX SETUP3) PCI Deviced Menu 4) Advanced Chipset MenuPhoenixBIOS NoteBIOS 4.0 SETUP - Copyright 1985-96 Phoenix Technologies Ltd.AdvancedPhoenixBIOS NoteBIOS 4.0 SETUP - Copyright 1985-96 Phoenix Technologies Ltd.AdvancedPCI DevicesAdvanced Chipset ControlPCI Device, Slot #1:Enable Master: [Disabled]Default Latency Timer: [Yes]Latency Timer: [0040]PCI Device, Slot #2Enable Master: [Disabled]Default Latency Timer: [Yes]Latency Timer: [0040]PCI Device, Slot #3Enable Master: [Disabled]Default Latency Timer: [Yes]Latency Timer: [0040]PCI Device, Slot #4Enable Master: [Disabled]Default Latency Timer: [Yes]Latency Timer: [0040]F1 Help ↓ ↑ Select Item +/- Change Values F9 Setup DefaultsESC Exit → ← Select Menu Enter Select ➤ Sub-Menu F10 Previous ValuesPCI Master Wait States: [Enabled]Row Address Hold: [1 CLK]Address Decode Delay: [Enabled ]CAS Precharge: [1 CLK]Read CAS Pulswidth: [2 CLKs]Write CAS Pulswidth: [2 CLKs]SDRAM CAS Burst Order: [3/Intel ]DRAM Post Write: [Fast]Parity check: [Disabled]CPU Burst Pipelining: [Slow]Slow Refresh: [/2]Refresh Mode: [ISA]Byte/Word Merge: [Disabled]Byte Merge with Pipelining: [Disabled]Byte Merge Timeout: [4 CPU Clks]Byte Merge HRQ Blocking: [Disabled]PCI Fast Frame: [Disabled]PCI Fast BRDY: [Disabled]PCI Clock [Asynchronous]PCI Read From DRAM Buffer: [Disabled]PCI Wirite To DRAM Buffer: [Disabled]DRAM Read Burst During PCI Master: [X-2-2-2]DRAM Wirite Burst During PCI Master [X-3-3-3]PCI Slave PostWr/Burst: [Disabled]CPU Write to PCI Buffer: [Disabled]CPU Write to DRAM Buffer: [Disabled]DRAM Byte Merge: [Disabled]DRAM Read-Around: [Disabled]EDO Timing: [8-2-2-2]Turnaround for Back-to-Back: [1 CLK]PCI Master Cycle Pre-snoop: [Disabled]CPU To Local Bus Trigger: [After 1st T2]PCI Fast Back-to-Back: [Enabled ]Fast NA# generation: [Disabled]F1 Help ↓ ↑ Select Item +/- Change Values F9 Setup DefaultsESC Exit → ← Select Menu Enter Select ➤ Sub-Menu F10 Previous Values5-7