hbrisc2 - Microelectronics

hbrisc2 - Microelectronics

hbrisc2 - Microelectronics

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

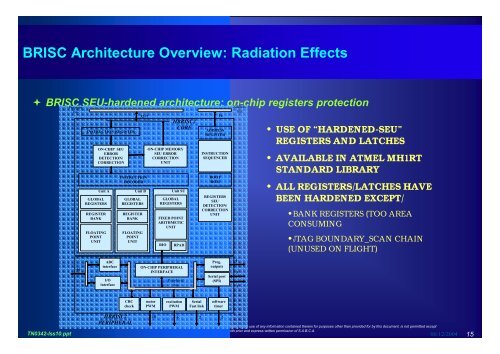

BRISC Architecture Overview: Radiation Effects BRISC SEU-hardened architecture: on-chip registers protectionProgrambusINSTRUCTION REGISTERON-CHIP SEUERRORDETECTION/CORRECTIONUNITUnit AGLOBALREGISTERSREGISTERBANKFLOATINGPOINTUNIT 32+7INSTRUCTIONDECODERUnit BGLOBALREGISTERSREGISTERBANKFLOATINGPOINTUNITON-CHIP MEMORYSEU ERRORCORRECTIONUNITGLOBALREGISTERSFIXED POINTARITHMETICUNITRIOHBRISC2COREUnit SURPAD 16ADDRESSREGISTERINSTRUCTIONSEQUENCERBOOTROMREGISTERSSEUDETECTION/CORRECTIONUNITAddressbus• USE OF “HARDENED-SEU”REGISTERS AND LATCHES• AVAILABLE IN ATMEL MH1RTSTANDARD LIBRARY• ALL REGISTERS/LATCHES HAVEBEEN HARDENED EXCEPT/•BANK REGISTERS (TOO AREACONSUMING•JTAG BOUNDARY_SCAN CHAIN(UNUSED ON FLIGHT)46/ADCinterfaceI/OinterfaceON-CHIP PERIPHERALINTERFACEPeripheralbusProg.outputsSerial port(SPI)4/3//1CRCcheckmotorPWMexcitationPWMSerialFast linksoftwaretimerTN0342-Iss10.pptHBRISC2PERIPHERAL 18 6 2 2All right reserved: Disclosure to third parties of this document or any part thereof, or the use of any information contained therein for purposes other than provided for by this document, is not permitted exceptwith prior and express written permission of S.A.B.C.A.06/12/200415