Simulation of Third Generation CDMA Systems - Virginia Tech

Simulation of Third Generation CDMA Systems - Virginia Tech

Simulation of Third Generation CDMA Systems - Virginia Tech

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

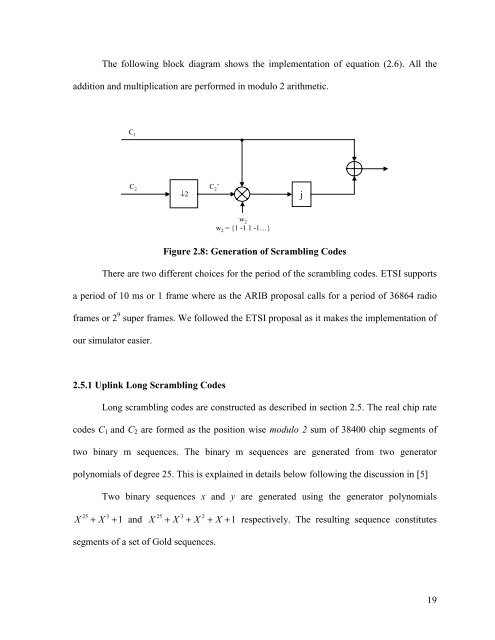

The following block diagram shows the implementation <strong>of</strong> equation (2.6). All theaddition and multiplication are performed in modulo 2 arithmetic.C 1C 2↓2C 2 ’jw 2w 2 = {1 -1 1 -1…}Figure 2.8: <strong>Generation</strong> <strong>of</strong> Scrambling CodesThere are two different choices for the period <strong>of</strong> the scrambling codes. ETSI supportsa period <strong>of</strong> 10 ms or 1 frame where as the ARIB proposal calls for a period <strong>of</strong> 36864 radi<strong>of</strong>rames or 2 9 super frames. We followed the ETSI proposal as it makes the implementation <strong>of</strong>our simulator easier.2.5.1 Uplink Long Scrambling CodesLong scrambling codes are constructed as described in section 2.5. The real chip ratecodes C 1 and C 2 are formed as the position wise modulo 2 sum <strong>of</strong> 38400 chip segments <strong>of</strong>two binary m sequences. The binary m sequences are generated from two generatorpolynomials <strong>of</strong> degree 25. This is explained in details below following the discussion in [5]Two binary sequences x and y are generated using the generator polynomialsX25 3 2+ X + 1 and X + X + X + X + 1 respectively. The resulting sequence constitutes25 3segments <strong>of</strong> a set <strong>of</strong> Gold sequences.19