Simulation of Third Generation CDMA Systems - Virginia Tech

Simulation of Third Generation CDMA Systems - Virginia Tech

Simulation of Third Generation CDMA Systems - Virginia Tech

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

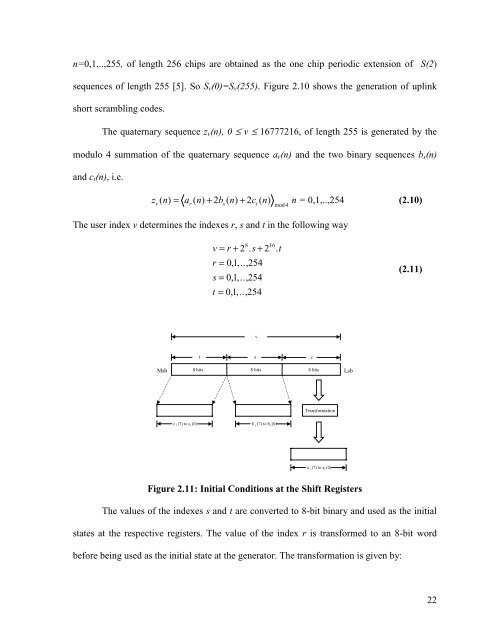

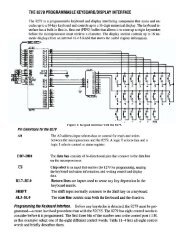

n=0,1,..,255, <strong>of</strong> length 256 chips are obtained as the one chip periodic extension <strong>of</strong> S(2)sequences <strong>of</strong> length 255 [5]. So S v (0)=S v (255). Figure 2.10 shows the generation <strong>of</strong> uplinkshort scrambling codes.The quaternary sequence z v (n), 0 ≤ v ≤ 16777216, <strong>of</strong> length 255 is generated by themodulo 4 summation <strong>of</strong> the quaternary sequence a r (n) and the two binary sequences b s (n)and c t (n), i.e.zv( n) = ar( n) + 2bs( n) + 2ct( n) mod 4n = 0,1,..,254 (2.10)The user index v determines the indexes r, s and t in the following way8 16v = r+ 2 . s+2 . tr = 0,,..,1 254s = 0,,..,1 254t = 0,,..,1 254(2.11)vtsrMsb8 bits 8 bits 8 bitsLsbTransformationc t (7) to c t (0) b s (7) to b s (0)a r (7) to a r (0)Figure 2.11: Initial Conditions at the Shift RegistersThe values <strong>of</strong> the indexes s and t are converted to 8-bit binary and used as the initialstates at the respective registers. The value <strong>of</strong> the index r is transformed to an 8-bit wordbefore being used as the initial state at the generator. The transformation is given by:22