reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

6.1. FELDEFFEKT-TRANSISTOREN<br />

Feldeffekt-Transistoren des n-Kanal-Typs bestehen aus stark n-dotierten Bereichen 1<br />

für Quelle und Abfluss und e<strong>in</strong>em p-dotierten Substrat. Das Siliziumdioxid unter dem<br />

Gate-Kontakt stellt e<strong>in</strong>en Isolator dar. Bei positiver Gatespannung bildet sich zwischen<br />

Gate und Substrat e<strong>in</strong> elektrisches Feld, so dass sich Elektronen unter dem Gate sam-<br />

meln. Dadurch wird e<strong>in</strong> Stromfluss zwischen Source und Dra<strong>in</strong> möglich.<br />

Beim p-Kanaltyp dienen positiv geladene Defektelektronen modellhaft als Ladungsträ-<br />

ger. Um e<strong>in</strong>en leitenden Defektelektronen-Kanal zu erzeugen, muss die Gate-Spannung<br />

null se<strong>in</strong>. Dadurch sammeln sich Defektelektronen unter dem Gate. Source und Dra<strong>in</strong><br />

e<strong>in</strong>es p-Kanal-FETs s<strong>in</strong>d stark p-dotiert und dessen Substrat ist n-dotiert, d.h. genau an-<br />

ders herum wie beim n-Kanal-Typ. Um beide Transistortypen auf e<strong>in</strong>em geme<strong>in</strong>samen<br />

Substrat betreiben zu können, werden bei der Chip-Herstellung sogenannte Wannen<br />

erzeugt.<br />

VDD<br />

VSS<br />

Dra<strong>in</strong><br />

Gate Source<br />

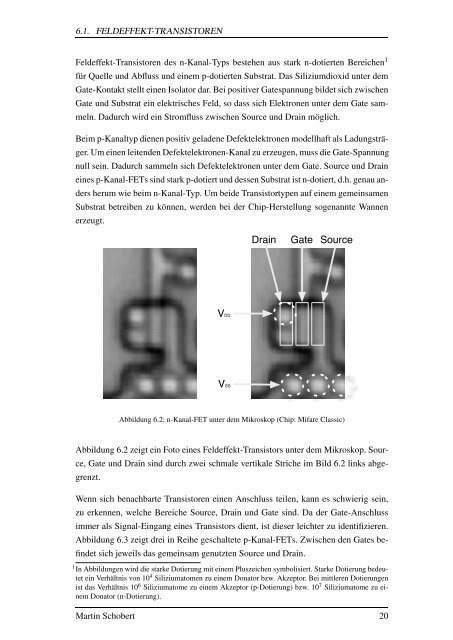

Abbildung 6.2: n-Kanal-FET unter dem Mikroskop (Chip: Mifare Classic)<br />

Abbildung 6.2 zeigt e<strong>in</strong> Foto e<strong>in</strong>es Feldeffekt-Transistors unter dem Mikroskop. Sour-<br />

ce, Gate und Dra<strong>in</strong> s<strong>in</strong>d durch zwei schmale vertikale Striche im Bild 6.2 l<strong>in</strong>ks abge-<br />

grenzt.<br />

Wenn sich benachbarte Transistoren e<strong>in</strong>en Anschluss teilen, kann es schwierig se<strong>in</strong>,<br />

zu erkennen, welche Bereiche Source, Dra<strong>in</strong> und Gate s<strong>in</strong>d. Da der Gate-Anschluss<br />

immer als Signal-E<strong>in</strong>gang e<strong>in</strong>es Transistors dient, ist dieser leichter zu identifizieren.<br />

Abbildung 6.3 zeigt drei <strong>in</strong> Reihe geschaltete p-Kanal-FETs. Zwischen den Gates be-<br />

f<strong>in</strong>det sich jeweils das geme<strong>in</strong>sam genutzten Source und Dra<strong>in</strong>.<br />

1 In Abbildungen wird die starke Dotierung mit e<strong>in</strong>em Pluszeichen symbolisiert. Starke Dotierung bedeutet<br />

e<strong>in</strong> Verhältnis <strong>von</strong> 10 4 Siliziumatomen zu e<strong>in</strong>em Donator bzw. Akzeptor. Bei mittleren Dotierungen<br />

ist das Verhältnis 10 6 Siliziumatome zu e<strong>in</strong>em Akzeptor (p-Dotierung) bzw. 10 7 Siliziumatome zu e<strong>in</strong>em<br />

Donator (n-Dotierung).<br />

Mart<strong>in</strong> Schobert 20