reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

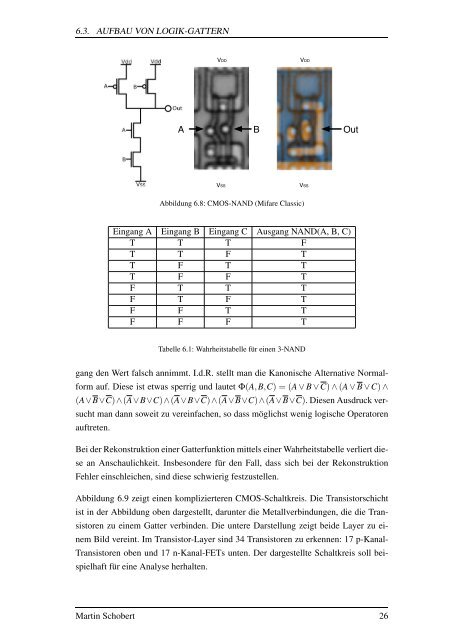

6.3. AUFBAU VON LOGIK-GATTERN<br />

VDD<br />

A B<br />

VSS<br />

Abbildung 6.8: CMOS-NAND (Mifare Classic)<br />

E<strong>in</strong>gang A E<strong>in</strong>gang B E<strong>in</strong>gang C Ausgang NAND(A, B, C)<br />

T T T F<br />

T T F T<br />

T F T T<br />

T F F T<br />

F T T T<br />

F T F T<br />

F F T T<br />

F F F T<br />

Tabelle 6.1: Wahrheitstabelle für e<strong>in</strong>en 3-NAND<br />

gang den Wert falsch annimmt. I.d.R. stellt man die Kanonische Alternative Normal-<br />

form auf. Diese ist etwas sperrig und lautet Φ(A,B,C) = (A ∨ B ∨C) ∧ (A ∨ B ∨C) ∧<br />

(A∨B∨C)∧(A∨B∨C)∧(A∨B∨C)∧(A∨B∨C)∧(A∨B∨C). Diesen Ausdruck ver-<br />

sucht man dann soweit zu vere<strong>in</strong>fachen, so dass möglichst wenig logische Operatoren<br />

auftreten.<br />

Bei der Rekonstruktion e<strong>in</strong>er Gatterfunktion mittels e<strong>in</strong>er Wahrheitstabelle verliert die-<br />

se an Anschaulichkeit. Insbesondere für den Fall, dass sich bei der Rekonstruktion<br />

Fehler e<strong>in</strong>schleichen, s<strong>in</strong>d diese schwierig festzustellen.<br />

Abbildung 6.9 zeigt e<strong>in</strong>en komplizierteren CMOS-Schaltkreis. Die Transistorschicht<br />

ist <strong>in</strong> der Abbildung oben dargestellt, darunter die Metallverb<strong>in</strong>dungen, die die Tran-<br />

sistoren zu e<strong>in</strong>em Gatter verb<strong>in</strong>den. Die untere Darstellung zeigt beide Layer zu ei-<br />

nem Bild vere<strong>in</strong>t. Im Transistor-Layer s<strong>in</strong>d 34 Transistoren zu erkennen: 17 p-Kanal-<br />

Transistoren oben und 17 n-Kanal-FETs unten. Der dargestellte Schaltkreis soll bei-<br />

spielhaft für e<strong>in</strong>e Analyse herhalten.<br />

Mart<strong>in</strong> Schobert 26<br />

VDD<br />

VSS<br />

Out