reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

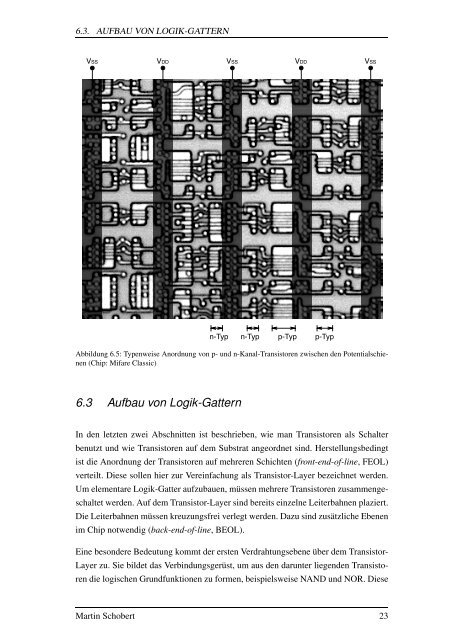

6.3. AUFBAU VON LOGIK-GATTERN<br />

VSS<br />

VDD VSS VDD VSS<br />

n-Typ<br />

n-Typ<br />

p-Typ p-Typ<br />

Abbildung 6.5: Typenweise Anordnung <strong>von</strong> p- und n-Kanal-Transistoren zwischen den Potentialschienen<br />

(Chip: Mifare Classic)<br />

6.3 Aufbau <strong>von</strong> Logik-Gattern<br />

In den letzten zwei Abschnitten ist beschrieben, wie man Transistoren als Schalter<br />

benutzt und wie Transistoren auf dem Substrat angeordnet s<strong>in</strong>d. Herstellungsbed<strong>in</strong>gt<br />

ist die Anordnung der Transistoren auf mehreren Schichten (front-end-of-l<strong>in</strong>e, FEOL)<br />

verteilt. Diese sollen hier zur Vere<strong>in</strong>fachung als Transistor-Layer bezeichnet werden.<br />

Um elementare Logik-Gatter aufzubauen, müssen mehrere Transistoren zusammenge-<br />

schaltet werden. Auf dem Transistor-Layer s<strong>in</strong>d bereits e<strong>in</strong>zelne Leiterbahnen plaziert.<br />

Die Leiterbahnen müssen kreuzungsfrei verlegt werden. Dazu s<strong>in</strong>d zusätzliche Ebenen<br />

im Chip notwendig (back-end-of-l<strong>in</strong>e, BEOL).<br />

E<strong>in</strong>e besondere Bedeutung kommt der ersten Verdrahtungsebene über dem Transistor-<br />

Layer zu. Sie bildet das Verb<strong>in</strong>dungsgerüst, um aus den darunter liegenden Transisto-<br />

ren die logischen Grundfunktionen zu formen, beispielsweise NAND und NOR. Diese<br />

Mart<strong>in</strong> Schobert 23