reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

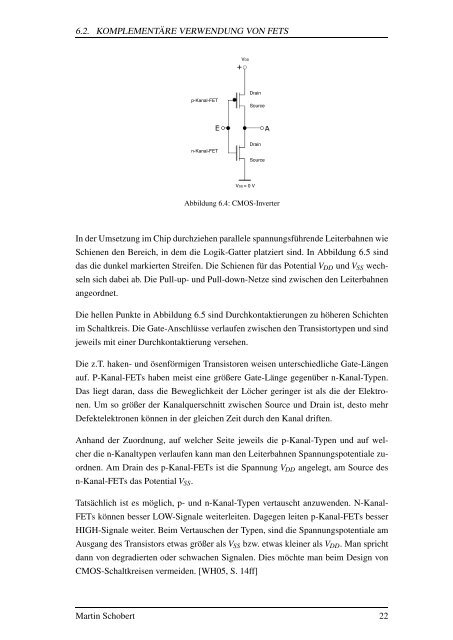

6.2. KOMPLEMENTÄRE VERWENDUNG VON FETS<br />

p-Kanal-FET<br />

n-Kanal-FET<br />

VDD<br />

VSS = 0 V<br />

Dra<strong>in</strong><br />

Source<br />

Dra<strong>in</strong><br />

Source<br />

Abbildung 6.4: CMOS-Inverter<br />

In der Umsetzung im Chip durchziehen parallele spannungsführende Leiterbahnen wie<br />

Schienen den Bereich, <strong>in</strong> dem die Logik-Gatter platziert s<strong>in</strong>d. In Abbildung 6.5 s<strong>in</strong>d<br />

das die dunkel markierten Streifen. Die Schienen für das Potential VDD und VSS wech-<br />

seln sich dabei ab. Die Pull-up- und Pull-down-Netze s<strong>in</strong>d zwischen den Leiterbahnen<br />

angeordnet.<br />

Die hellen Punkte <strong>in</strong> Abbildung 6.5 s<strong>in</strong>d Durchkontaktierungen zu höheren Schichten<br />

im Schaltkreis. Die Gate-Anschlüsse verlaufen zwischen den Transistortypen und s<strong>in</strong>d<br />

jeweils mit e<strong>in</strong>er Durchkontaktierung versehen.<br />

Die z.T. haken- und ösenförmigen Transistoren weisen unterschiedliche Gate-Längen<br />

auf. P-Kanal-FETs haben meist e<strong>in</strong>e größere Gate-Länge gegenüber n-Kanal-Typen.<br />

Das liegt daran, dass die Beweglichkeit der Löcher ger<strong>in</strong>ger ist als die der Elektro-<br />

nen. Um so größer der Kanalquerschnitt zwischen Source und Dra<strong>in</strong> ist, desto mehr<br />

Defektelektronen können <strong>in</strong> der gleichen Zeit durch den Kanal driften.<br />

Anhand der Zuordnung, auf welcher Seite jeweils die p-Kanal-Typen und auf wel-<br />

cher die n-Kanaltypen verlaufen kann man den Leiterbahnen Spannungspotentiale zu-<br />

ordnen. Am Dra<strong>in</strong> des p-Kanal-FETs ist die Spannung VDD angelegt, am Source des<br />

n-Kanal-FETs das Potential VSS.<br />

Tatsächlich ist es möglich, p- und n-Kanal-Typen vertauscht anzuwenden. N-Kanal-<br />

FETs können besser LOW-Signale weiterleiten. Dagegen leiten p-Kanal-FETs besser<br />

HIGH-Signale weiter. Beim Vertauschen der Typen, s<strong>in</strong>d die Spannungspotentiale am<br />

Ausgang des Transistors etwas größer als VSS bzw. etwas kle<strong>in</strong>er als VDD. Man spricht<br />

dann <strong>von</strong> degradierten oder schwachen Signalen. Dies möchte man beim Design <strong>von</strong><br />

CMOS-Schaltkreisen vermeiden. [WH05, S. 14ff]<br />

Mart<strong>in</strong> Schobert 22