reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

6.3. AUFBAU VON LOGIK-GATTERN<br />

Intuitiver ist allerd<strong>in</strong>gs, zu versuchen, im Schaltbild Funktionsblöcke auszumachen 4 .<br />

Als H<strong>in</strong>weis auf die Abgrenzung der Funktionsblöcke können die Zuführungen der<br />

Spannungspotentiale VDD und VSS dienen. In Abbildung 6.9 kann man im Transistor-<br />

Layer erkennen, dass seriell geschaltete Transitoren <strong>in</strong> Blöcken gruppiert s<strong>in</strong>d. Diese<br />

Gruppierung spiegelt im Wesentlichen die Funktionsblöcke wieder.<br />

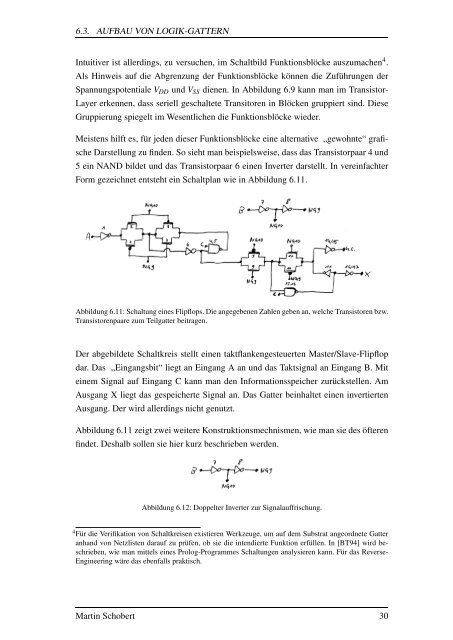

Meistens hilft es, für jeden dieser Funktionsblöcke e<strong>in</strong>e alternative „gewohnte“ grafi-<br />

sche Darstellung zu f<strong>in</strong>den. So sieht man beispielsweise, dass das Transistorpaar 4 und<br />

5 e<strong>in</strong> NAND bildet und das Transistorpaar 6 e<strong>in</strong>en Inverter darstellt. In vere<strong>in</strong>fachter<br />

Form gezeichnet entsteht e<strong>in</strong> Schaltplan wie <strong>in</strong> Abbildung 6.11.<br />

Abbildung 6.11: Schaltung e<strong>in</strong>es Flipflops. Die angegebenen Zahlen geben an, welche Transistoren bzw.<br />

Transistorenpaare zum Teilgatter beitragen.<br />

Der abgebildete Schaltkreis stellt e<strong>in</strong>en taktflankengesteuerten Master/Slave-Flipflop<br />

dar. Das „E<strong>in</strong>gangsbit“ liegt an E<strong>in</strong>gang A an und das Taktsignal an E<strong>in</strong>gang B. Mit<br />

e<strong>in</strong>em Signal auf E<strong>in</strong>gang C kann man den Informationsspeicher zurückstellen. Am<br />

Ausgang X liegt das gespeicherte Signal an. Das Gatter be<strong>in</strong>haltet e<strong>in</strong>en <strong>in</strong>vertierten<br />

Ausgang. Der wird allerd<strong>in</strong>gs nicht genutzt.<br />

Abbildung 6.11 zeigt zwei weitere Konstruktionsmechnismen, wie man sie des öfteren<br />

f<strong>in</strong>det. Deshalb sollen sie hier kurz beschrieben werden.<br />

Abbildung 6.12: Doppelter Inverter zur Signalauffrischung.<br />

4 Für die Verifikation <strong>von</strong> Schaltkreisen existieren Werkzeuge, um auf dem Substrat angeordnete Gatter<br />

anhand <strong>von</strong> Netzlisten darauf zu prüfen, ob sie die <strong>in</strong>tendierte Funktion erfüllen. In [BT94] wird beschrieben,<br />

wie man mittels e<strong>in</strong>es Prolog-Programmes Schaltungen analysieren kann. Für das Reverse-<br />

Eng<strong>in</strong>eer<strong>in</strong>g wäre das ebenfalls praktisch.<br />

Mart<strong>in</strong> Schobert 30