reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

reverse-engineering von logik-gattern in integrierten ... - Degate

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

6.2. KOMPLEMENTÄRE VERWENDUNG VON FETS<br />

Feldeffekt-Transistoren s<strong>in</strong>d symmetrisch aufgebaut. D.h. Source und Dra<strong>in</strong> könnten<br />

vertauscht werden. Zum<strong>in</strong>dest ist das bei den e<strong>in</strong>fachen FETs der Fall und bei den<br />

Chips, <strong>von</strong> denen hier Bildmaterial gezeigt wird. Die Symmetrieeigenschaft lässt es<br />

zu, dass man bei der Analyse nicht Source und Dra<strong>in</strong> explizit im Bild bennen muss.<br />

Es reicht die Vorstellung e<strong>in</strong>es Schalters, mit dem man Source und Dra<strong>in</strong> elektrisch<br />

verb<strong>in</strong>den kann.<br />

In den Schaltkreisen wird Information als Spannungs-<br />

potential gespeichert – LOW oder HIGH. Es ist des-<br />

halb nicht notwendig, sich zu überlegen, <strong>in</strong> welche<br />

Richtung der technische oder physikalische Strom fließt.<br />

Strom fließt im Gegensatz zu Bipolartransistoren haupt-<br />

sächlich nur beim Umschaltvorgang.<br />

Das Modell lautet also: Wenn das „passende“ Signal<br />

am Gate anliegt, s<strong>in</strong>d Source und Dra<strong>in</strong> elektrisch ver-<br />

bunden und der Transistor schaltet durch. Anderen-<br />

falls sperrt der Transistor.<br />

Dra<strong>in</strong><br />

Source<br />

Gate<br />

Gate<br />

Gate<br />

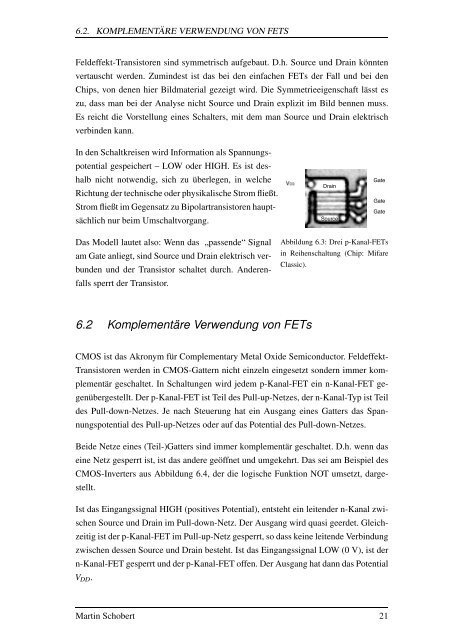

Abbildung 6.3: Drei p-Kanal-FETs<br />

<strong>in</strong> Reihenschaltung (Chip: Mifare<br />

Classic).<br />

6.2 Komplementäre Verwendung <strong>von</strong> FETs<br />

CMOS ist das Akronym für Complementary Metal Oxide Semiconductor. Feldeffekt-<br />

Transistoren werden <strong>in</strong> CMOS-Gattern nicht e<strong>in</strong>zeln e<strong>in</strong>gesetzt sondern immer kom-<br />

plementär geschaltet. In Schaltungen wird jedem p-Kanal-FET e<strong>in</strong> n-Kanal-FET ge-<br />

genübergestellt. Der p-Kanal-FET ist Teil des Pull-up-Netzes, der n-Kanal-Typ ist Teil<br />

des Pull-down-Netzes. Je nach Steuerung hat e<strong>in</strong> Ausgang e<strong>in</strong>es Gatters das Span-<br />

nungspotential des Pull-up-Netzes oder auf das Potential des Pull-down-Netzes.<br />

Beide Netze e<strong>in</strong>es (Teil-)Gatters s<strong>in</strong>d immer komplementär geschaltet. D.h. wenn das<br />

e<strong>in</strong>e Netz gesperrt ist, ist das andere geöffnet und umgekehrt. Das sei am Beispiel des<br />

CMOS-Inverters aus Abbildung 6.4, der die logische Funktion NOT umsetzt, darge-<br />

stellt.<br />

Ist das E<strong>in</strong>gangssignal HIGH (positives Potential), entsteht e<strong>in</strong> leitender n-Kanal zwi-<br />

schen Source und Dra<strong>in</strong> im Pull-down-Netz. Der Ausgang wird quasi geerdet. Gleich-<br />

zeitig ist der p-Kanal-FET im Pull-up-Netz gesperrt, so dass ke<strong>in</strong>e leitende Verb<strong>in</strong>dung<br />

zwischen dessen Source und Dra<strong>in</strong> besteht. Ist das E<strong>in</strong>gangssignal LOW (0 V), ist der<br />

n-Kanal-FET gesperrt und der p-Kanal-FET offen. Der Ausgang hat dann das Potential<br />

VDD.<br />

Mart<strong>in</strong> Schobert 21