Chapter 08 Power, Reset, and Clock Management (PRCM).pdf

Chapter 08 Power, Reset, and Clock Management (PRCM).pdf

Chapter 08 Power, Reset, and Clock Management (PRCM).pdf

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

www.ti.com <strong>Power</strong>, <strong>Reset</strong>, <strong>and</strong> <strong>Clock</strong> <strong>Management</strong><br />

Master<br />

Osc<br />

(CLK_M_OSC)<br />

ALT_CLK1<br />

ALT_CLK2<br />

TEST.CDR (via P1500)<br />

<strong>Reset</strong> default = 0<br />

0<br />

1<br />

2<br />

Per PLL<br />

(ADPLLLJ)<br />

CLKINP<br />

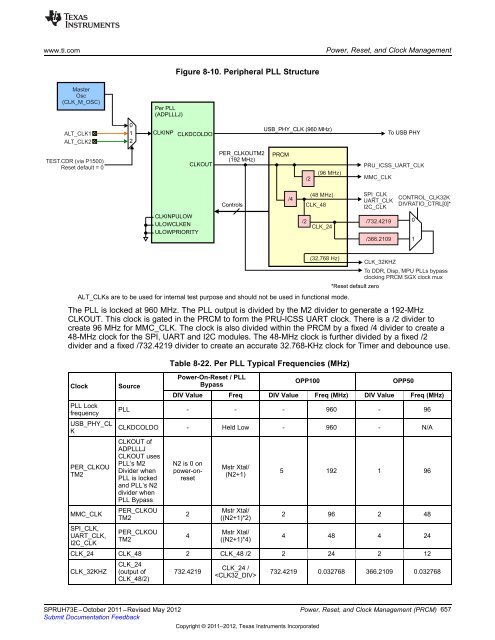

Figure 8-10. Peripheral PLL Structure<br />

CLKDCOLDO<br />

CLKINPULOW<br />

ULOWCLKEN<br />

ULOWPRIORITY<br />

CLKOUT<br />

PER_CLKOUTM2<br />

(192 MHz)<br />

Controls<br />

USB_PHY_CLK (960 MHz)<br />

<strong>PRCM</strong><br />

/4<br />

/2<br />

/2<br />

(96 MHz)<br />

(48 MHz)<br />

CLK_48<br />

CLK_24<br />

(32,768 Hz)<br />

ALT_CLKs are to be used for internal test purpose <strong>and</strong> should not be used in functional mode.<br />

*<strong>Reset</strong> default zero<br />

To USB PHY<br />

PRU_ICSS_UART_CLK<br />

MMC_CLK<br />

SPI_CLK<br />

UART_CLK<br />

I2C_CLK<br />

/732.4219<br />

/366.2109<br />

CLK_32KHZ<br />

CONTROL_CLK32K<br />

DIVRATIO_CTRL[0]*<br />

To DDR, Disp, MPU PLLs bypass<br />

clocking <strong>PRCM</strong> SGX clock mux<br />

The PLL is locked at 960 MHz. The PLL output is divided by the M2 divider to generate a 192-MHz<br />

CLKOUT. This clock is gated in the <strong>PRCM</strong> to form the PRU-ICSS UART clock. There is a /2 divider to<br />

create 96 MHz for MMC_CLK. The clock is also divided within the <strong>PRCM</strong> by a fixed /4 divider to create a<br />

48-MHz clock for the SPI, UART <strong>and</strong> I2C modules. The 48-MHz clock is further divided by a fixed /2<br />

divider <strong>and</strong> a fixed /732.4219 divider to create an accurate 32.768-KHz clock for Timer <strong>and</strong> debounce use.<br />

<strong>Clock</strong> Source<br />

PLL Lock<br />

frequency<br />

Table 8-22. Per PLL Typical Frequencies (MHz)<br />

<strong>Power</strong>-On-<strong>Reset</strong> / PLL<br />

Bypass<br />

OPP100 OPP50<br />

DIV Value Freq DIV Value Freq (MHz) DIV Value Freq (MHz)<br />

PLL - - - 960 - 96<br />

USB_PHY_CL CLKDCOLDO - Held Low - 960 - N/A<br />

K<br />

PER_CLKOU<br />

TM2<br />

CLKOUT of<br />

ADPLLLJ<br />

CLKOUT uses<br />

PLL’s M2<br />

Divider when<br />

PLL is locked<br />

<strong>and</strong> PLL’s N2<br />

divider when<br />

PLL Bypass<br />

N2 is 0 on<br />

power-onreset<br />

Mstr Xtal/<br />

(N2+1)<br />

5 192 1 96<br />

PER_CLKOU Mstr Xtal/<br />

MMC_CLK 2 2 96 2 48<br />

TM2 ((N2+1)*2)<br />

SPI_CLK,<br />

PER_CLKOU Mstr Xtal/<br />

UART_CLK, 4 4 48 4 24<br />

TM2 ((N2+1)*4)<br />

I2C_CLK<br />

CLK_24 CLK_48 2 CLK_48 /2 2 24 2 12<br />

CLK_24<br />

CLK_24 /<br />

CLK_32KHZ (output of 732.4219 732.4219 0.032768 366.2109 0.032768<br />

<br />

CLK_48/2)<br />

SPRUH73E–October 2011–Revised May 2012 <strong>Power</strong>, <strong>Reset</strong>, <strong>and</strong> <strong>Clock</strong> <strong>Management</strong> (<strong>PRCM</strong>)<br />

Submit Documentation Feedback<br />

Copyright © 2011–2012, Texas Instruments Incorporated<br />

0<br />

1<br />

657