FPGA based Hardware Accleration for Elliptic Curve Cryptography ...

FPGA based Hardware Accleration for Elliptic Curve Cryptography ...

FPGA based Hardware Accleration for Elliptic Curve Cryptography ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

D<br />

SUM E K]GiD Qlk DHGIeGk KNGR KTSVUXW Y [mGnK_^`DbacDedZLfKhgnEfj R KNGnK_SoUpW Y [ E KNMPOqGJEFK]GnLfD<br />

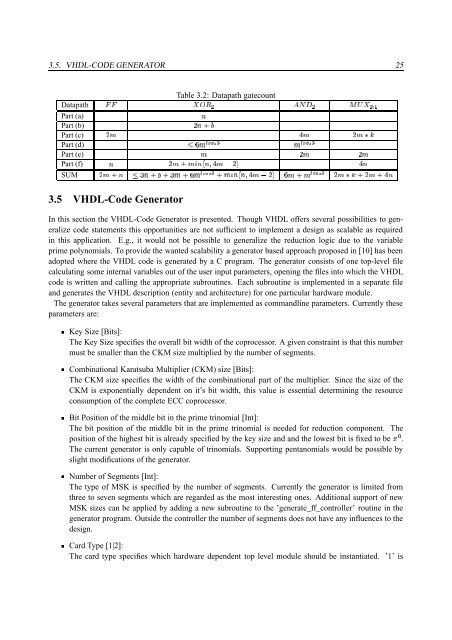

3.5. VHDL-CODE GENERATOR 25<br />

Table 3.2: Datapath gatecount<br />

010 24365,7 8:9@?,2A7B C<br />

Datapath<br />

Part (a)<br />

Part (b)<br />

EFDHGJI<br />

Part E K L£K E KNMPO<br />

(c)<br />

Part Q)R KTSVUXWZYX[ KTSVUXWZY\[<br />

(d)<br />

Part K E K EFK<br />

(e)<br />

Part D E K]GK_^`DbacDedZLfKhgiEfj LfD<br />

(f)<br />

3.5 VHDL-Code Generator<br />

In this section the VHDL-Code Generator is presented. Though VHDL offers several possibilities to generalize<br />

code statements this opportunities are not sufficient to implement a design as scalable as required<br />

in this application. E.g., it would not be possible to generalize the reduction logic due to the variable<br />

prime polynomials. To provide the wanted scalability a generator <strong>based</strong> approach proposed in [10] has been<br />

adopted where the VHDL code is generated by a C program. The generator consists of one top-level file<br />

calculating some internal variables out of the user input parameters, opening the files into which the VHDL<br />

code is written and calling the appropriate subroutines. Each subroutine is implemented in a separate file<br />

and generates the VHDL description (entity and architecture) <strong>for</strong> one particular hardware module.<br />

The generator takes several parameters that are implemented as commandline parameters. Currently these<br />

parameters are:<br />

Key Size [Bits]:<br />

r<br />

The Key Size specifies the overall bit width of the coprocessor. A given constraint is that this number<br />

must be smaller than the CKM size multiplied by the number of segments.<br />

Combinational Karatsuba Multiplier (CKM) size [Bits]:<br />

r<br />

The CKM size specifies the width of the combinational part of the multiplier. Since the size of the<br />

CKM is exponentially dependent on it’s bit width, this value is essential determining the resource<br />

consumption of the complete ECC coprocessor.<br />

Bit Position of the middle bit in the prime trinomial [Int]:<br />

r<br />

The bit position of the middle bit in the prime trinomial is needed <strong>for</strong> reduction component. The<br />

position of the highest bit is already specified by the key size and and the lowest bit is fixed be5<br />

®<br />

to .<br />

The current generator is only capable of trinomials. Supporting pentanomials would be possible by<br />

slight modifications of the generator.<br />

Number of Segments [Int]:<br />

r<br />

The type of MSK is specified by the number of segments. Currently the generator is limited from<br />

three to seven segments which are regarded as the most interesting ones. Additional support of new<br />

MSK sizes can be applied by adding a new subroutine to the ’generate_ff_controller’ routine in the<br />

generator program. Outside the controller the number of segments does not have any influences to the<br />

design.<br />

Card Type [1|2]:<br />

r<br />

The card type specifies which hardware dependent top level module should be instantiated. ’1’ is