FPGA based Hardware Accleration for Elliptic Curve Cryptography ...

FPGA based Hardware Accleration for Elliptic Curve Cryptography ...

FPGA based Hardware Accleration for Elliptic Curve Cryptography ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

4.2. XILINX XCV405E 28<br />

implementation of a CKM with a maximum width of 64 bit within the datapath. The exact number varies<br />

on other generator parameters such as the number of segments.<br />

4.2 Xilinx XCV405E<br />

The XCV405E <strong>FPGA</strong> device from Xilinx, Inc. is a high-end <strong>FPGA</strong> providing 400K system gates. This<br />

device allows the implementation of a CKM with up to 85 bits. Due to the newer technology and powerful<br />

routing resources higher frequencies can be achieved compared to the XC4085XLA device. Similar to the<br />

XC4085XLA the XCV405E is applied on a PCI interface card. This ADM-XRC-II plat<strong>for</strong>m from Alpha<br />

Data, Inc. [22] provides a <br />

ñ<br />

-bit wide PCI interface and 6M Bytes SRAM. It supports up to two different<br />

Xilinx VirtexE or Virtex2 <strong>FPGA</strong> devices on one PCI interface card.<br />

4.3 Atmel AT94K40<br />

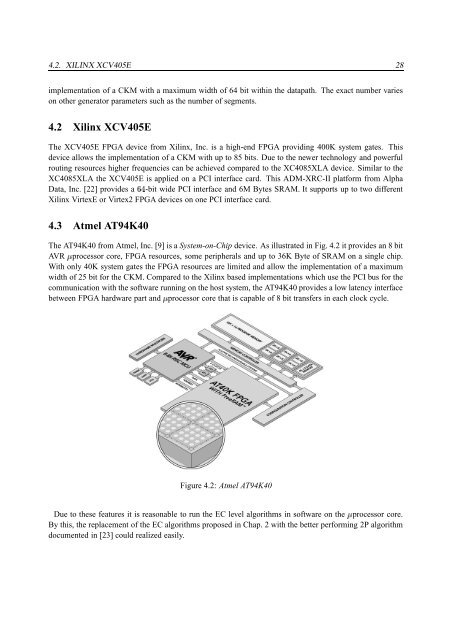

The AT94K40 from Atmel, Inc. [9] is a System-on-Chip device. As illustrated in Fig. 4.2 it provides an 8 bit<br />

AVR Ž processor core, <strong>FPGA</strong> resources, some peripherals and up to 36K Byte of SRAM on a single chip.<br />

With only 40K system gates the <strong>FPGA</strong> resources are limited and allow the implementation of a maximum<br />

width of 25 bit <strong>for</strong> the CKM. Compared to the Xilinx <strong>based</strong> implementations which use the PCI bus <strong>for</strong> the<br />

communication with the software running on the host system, the AT94K40 provides a low latency interface<br />

between <strong>FPGA</strong> hardware part and Ž processor core that is capable of 8 bit transfers in each clock cycle.<br />

Figure 4.2: Atmel AT94K40<br />

Due to these features it is reasonable to run the EC level algorithms in software on the Ž processor core.<br />

By this, the replacement of the EC algorithms proposed in Chap. 2 with the better per<strong>for</strong>ming 2P algorithm<br />

documented in [23] could realized easily.