Carbon Cortex-A15 Model User Guide for SoC Designer

Carbon Cortex-A15 Model User Guide for SoC Designer

Carbon Cortex-A15 Model User Guide for SoC Designer

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

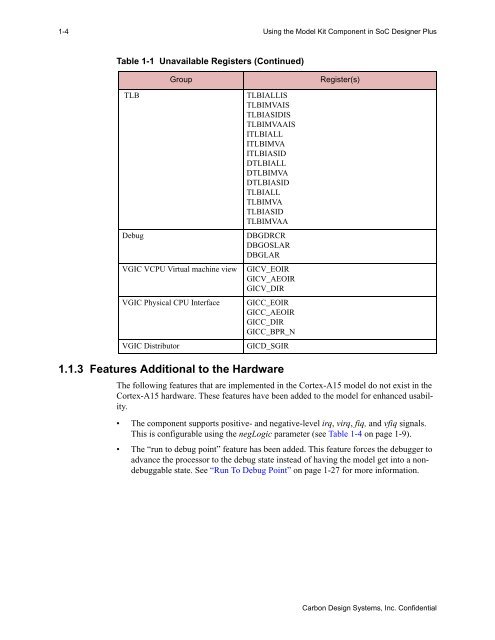

1-4 Using the <strong>Model</strong> Kit Component in <strong>SoC</strong> <strong>Designer</strong> PlusTable 1-1 Unavailable Registers (Continued)GroupRegister(s)TLBDebugVGIC VCPU Virtual machine viewVGIC Physical CPU InterfaceVGIC DistributorTLBIALLISTLBIMVAISTLBIASIDISTLBIMVAAISITLBIALLITLBIMVAITLBIASIDDTLBIALLDTLBIMVADTLBIASIDTLBIALLTLBIMVATLBIASIDTLBIMVAADBGDRCRDBGOSLARDBGLARGICV_EOIRGICV_AEOIRGICV_DIRGICC_EOIRGICC_AEOIRGICC_DIRGICC_BPR_NGICD_SGIR1.1.3 Features Additional to the HardwareThe following features that are implemented in the <strong>Cortex</strong>-<strong>A15</strong> model do not exist in the<strong>Cortex</strong>-<strong>A15</strong> hardware. These features have been added to the model <strong>for</strong> enhanced usability.• The component supports positive- and negative-level irq, virq, fiq, and vfiq signals.This is configurable using the negLogic parameter (see Table 1-4 on page 1-9).• The “run to debug point” feature has been added. This feature <strong>for</strong>ces the debugger toadvance the processor to the debug state instead of having the model get into a nondebuggablestate. See “Run To Debug Point” on page 1-27 <strong>for</strong> more in<strong>for</strong>mation.<strong>Carbon</strong> Design Systems, Inc. Confidential