Intel Pentium III Processor for the SC242 at 450 MHz to 1.0 GHz

Intel Pentium III Processor for the SC242 at 450 MHz to 1.0 GHz

Intel Pentium III Processor for the SC242 at 450 MHz to 1.0 GHz

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

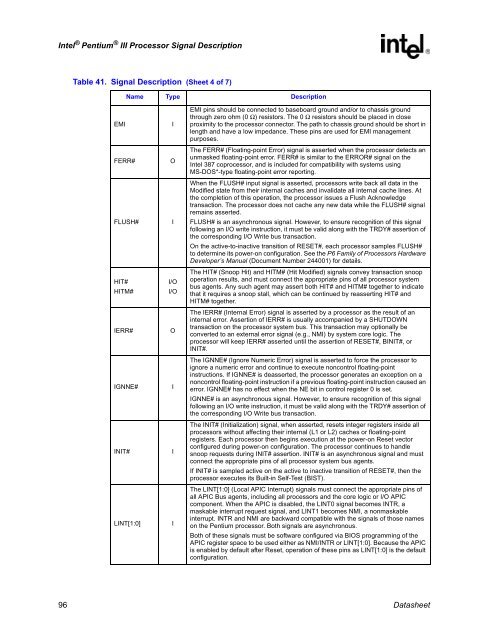

<strong>Intel</strong> ® <strong>Pentium</strong> ® <strong>III</strong> <strong>Processor</strong> Signal DescriptionTable 41. Signal Description (Sheet 4 of 7)Name Type DescriptionEMIFERR#FLUSH#HIT#HITM#IERR#IGNNE#INIT#LINT[1:0]IOII/OI/OO<strong>III</strong>EMI pins should be connected <strong>to</strong> baseboard ground and/or <strong>to</strong> chassis groundthrough zero ohm (0 Ω) resis<strong>to</strong>rs. The 0 Ω resis<strong>to</strong>rs should be placed in closeproximity <strong>to</strong> <strong>the</strong> processor connec<strong>to</strong>r. The p<strong>at</strong>h <strong>to</strong> chassis ground should be short inlength and have a low impedance. These pins are used <strong>for</strong> EMI managementpurposes.The FERR# (Flo<strong>at</strong>ing-point Error) signal is asserted when <strong>the</strong> processor detects anunmasked flo<strong>at</strong>ing-point error. FERR# is similar <strong>to</strong> <strong>the</strong> ERROR# signal on <strong>the</strong><strong>Intel</strong> 387 coprocessor, and is included <strong>for</strong> comp<strong>at</strong>ibility with systems usingMS-DOS*-type flo<strong>at</strong>ing-point error reporting.When <strong>the</strong> FLUSH# input signal is asserted, processors write back all d<strong>at</strong>a in <strong>the</strong>Modified st<strong>at</strong>e from <strong>the</strong>ir internal caches and invalid<strong>at</strong>e all internal cache lines. At<strong>the</strong> completion of this oper<strong>at</strong>ion, <strong>the</strong> processor issues a Flush Acknowledgetransaction. The processor does not cache any new d<strong>at</strong>a while <strong>the</strong> FLUSH# signalremains asserted.FLUSH# is an asynchronous signal. However, <strong>to</strong> ensure recognition of this signalfollowing an I/O write instruction, it must be valid along with <strong>the</strong> TRDY# assertion of<strong>the</strong> corresponding I/O Write bus transaction.On <strong>the</strong> active-<strong>to</strong>-inactive transition of RESET#, each processor samples FLUSH#<strong>to</strong> determine its power-on configur<strong>at</strong>ion. See <strong>the</strong> P6 Family of <strong>Processor</strong>s HardwareDeveloper’s Manual (Document Number 244001) <strong>for</strong> details.The HIT# (Snoop Hit) and HITM# (Hit Modified) signals convey transaction snoopoper<strong>at</strong>ion results, and must connect <strong>the</strong> appropri<strong>at</strong>e pins of all processor systembus agents. Any such agent may assert both HIT# and HITM# <strong>to</strong>ge<strong>the</strong>r <strong>to</strong> indic<strong>at</strong>eth<strong>at</strong> it requires a snoop stall, which can be continued by reasserting HIT# andHITM# <strong>to</strong>ge<strong>the</strong>r.The IERR# (Internal Error) signal is asserted by a processor as <strong>the</strong> result of aninternal error. Assertion of IERR# is usually accompanied by a SHUTDOWNtransaction on <strong>the</strong> processor system bus. This transaction may optionally beconverted <strong>to</strong> an external error signal (e.g., NMI) by system core logic. Theprocessor will keep IERR# asserted until <strong>the</strong> assertion of RESET#, BINIT#, orINIT#.The IGNNE# (Ignore Numeric Error) signal is asserted <strong>to</strong> <strong>for</strong>ce <strong>the</strong> processor <strong>to</strong>ignore a numeric error and continue <strong>to</strong> execute noncontrol flo<strong>at</strong>ing-pointinstructions. If IGNNE# is deasserted, <strong>the</strong> processor gener<strong>at</strong>es an exception on anoncontrol flo<strong>at</strong>ing-point instruction if a previous flo<strong>at</strong>ing-point instruction caused anerror. IGNNE# has no effect when <strong>the</strong> NE bit in control register 0 is set.IGNNE# is an asynchronous signal. However, <strong>to</strong> ensure recognition of this signalfollowing an I/O write instruction, it must be valid along with <strong>the</strong> TRDY# assertion of<strong>the</strong> corresponding I/O Write bus transaction.The INIT# (Initializ<strong>at</strong>ion) signal, when asserted, resets integer registers inside allprocessors without affecting <strong>the</strong>ir internal (L1 or L2) caches or flo<strong>at</strong>ing-pointregisters. Each processor <strong>the</strong>n begins execution <strong>at</strong> <strong>the</strong> power-on Reset vec<strong>to</strong>rconfigured during power-on configur<strong>at</strong>ion. The processor continues <strong>to</strong> handlesnoop requests during INIT# assertion. INIT# is an asynchronous signal and mustconnect <strong>the</strong> appropri<strong>at</strong>e pins of all processor system bus agents.If INIT# is sampled active on <strong>the</strong> active <strong>to</strong> inactive transition of RESET#, <strong>the</strong>n <strong>the</strong>processor executes its Built-in Self-Test (BIST).The LINT[1:0] (Local APIC Interrupt) signals must connect <strong>the</strong> appropri<strong>at</strong>e pins ofall APIC Bus agents, including all processors and <strong>the</strong> core logic or I/O APICcomponent. When <strong>the</strong> APIC is disabled, <strong>the</strong> LINT0 signal becomes INTR, amaskable interrupt request signal, and LINT1 becomes NMI, a nonmaskableinterrupt. INTR and NMI are backward comp<strong>at</strong>ible with <strong>the</strong> signals of those nameson <strong>the</strong> <strong>Pentium</strong> processor. Both signals are asynchronous.Both of <strong>the</strong>se signals must be software configured via BIOS programming of <strong>the</strong>APIC register space <strong>to</strong> be used ei<strong>the</strong>r as NMI/INTR or LINT[1:0]. Because <strong>the</strong> APICis enabled by default after Reset, oper<strong>at</strong>ion of <strong>the</strong>se pins as LINT[1:0] is <strong>the</strong> defaultconfigur<strong>at</strong>ion.96 D<strong>at</strong>asheet