STORE STATUS (STS) Store Status FunctionFORMATSOP F T Disp 15 0 OP F T 1A80 Cond 15 0 Address 15I 01011,01110[IIIIIIIIIII 010 1 11011I1I oioo2 8–B X X 2 C–F 0 or 8 0 X X X XDESCR IPTION117162BIThe status of <strong>the</strong> carry and overflow indicators arestored in bit positions 14 and 15, respectively, of <strong>the</strong>core-storage location specified by <strong>the</strong> effective address(EA) of <strong>the</strong> instruction. The carry and overflow indicatorsare <strong>the</strong>n reset. Bit positions 0 through 7 of <strong>the</strong> wordat <strong>the</strong> EA remain unchanged and bit positions 8 through13 are reset to 0's as shown in <strong>the</strong> illustration.If <strong>the</strong> long format is used, bit 9 (BO) of <strong>the</strong> instructionmust be 0 for a store status function; o<strong>the</strong>rwise awrite or clear storage protect bit function is performed0 13 14 IS10 . 0 ,000 ,01 I IUnchangedas described on <strong>the</strong> next page.OverflowCarryNEMTHE CARRY AND OVERFLOW INDICATORS are resetas <strong>the</strong>y are stored.EXAMPLESAssembler Language CodingEquivalent Machine Language Instruction21Label25Operation27 30FT323335 40SeeNoteHexadecimalValueDescriptioni 1 S ,T IS, D,I,SIP,,28XXStore status of indicators in CSL at EA (I + DISP)i , 1 SITISI I D, LS ,P,,29XX Store status of indicators in CSL at EA (XR1 + DISP)1 1 S,TIS, 2 D,I ,S ,P, I 2AXX Store status of indicators in CSL at EA (XR2 + DISP)1 1 SITISI 3 D, I ,S IP, , 2BXX Store status of indicators in CSL at EA (XR3 + DISP), SITIS, L A,D,D,R, , 2C00XXXX Store status of indicators in CSL at EA (Addr)1 1 S ,T ,S, L I A,D,D,R, , 2D00XXXX Store status of indicators in CSL at EA (Addr + XR1)1 1 S1T,S 1 L 2 AID ,D ,R, 1 2EOOXXXX Store status of indicators in CSL at EA (Addr + XR2)I S I-1,S, L 3 A,D 1D ,R, , 2F00XXXX Store status of indicators in CSL at EA (Addr + XR3), i S,T,S, I A,D ,D,R, , 2C80XXXX Store status of indicators in CSL at EA (V in CSL at Addr), , S,TISI I I A,D,D,R,/212/80XXXX Store status of indicators in CSL at EA (V in CSL at "AddrI I 1 1 11 1 1 1I 1+ XR I")1 1 S,T,S, I 2 A,D ,D ,R, , 2E80XXXX Store status of indicators in CSL at EA (V in CSL at "Addri I 1 , , I , 1 1 1 I I 1 I + XR2")I 1 1 S IT,S, I 3 A,D,D,R, , 2F80XXXX Store status of indicators in CSL at EA (V in CSL at "Addr1 11 1 1 1 • 1 1 1 1 1 1 1 1 + XR3")FormatShortInstructionLongInstructionDirectAddressingLongInstructionIndirectAddressing22STS

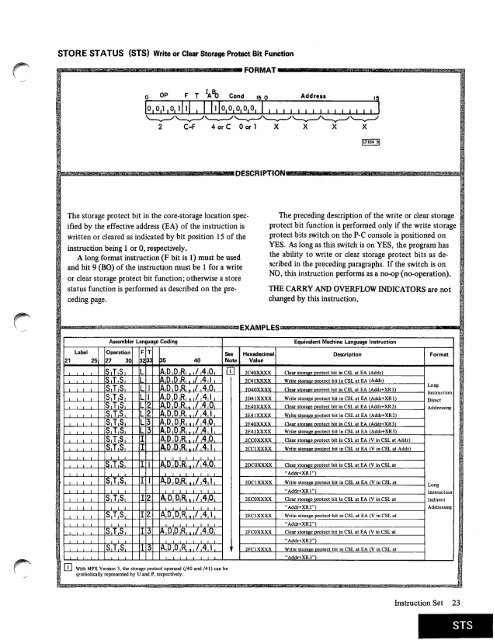

STORE STATUS (STS) Write or Clear Storage Protect Bit FunctionFORMAT0 OP F T 'A DO Coed 15 0 Address 15, I ijo,o,o,o,o, „ „ I „ , , I I2 C-F 4 or C 0 or 1 X X X X117164 B1DESCRIPTIONThe storage protect bit in <strong>the</strong> core-storage location specifiedby <strong>the</strong> effective address (EA) of <strong>the</strong> instruction iswritten or cleared as indicated by bit position 15 of <strong>the</strong>instruction being 1 or 0, respectively.A long format instruction (F bit is 1) must be usedand bit 9 (BO) of <strong>the</strong> instruction must be 1 for a writeor clear storage protect bit function; o<strong>the</strong>rwise a storestatus function is performed as described on <strong>the</strong> precedingpage.The preceding description of <strong>the</strong> write or clear storageprotect bit function is performed only if <strong>the</strong> write storageprotect bits switch on <strong>the</strong> P-C console is positioned onYES. As long as this switch is on YES, <strong>the</strong> program has<strong>the</strong> ability to write or clear storage protect bits as describedin <strong>the</strong> preceding paragraphs. If <strong>the</strong> switch is onNO, this instruction performs as a no-op (no-operation).THE CARRY AND OVERFLOW INDICATORS are notchanged by this instruction.EXAMPLES714 .12Label21 25Assembler Language CodingOperation27 30FT323335 40SeeNoteHexadecimalValueEquivalent Machine Language InstructionDescription, 1 S Il l s I L A,D,D,R, ,1/14,012C40XXXX Clear storage protect bit in CSL at EA (Addr)I , I MIS, L AA) il) p , , 1/ 1411 ,2C41XXXX Write storage protect bit in CSL at EA (Addr)I 1 I S I T I S, L I A,D,D,R,, ,/ 1 4,0 12D40XXXX Clear storage protect bit in CSL at EA (Addr+XR I)1 i I S IT 'S ., L I A,D,D,R, III 4,1 ,2D4IXXXX Write storage protect bit in CSL at EA (Addr+XR I), , 1 S I T I S, L 2 A,D,D,R 1 , ,/ .4 1 0 1 2E4 OXXXX Clear storage protect bit in CSL at EA (Addr+XR2)1 1 1 S,T,S, L 2 A,D,D,R 1 , 1 / 1 4,1 , 2E41XXXX Write storage protect bit in CSL at EA (Addr+XR2)I I I I S,T,S, L 3 A,D,D,R, , ,/ 1 4 10, 2F40XXXX Clear storage protect bit in CSL at EA (Addr+XR3), , S,T,S, L 3 A,D,D1R1, 1/,41 II 2F41XXXX Write storage protect bit in CSL at EA (Addr+XR3)I 1 S,T,Si I A,D,D,R 1 , ,/,4,0, 2CCOX.XXX Clear storage protect bit in CSL at EA (V in CSL at Addr), , 1 S iT I S, I A,D,D,R, I 1,4 1 I 1 2CCIXXXX Write storage protect bit in CSL at EA (V in CSL at Addr)I i I I I i 1 1 1 1 1 1 1 1I I I S,T,S, I I A,D,D,R, ,1/14,0, 2DCOXXXX Clear storage protect bit in CSL at EA (V in CSL atI 1 1 1 1 I t 1 1 1 1 1 1 1 1"Addr+XR 1")1 i I S,T,S, I I A,D,D,R; ,,/,41112DC1XXXX Write storage protect bit in CSL at EA (V in CSL atI I I I I I 1 1 1 1 I I 11 "Addr+XR I")1 I I S,T,S, I 2 A, D I DR! , ,/,4 10, 2ECOXXXX Clear storage protect bit in CSL at EA (V in CSL atI I I I i I I 1 I 1 1 1 I I I "Addr+XR2")I 1 S,T,S, I 2 A,D,D,R,,,/ ,4, I, 2ECIXXXX Write storage protect bit in CSL at EA (V in CSL atI i i 1 1 1 1 i I I 1 1 1 "Addr+XR2")I 1 I S,T,S, I 3 A,D,D,R, ,,/,4,0, 2FCOXXXX Clear storage protect bit in CSL at EA (V in CSL atI I I I I I i I ii i I t I "Addr+XR3")i 1 SiTIS, 1 3 4,0 1 1),R, , J 1 4,1 1 2FCIXXXX Write storage protect bit in CSL at EA (V in CSL at1 I 1 I 1 I 1 i I "Addr+XR3")A With MPX Version 3, <strong>the</strong> storage protect operand (/40 and /41) can besymbolically represented by U and P, respectively.FormatLongInstructionDirectAddressingLongInstructionIndirectAddressingInstruction Set 23STS

- Page 1 and 2: File No. 1800-01Order No. GA26-5918

- Page 3 and 4: ContentsINTRODUCTION 1SYSTEM DESCRI

- Page 5 and 6: Thermocouple Conversion ExampleConv

- Page 7: Status Character 2412790 ADAPTER PR

- Page 12: Processor - ControllerCoreStorageOu

- Page 16 and 17: Page of GA26-5918-8Revised July 14,

- Page 18 and 19: egister or the index register speci

- Page 20 and 21: Short InstructionDDOne WordInstruct

- Page 22 and 23: Instruction SetThe 1800 system inst

- Page 24 and 25: LOAD ACCUMULATOR (LD)FORMATS oitamw

- Page 26 and 27: STORE ACCUMULATOR (STO)FORMATSF 0 O

- Page 28 and 29: LOAD INDEX (LDX)0 OP F T Disp 151 0

- Page 32 and 33: LOAD STATUS (LDS)117165 A1DESCRIPTI

- Page 34 and 35: Page of GA26-5918-8Revised July 14,

- Page 36 and 37: SUBTRACT DOUBLE (SD).fartzaielTmEas

- Page 38: DIVIDE (D)FORMATS0 OP F T DispF T I

- Page 41 and 42: LOGICAL EXCLUSIVE OR (EOR)'FORMATS

- Page 43 and 44: SHIFT LEFT A AND Q (SLT)altkae..,.:

- Page 46 and 47: SHIFT RIGHT LOGICAL A (SRA)FORMAT s

- Page 48 and 49: ROTATE RIGHT A AND Q (RTE)FORMAT ta

- Page 50 and 51: BRANCH OR SKIP ON CONDITION (BSC OR

- Page 52 and 53: a4.-4KA4rE4.7.9.4.&.4VA/M4:14/24...

- Page 54 and 55: ',V.71..1.41VV4-02,P2A,V4,1%1,L—N

- Page 56 and 57: COMPARE (CMP)FORMATS0 OP F T Disp 1

- Page 58 and 59: Page of GA26-5918-8Revised July 14,

- Page 60 and 61: MachineCyclesAUGEND (A-reg) and ADD

- Page 62 and 63: Page of GA26-5918-8Revised July 14,

- Page 64 and 65: Page of GA26-5918-8Revised July 14,

- Page 66 and 67: chain is accomplished as follows: T

- Page 68 and 69: Page of GA26-5918-8Revised July 14,

- Page 70 and 71: Page of GA26-5918-8Revised July 14,

- Page 72 and 73: Page of GA26-5918-8Revised July 14,

- Page 74 and 75: InterruptTo allow for coordination

- Page 76 and 77: Page of GA26-5918-8Revised July 14,

- Page 78 and 79: Page of GA26-5918-8Revised July 14,

- Page 80 and 81:

After a request for service has bee

- Page 82 and 83:

2. The forced BSI with indirect add

- Page 84 and 85:

Storage ProtectionStorage protectio

- Page 86 and 87:

Page of GA26-5918-8Revised January

- Page 88 and 89:

Processor-Controller ConsoleThe pro

- Page 90 and 91:

117674,Figure 23. Console Pushbutto

- Page 92 and 93:

Page of GA26-5918-8Revised July 14,

- Page 94 and 95:

Page of GA26-5918-8Revised July 14,

- Page 96 and 97:

DATA FLOW DISPLAYSSix rows of light

- Page 98 and 99:

This command causes the console int

- Page 100 and 101:

High -LevelHigh -Level Low-LevelLow

- Page 102 and 103:

Page of GA26-5918-8Revised July 14,

- Page 104 and 105:

CUSTOM ELEMENT: This element is ava

- Page 106 and 107:

The clock stop period does not dire

- Page 108 and 109:

Numberingwithin 18511851's withMult

- Page 110 and 111:

selected analog signal to a digital

- Page 112 and 113:

Page of GA26-5918-8Revised July 14,

- Page 114 and 115:

0 1 2 3 4 5 8 7 0 9 10 14 15Indicat

- Page 116 and 117:

Direct Program Control Operations P

- Page 118 and 119:

Temp TempF C1652° 9001472° 81292

- Page 120 and 121:

2. Determine the ADC reading (Q val

- Page 122 and 123:

Digital InputDigital input features

- Page 124 and 125:

ead operation without external sync

- Page 126 and 127:

AdapterFirstSecondThirdFourthFifthS

- Page 128 and 129:

the next input group address (conta

- Page 130 and 131:

status word (PISW), the PISW is rea

- Page 132 and 133:

ProcessorControllerOut Bus(16 - Bit

- Page 134 and 135:

DAC reference voltage used in devel

- Page 136 and 137:

126 is assigned to the second group

- Page 138 and 139:

The input/output control command (I

- Page 140 and 141:

Page of GA26-5918-8Revised July 14,

- Page 142 and 143:

1053/1816 Printer IOCC'sCE ModeSpec

- Page 144 and 145:

Keyboard entries are not printed au

- Page 146 and 147:

error is detected, the program may

- Page 148 and 149:

the keyboard into a storage-protect

- Page 150 and 151:

Channel••• ••••• 14

- Page 152 and 153:

READER ANY ERROR: This indicator tu

- Page 154 and 155:

Page of GA26-5918-8Revised July 14,

- Page 156 and 157:

Even-Numbered ColumnsOdd-Numbered C

- Page 158 and 159:

1442 DSW Interrupt IndicatorsFigure

- Page 160 and 161:

The preceding examples show that if

- Page 162 and 163:

CharHexCore Storage BitsTypebar2 5

- Page 164 and 165:

Page of GA26-5918-8Revised July 14,

- Page 166 and 167:

CE PRINTER BUSY: When the 1443 is i

- Page 168 and 169:

DrumDownDRUM FAST RUN: This switch

- Page 170 and 171:

1627 DSW Noninterrupt IndicatorsFig

- Page 172 and 173:

120255A1Each track is divided into

- Page 174 and 175:

This command places the disk storag

- Page 176 and 177:

ANY ERROR: This indicator turns on

- Page 178 and 179:

LogicalDataRecordIBGapLRCIBGap.._01

- Page 180 and 181:

A tape mark read from seven-track t

- Page 182 and 183:

Modifier bits perform the five func

- Page 184 and 185:

an XIO initialize read operation wi

- Page 186 and 187:

Communications AdapterINTRODUCTIONT

- Page 188 and 189:

character (bit positions 0 through

- Page 190 and 191:

Bit PositionsP, 7, 6, 54, 3, 2, 100

- Page 192 and 193:

Standard replies as well as NAK cau

- Page 194 and 195:

either seeking characters received

- Page 196 and 197:

CA IOCC'sInitialize Write0 15 0 4 8

- Page 198 and 199:

TIMEOUT: This indicator turns on, c

- Page 200 and 201:

0 I 2 3 4 5 6 7 8 9 10 11 i2 13 14

- Page 202 and 203:

ETB, ETX, AND ENQ: These characters

- Page 204 and 205:

.■••.0■-3toCOc.nroz0F21.0fa

- Page 206 and 207:

Selector ChannelThe selector channe

- Page 208 and 209:

CCW Word 1 CCW Word 2 CCW Word 315B

- Page 210 and 211:

Page of GA26-5918-8Revised July 14,

- Page 212 and 213:

limited to the number of sense byte

- Page 214 and 215:

CSW Word 1 CSW Word 2 CSW Word 3 CS

- Page 216 and 217:

CSW Word 2 CSW Word 3CSW Word 40 3

- Page 218 and 219:

Termination of an operation with a

- Page 220 and 221:

Device end, when subsequently provi

- Page 222 and 223:

System /360 AdapterINTRODUCTIONThe

- Page 224 and 225:

specified by the channel command wo

- Page 226 and 227:

ATTENTION: This status indicates th

- Page 228 and 229:

Page of GA26-5918-8Revised July 14,

- Page 230 and 231:

HALT: This bit turns on, causing an

- Page 232 and 233:

Page of GA26-5918-8Revised July 14,

- Page 234 and 235:

Start Byte AS Address Byte Device A

- Page 236 and 237:

Page of GA26-5918-8Revised July 14,

- Page 238 and 239:

Read data request causes the adapte

- Page 240 and 241:

If a 1053 Printer is addressed by t

- Page 242 and 243:

specific 16-word block within the c

- Page 244 and 245:

LCCBWord1Address Word(Active Frame)

- Page 246 and 247:

channel active is interrogated. If

- Page 248 and 249:

Form GA26-5918-8Page Revised 10/1/7

- Page 250 and 251:

AREA STATION LOCAL I/O TRANSACTION

- Page 252 and 253:

Form GA26-5918-8Page Revised 10/1/7

- Page 254 and 255:

244Form GA26-5918-8Page Added 10/1/

- Page 256 and 257:

Page of GA26-5918-8Revised July 14,

- Page 258 and 259:

Form GA26-5918-8Page Revised 10/1/7

- Page 260 and 261:

Form GA26-5918-8Page Revised 10/1/7

- Page 262 and 263:

When all segments are bypassed modi

- Page 264 and 265:

0. It can occur only during a read

- Page 266 and 267:

Page of GA26-5918-8Revised July 14,

- Page 268 and 269:

HexadecimalValueDouble Compare (DCM

- Page 270 and 271:

Appendix B. I/O Device AddressingTh

- Page 272 and 273:

1054 AND 1055 PAPER TAPEWRITE: Punc

- Page 274 and 275:

INITIALIZE WRITE: Move contents of

- Page 276 and 277:

INITIALIZE READ: Move tape data to

- Page 278 and 279:

AREA FEATURE 0 1 2 3 4 5 6 7 8 9•

- Page 280 and 281:

Form GA26-5918-8Page Revised 10/1/7

- Page 282 and 283:

Page of GA26-5918-8Revised July 14,

- Page 284 and 285:

Clear (Continued)Storage (Continued

- Page 286 and 287:

Converting Thermocouple Characteris

- Page 288 and 289:

Page of GA26-5918-8Revised July 14,

- Page 290 and 291:

4Input/Output Control (Continued)On

- Page 292 and 293:

Loop Channel (Continued)Control Blo

- Page 294 and 295:

Pulse OutputDescription of 125Timer

- Page 296 and 297:

Storage ProtectBit (S) 10Bit Light

- Page 298 and 299:

1053 Printer (Continued)Maximum Rat

- Page 300 and 301:

1810 Disk Storage (Continued)Read/W

- Page 302:

Form GA26-5918-8Page Revised 10/1/7

- Page 305:

IBM Technical Newsletter File Numbe

- Page 308 and 309:

^;``

- Page 311 and 312:

• READER'S COMMENT FORM•▪ IBM

- Page 313 and 314:

• READER'S COMMENT FORM• IBM 18

- Page 315 and 316:

• READER'S COMMENT FORM• IBM 18