Intel 80200 Processor based on Intel XScale Microarchitecture

Intel 80200 Processor based on Intel XScale Microarchitecture

Intel 80200 Processor based on Intel XScale Microarchitecture

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

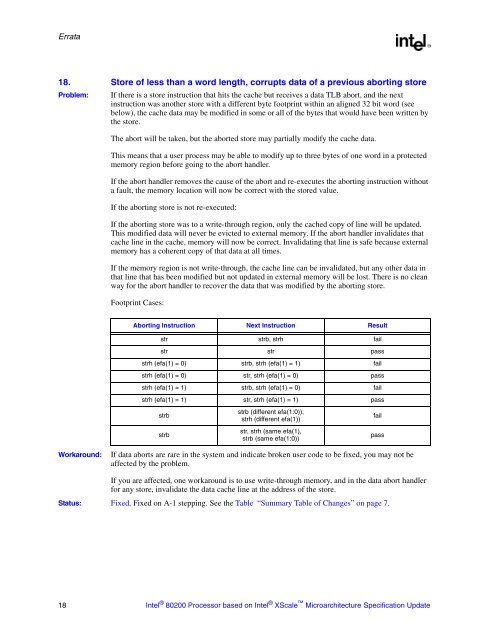

Errata18. Store of less than a word length, corrupts data of a previous aborting storeProblem:If there is a store instructi<strong>on</strong> that hits the cache but receives a data TLB abort, and the nextinstructi<strong>on</strong> was another store with a different byte footprint within an aligned 32 bit word (seebelow), the cache data may be modified in some or all of the bytes that would have been written bythe store.The abort will be taken, but the aborted store may partially modify the cache data.This means that a user process may be able to modify up to three bytes of <strong>on</strong>e word in a protectedmemory regi<strong>on</strong> before going to the abort handler.If the abort handler removes the cause of the abort and re-executes the aborting instructi<strong>on</strong> withouta fault, the memory locati<strong>on</strong> will now be correct with the stored value.If the aborting store is not re-executed:If the aborting store was to a write-through regi<strong>on</strong>, <strong>on</strong>ly the cached copy of line will be updated.This modified data will never be evicted to external memory. If the abort handler invalidates thatcache line in the cache, memory will now be correct. Invalidating that line is safe because externalmemory has a coherent copy of that data at all times.If the memory regi<strong>on</strong> is not write-through, the cache line can be invalidated, but any other data inthat line that has been modified but not updated in external memory will be lost. There is no cleanway for the abort handler to recover the data that was modified by the aborting store.Footprint Cases:Aborting Instructi<strong>on</strong> Next Instructi<strong>on</strong> Resultstr strb, strh failstr str passstrh (efa(1) = 0) strb, strh (efa(1) = 1) failstrh (efa(1) = 0) str, strh (efa(1) = 0) passstrh (efa(1) = 1) strb, strh (efa(1) = 0) failstrh (efa(1) = 1) str, strh (efa(1) = 1) passstrbstrbstrb (different efa(1:0)),strh (different efa(1))str, strh (same efa(1),strb (same efa(1:0))failpassWorkaround:If data aborts are rare in the system and indicate broken user code to be fixed, you may not beaffected by the problem.If you are affected, <strong>on</strong>e workaround is to use write-through memory, and in the data abort handlerfor any store, invalidate the data cache line at the address of the store.Status: Fixed. Fixed <strong>on</strong> A-1 stepping. See the Table “Summary Table of Changes” <strong>on</strong> page 7.18 <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <str<strong>on</strong>g>80200</str<strong>on</strong>g> <str<strong>on</strong>g>Processor</str<strong>on</strong>g> <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <strong>XScale</strong> <strong>Microarchitecture</strong> Specificati<strong>on</strong> Update