Intel 80200 Processor based on Intel XScale Microarchitecture

Intel 80200 Processor based on Intel XScale Microarchitecture

Intel 80200 Processor based on Intel XScale Microarchitecture

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

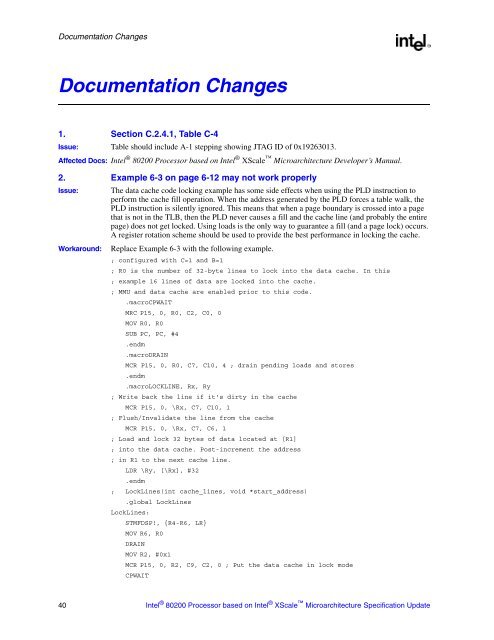

Documentati<strong>on</strong> ChangesDocumentati<strong>on</strong> Changes1. Secti<strong>on</strong> C.2.4.1, Table C-4Issue: Table should include A-1 stepping showing JTAG ID of 0x19263013.Affected Docs: <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <str<strong>on</strong>g>80200</str<strong>on</strong>g> <str<strong>on</strong>g>Processor</str<strong>on</strong>g> <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <strong>XScale</strong> <strong>Microarchitecture</strong> Developer’s Manual.2. Example 6-3 <strong>on</strong> page 6-12 may not work properlyIssue:Workaround:The data cache code locking example has some side effects when using the PLD instructi<strong>on</strong> toperform the cache fill operati<strong>on</strong>. When the address generated by the PLD forces a table walk, thePLD instructi<strong>on</strong> is silently ignored. This means that when a page boundary is crossed into a pagethat is not in the TLB, then the PLD never causes a fill and the cache line (and probably the entirepage) does not get locked. Using loads is the <strong>on</strong>ly way to guarantee a fill (and a page lock) occurs.A register rotati<strong>on</strong> scheme should be used to provide the best performance in locking the cache.Replace Example 6-3 with the following example.; c<strong>on</strong>figured with C=1 and B=1; R0 is the number of 32-byte lines to lock into the data cache. In this; example 16 lines of data are locked into the cache.; MMU and data cache are enabled prior to this code..macroCPWAITMRC P15, 0, R0, C2, C0, 0MOV R0, R0SUB PC, PC, #4.endm.macroDRAINMCR P15, 0, R0, C7, C10, 4 ; drain pending loads and stores.endm.macroLOCKLINE, Rx, Ry; Write back the line if it's dirty in the cacheMCR P15, 0, \Rx, C7, C10, 1; Flush/Invalidate the line from the cacheMCR P15, 0, \Rx, C7, C6, 1; Load and lock 32 bytes of data located at [R1]; into the data cache. Post-increment the address; in R1 to the next cache line.LDR \Ry, [\Rx], #32.endm; LockLines(int cache_lines, void *start_address).global LockLinesLockLines:STMFDSP!, {R4-R6, LR}MOV R6, R0DRAINMOV R2, #0x1MCR P15, 0, R2, C9, C2, 0 ; Put the data cache in lock modeCPWAIT40 <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <str<strong>on</strong>g>80200</str<strong>on</strong>g> <str<strong>on</strong>g>Processor</str<strong>on</strong>g> <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <strong>XScale</strong> <strong>Microarchitecture</strong> Specificati<strong>on</strong> Update