Intel 80200 Processor based on Intel XScale Microarchitecture

Intel 80200 Processor based on Intel XScale Microarchitecture

Intel 80200 Processor based on Intel XScale Microarchitecture

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

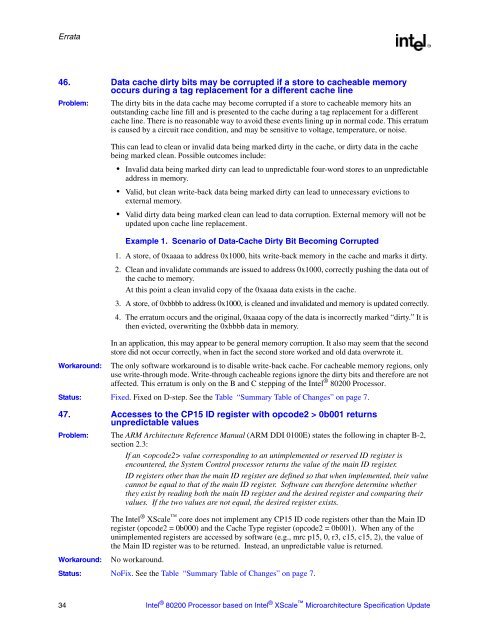

Errata46. Data cache dirty bits may be corrupted if a store to cacheable memoryoccurs during a tag replacement for a different cache lineProblem:Workaround:The dirty bits in the data cache may become corrupted if a store to cacheable memory hits anoutstanding cache line fill and is presented to the cache during a tag replacement for a differentcache line. There is no reas<strong>on</strong>able way to avoid these events lining up in normal code. This erratumis caused by a circuit race c<strong>on</strong>diti<strong>on</strong>, and may be sensitive to voltage, temperature, or noise.This can lead to clean or invalid data being marked dirty in the cache, or dirty data in the cachebeing marked clean. Possible outcomes include:• Invalid data being marked dirty can lead to unpredictable four-word stores to an unpredictableaddress in memory.• Valid, but clean write-back data being marked dirty can lead to unnecessary evicti<strong>on</strong>s toexternal memory.• Valid dirty data being marked clean can lead to data corrupti<strong>on</strong>. External memory will not beupdated up<strong>on</strong> cache line replacement.Example 1. Scenario of Data-Cache Dirty Bit Becoming Corrupted1. A store, of 0xaaaa to address 0x1000, hits write-back memory in the cache and marks it dirty.2. Clean and invalidate commands are issued to address 0x1000, correctly pushing the data out ofthe cache to memory.At this point a clean invalid copy of the 0xaaaa data exists in the cache.3. A store, of 0xbbbb to address 0x1000, is cleaned and invalidated and memory is updated correctly.4. The erratum occurs and the original, 0xaaaa copy of the data is incorrectly marked “dirty.” It isthen evicted, overwriting the 0xbbbb data in memory.In an applicati<strong>on</strong>, this may appear to be general memory corrupti<strong>on</strong>. It also may seem that the sec<strong>on</strong>dstore did not occur correctly, when in fact the sec<strong>on</strong>d store worked and old data overwrote it.The <strong>on</strong>ly software workaround is to disable write-back cache. For cacheable memory regi<strong>on</strong>s, <strong>on</strong>lyuse write-through mode. Write-through cacheable regi<strong>on</strong>s ignore the dirty bits and therefore are notaffected. This erratum is <strong>on</strong>ly <strong>on</strong> the B and C stepping of the <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <str<strong>on</strong>g>80200</str<strong>on</strong>g> <str<strong>on</strong>g>Processor</str<strong>on</strong>g>.Status: Fixed. Fixed <strong>on</strong> D-step. See the Table “Summary Table of Changes” <strong>on</strong> page 7.47. Accesses to the CP15 ID register with opcode2 > 0b001 returnsunpredictable valuesProblem:The ARM Architecture Reference Manual (ARM DDI 0100E) states the following in chapter B-2,secti<strong>on</strong> 2.3:If an value corresp<strong>on</strong>ding to an unimplemented or reserved ID register isencountered, the System C<strong>on</strong>trol processor returns the value of the main ID register.ID registers other than the main ID register are defined so that when implemented, their valuecannot be equal to that of the main ID register. Software can therefore determine whetherthey exist by reading both the main ID register and the desired register and comparing theirvalues. If the two values are not equal, the desired register exists.The <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <strong>XScale</strong> core does not implement any CP15 ID code registers other than the Main IDregister (opcode2 = 0b000) and the Cache Type register (opcode2 = 0b001). When any of theunimplemented registers are accessed by software (e.g., mrc p15, 0, r3, c15, c15, 2), the value ofthe Main ID register was to be returned. Instead, an unpredictable value is returned.Workaround:No workaround.Status: NoFix. See the Table “Summary Table of Changes” <strong>on</strong> page 7.34 <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <str<strong>on</strong>g>80200</str<strong>on</strong>g> <str<strong>on</strong>g>Processor</str<strong>on</strong>g> <str<strong>on</strong>g>based</str<strong>on</strong>g> <strong>on</strong> <str<strong>on</strong>g>Intel</str<strong>on</strong>g> ® <strong>XScale</strong> <strong>Microarchitecture</strong> Specificati<strong>on</strong> Update