Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

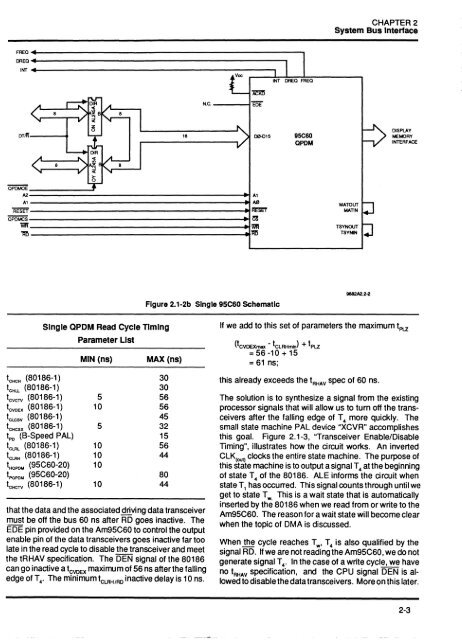

F~a~----------------________________________________ --,rnEa~----------------------------------------------1I~~------------------------------------~~----I~--~~~~-------,CHAPTER 2System Bus InterfaceN.C. -------IDTiI'I------"1 16Q0.D1S95C60QPDMDISPLAYMEMORYINTERFACE'QPiiiFEA2A1iiEsE'i'QP5MCswrf1Irl'" NlJ~1!§mMATOUTMAnNTSYNO\JTTSYNINFigure 2.1-2b Single 95C60 Schematic9682A2.2-2Single QPDM Read Cycle TimingParameter ListMIN (ns)MAX (ns)tCHCH (80186-1) 30teHLL (80186-1) 30tcveN (80186-1) 5 56tCVOEX (80186-1) 10 56tCLCSV (80186-1) 45tCHesx (80186-1) 5 32tpo (B-Speed PAL) 15tCLRL (80186-1) 10 56teLRH (80186-1) 10 44tHOPOM (95C60-20) 10tpOPOM (95C60-20) 80teHeTv (80186-1) 10 44that the data and the associated driving data transceivermust be off the bus 60 ns after RD goes inactive. TheEDE pin provided on the Am95C60 to control the outputenable pin of the data transceivers goes inactive far toolate in the read cycle to disable the transceiver and meetthe tRHAV specification. The DEN signal of the 80186can go inactive a tCVDEX maximum of 56 ns after the fallingedge of T4. The minimum tCLRH/RD inactive delay is 10 ns.If we add to this set of parameters the maximum tp\.z(tCVOEXmax - tCLRHmln) + tpLZ=56-10 + 15= 61 ns;this already exceeds the tRHAV spec of 60 ns.The solution is to synthesize a signal from the existingprocessor signals that will allow us to turn off the transceiversafter the falling edge of T4 more quickly. Thesmall state machine PAL device "XCVR" accomplishesthis goal. Figure 2.1-3, ''Transceiver Enable/DisableTiming", illustrates how the circuit works. An invertedCLK(OU1) clocks the entire state machine. The purpose ofthis state machine is to output a signal T 4 at the beginningof state T4 of the 80186. ALE informs the circuit whenstate T, has occurred. This signal counts through until weget to state T w. This is a wait state that is automaticallyinserted by the 80186 when we read from or write to theAm95C60. The reason for a wait state will become clearwhen the topic of DMA is discussed.When the cycle reaches T w ' T4 is also qualified by thesignal RD. If we are not reading the Am95C60, wedo notgenerate signal T4. In the case of a write cycle, we haveno tRHAV specification, and the CPU signal DEN is allowedto disable the data transceivers. More on this later.2-3