- Page 1 and 2:

Am95C60Quad Pixel Dataflow ManagerA

- Page 3 and 4: Authors:Tom CrawfordStuart TindallE

- Page 6: Table of ContentsCHAPTER 1 Overview

- Page 10 and 11: CHAPTER 1OverviewDESIGN APPLICATION

- Page 12 and 13: and the information is read in on t

- Page 14 and 15: CHAPTER 1Overviewservice. As with t

- Page 16: CHAPTER 2System Bus Interface2.1 Am

- Page 19 and 20: CHAPTER 2System Bus InterfaceT4 1W

- Page 21 and 22: CHAPTER 2System Bus InterfaceALE ~t

- Page 23 and 24: CHAPTER 2System Bus InterfaceDMAQPD

- Page 25 and 26: CHAPTER 2System Bus Interfacevee20

- Page 27 and 28: CHAPTER 2System Bus InterfaceMATOUT

- Page 29 and 30: CHAPTER 2System Bus InterfaceQPDM i

- Page 31 and 32: CHAPTER 2System Bus InterfaceJ01501

- Page 33 and 34: CHAPTER 2System Bus Interfacedresse

- Page 35 and 36: CHAPTER 2System Bus InterfaceCUPL v

- Page 37 and 38: CHAPTER 2System Bus InterfaceCUPL v

- Page 39 and 40: CHAPTER 2System Bus InterfaceCUPL v

- Page 41 and 42: CHAPTER 2System Bus InterfaceCUPL V

- Page 43 and 44: CHAPTER 2System Bus InterfaceCUPL v

- Page 45 and 46: CHAPTER 2System Bus Interface2.2 VM

- Page 47 and 48: CHAPTER 2System Bus InterfaceAs ano

- Page 49 and 50: CHAPTER 2System Bus InterfaceADDRBu

- Page 51 and 52: CHAPTER 2System Bus Interface2.3 68

- Page 53: CHAPTER 2System Bus InterfaceFCVA+3

- Page 57 and 58: CHAPTER 2System Bus Interfacethat c

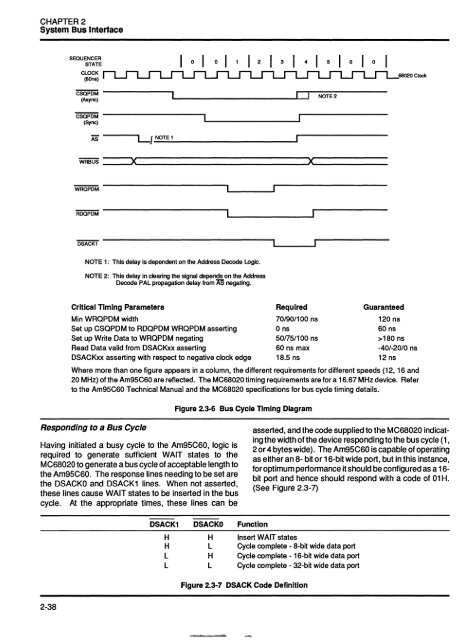

- Page 59 and 60: CHAPTER 2System Bus InterfaceAs the

- Page 61 and 62: CHAPTER 2System Bus InterfaceDecode

- Page 63 and 64: CHAPTER 2System Bus InterfaceAppend

- Page 65 and 66: CHAPTER 2System Bus Interface2.3.12

- Page 67 and 68: CHAPTER 2System Bus InterfaceAPPEND

- Page 69 and 70: CHAPTER 2System Bus InterfaceAPPEND

- Page 71 and 72: CHAPTER 2System Bus InterfaceAPPEND

- Page 73 and 74: CHAPTER 2System Bus InterfaceData i

- Page 76 and 77: CHAPTER 3Display Memory BusIn this

- Page 78 and 79: CHAPTER 3Display Memory BusTo minim

- Page 80 and 81: CHAPTER 3Display Memory BusAOOA"(7;

- Page 82 and 83: CHAPTER 3Display Memory BusFurtherm

- Page 84 and 85: CHAPTER 3Display Memory BusTo run t

- Page 86 and 87: CHAPTER 3Display Memory BusQPDM) as

- Page 88 and 89: CHAPTER 3Display Memory BusCDAT -0

- Page 90 and 91: CHAPTER 3Display Memory Busoutput b

- Page 92 and 93: CHAPTER 3Display Memory BusDIM qpar

- Page 94 and 95: CHAPTER 3Display Memory Busram.para

- Page 96 and 97: DATA 99,99,10,20,99,99,99,99,99,tw(

- Page 98 and 99: CHAPTER 3Display Memory BusDATA 5,-

- Page 100 and 101: CHAPTER 3Display Memory BusGOSUB fi

- Page 102 and 103: CHAPTER 3Display Memory Busramp=18:

- Page 104 and 105:

CHAPTER 3Display Memory BusGOSUB fi

- Page 106 and 107:

CHAPTER 3Display Memory Busramp=46:

- Page 108 and 109:

CHAPTER 3Display Memory Busparam69:

- Page 110 and 111:

amp=93 :GOSUB out.paramtext$="this

- Page 112 and 113:

CHAPTER 3Display Memory BusRETURNge

- Page 114 and 115:

CHAPTER 3Display Memory Bustext$="N

- Page 116 and 117:

CHAPTER 3Display Memory BusKANJI RO

- Page 118 and 119:

CHAPTER 3Display Memory BusTable 3.

- Page 120 and 121:

Al1 -1'01----.----------1lSI Level0

- Page 122:

CHAPTER 4Video Bus4.1 VIDEO BUS4.2

- Page 125 and 126:

CHAPTER 4Video Bus4.2.2 High-speed

- Page 127 and 128:

CHAPTER 4Video BusScan Line End Con

- Page 129 and 130:

CHAPTER 4Video BusFIFO (VDAF). The

- Page 131 and 132:

CHAPTER 4Video BusParameter min typ

- Page 134:

CHAPTER 5Evaluation and Demonstrati

- Page 137 and 138:

CHAPTER 5Evaluation and Demonstrati

- Page 139 and 140:

CHAPTER 5Evaluation and Demonstrati

- Page 141 and 142:

CHAPTER 5Evaluation and Demonstrati

- Page 143 and 144:

CHAPTER 5Evaluation and Demonstrati

- Page 145 and 146:

CHAPTERSEvaluation and Demonstratio

- Page 147 and 148:

CHAPTER 5Evaluation and Demonstrati

- Page 149 and 150:

CHAPTER 5Evaluatuion and Demonstrat

- Page 151 and 152:

CHAPTERSEvaluation and Demonstratio

- Page 153 and 154:

CHAPTERSEvaluation and Demonstratio

- Page 155 and 156:

CHAPTER 5Evaluation and Demonstrati

- Page 157 and 158:

CHAPTER 5Evaluation and Demonstrati

- Page 159 and 160:

C{I~P2-01 T22 T 22 TO. 1 41-44. 48-

- Page 161 and 162:

(JIN0>2D2PROM_(SA16: :~~~202

- Page 163 and 164:

(.TI~8A22828C26A7'A66A'6A37C77C6704

- Page 165 and 166:

c.nWo607, Be2 DClK2 » ============

- Page 168:

CHAPTER 6Articles/Application Notes

- Page 171 and 172:

CHAPTER 6Software10 'This programs

- Page 173 and 174:

CHAPTER 6Software950 RETURN960 '970

- Page 175 and 176:

CHAPTER 6Software6.2 COPY BLOCK OPE

- Page 177 and 178:

CHAPTER 6Software6.2.4 Transparency

- Page 179 and 180:

CHAPTER 6Softwarecpy 11 a [temp2] [

- Page 181 and 182:

CHAPTER 6Softwarecpy 11 a [temp2] [

- Page 183 and 184:

CHAPTER 6SoftwareADDTEMPblk [blksiz

- Page 185 and 186:

CHAPTER 6SoftWareSUBSTEMPblk [blksi

- Page 187 and 188:

NOTES

- Page 189 and 190:

NOTES

- Page 191 and 192:

NOTES

- Page 193:

ADVANCED MICRO DEVICES' NORTH AMERI