- Page 1:

z/OS UNIX System Services Command R

- Page 4 and 5:

Note Before using this information

- Page 6 and 7:

| | | | | | | | | clear — Clear t

- Page 8 and 9:

| | | paste — Merge corresponding

- Page 10 and 11:

| OCOPY — Copy an MVS data set me

- Page 12 and 13:

x z/OS V1R9.0 UNIX System Services

- Page 14 and 15:

xii z/OS V1R9.0 UNIX System Service

- Page 16 and 17:

xiv z/OS V1R9.0 UNIX System Service

- Page 18 and 19:

You can browse softcopy z/OS public

- Page 20 and 21:

v A CD-ROM in the z/OS Collection (

- Page 22 and 23:

uudecode uuencode The following deb

- Page 24 and 25:

c++ c89 cc mount pax ps multproc su

- Page 26 and 27:

[-k startpos[,endpos]] ... [file ..

- Page 28 and 29:

Trying the examples provided Before

- Page 30 and 31:

Usage notes Exit values Limits Port

- Page 32 and 33:

v Environment variables (DBCS chara

- Page 34 and 35:

When in the POSIX locale, DBCS stri

- Page 36 and 37:

alias Options To avoid using four b

- Page 38 and 39:

| | | alias Portability POSIX.2 Use

- Page 40 and 41:

ar Operands Examples archive Specif

- Page 42 and 43:

| | | | | | | | | | | | | as as —

- Page 44 and 45:

| | | | | | | | | | | | | | | | | |

- Page 46 and 47:

asa Localization Exit values Portab

- Page 48 and 49:

at hh:mmam Morning, 12-hour clock h

- Page 50 and 51:

| | | autoload See typeset — Assi

- Page 52 and 53:

automount name * type HFS filesyste

- Page 54 and 55:

automount 30 z/OS V1R9.0 UNIX Syste

- Page 56 and 57:

| | | automount v When allocation-s

- Page 58 and 59:

awk For a description of fields, se

- Page 60 and 61:

| | | | | | | | | | | | awk If two

- Page 62 and 63:

awk contains five fields, two of wh

- Page 64 and 65:

awk ampersand (&) in repl with the

- Page 66 and 67:

| | | | | | | | | | | | awk Actions

- Page 68 and 69:

awk {print NR ":" $0} 3. The follow

- Page 70 and 71:

| | | awk close(string) return ($2)

- Page 72 and 73:

awk Portability The parser stack de

- Page 74 and 75:

| | | batch Exit Values Portability

- Page 76 and 77:

c v A function is a sequence of ins

- Page 78 and 79:

c Arithmetic Operations bc provides

- Page 80 and 81:

c A || B Is true if A is true or B

- Page 82 and 83:

c if (a

- Page 84 and 85:

c Each parameter on the first line

- Page 86 and 87:

| | | | bc Examples a full name, an

- Page 88 and 89:

| | bc Usage notes Files Localizati

- Page 90 and 91:

g bg — Move a job to the backgrou

- Page 92 and 93:

| | | | | break Usage Note Exit Val

- Page 94 and 95:

c89, cc, and c++ Options utilities.

- Page 96 and 97:

c89, cc, and c++ hexadecimal format

- Page 98 and 99:

c89, cc, and c++ You can specify an

- Page 100 and 101:

c89, cc, and c++ acceptable to have

- Page 102 and 103:

c89, cc, and c++ 78 z/OS V1R9.0 UNI

- Page 104 and 105:

c89, cc, and c++ passing function c

- Page 106 and 107:

c89, cc, and c++ be a C370LIB objec

- Page 108 and 109:

c89, cc, and c++ Environment variab

- Page 110 and 111:

c89, cc, and c++ c89/cc/c++ environ

- Page 112 and 113:

c89, cc, and c++ of record format u

- Page 114 and 115:

c89, cc, and c++ the IPA Link step

- Page 116 and 117:

c89, cc, and c++ prefix_NEW_DATACLA

- Page 118 and 119:

c89, cc, and c++ The following data

- Page 120 and 121:

c89, cc, and c++ normally used by c

- Page 122 and 123:

c89, cc, and c++ escaped. For examp

- Page 124 and 125:

c89, cc, and c++ to specify a libra

- Page 126 and 127:

c89, cc, and c++ prefix_ILSYSLIB pr

- Page 128 and 129:

| | | | | | | | | c89, cc, and c++

- Page 130 and 131:

cal Localization Usage Note Exit Va

- Page 132 and 133:

calendar Related Information mailx

- Page 134 and 135:

captoinfo Related Information infoc

- Page 136 and 137:

cd In the shell, the command cd - i

- Page 138 and 139:

| | | | | | | | | | | | | | | | | |

- Page 140 and 141:

| | | | | | | | | | | | | | | | | |

- Page 142 and 143:

chaudit Examples Localization Exit

- Page 144 and 145:

chcp Examples Usage notes You get t

- Page 146 and 147:

chgrp Description Options Localizat

- Page 148 and 149:

chlabel Exit Values Examples 0 Succ

- Page 150 and 151:

chmod Examples If the RACF profile

- Page 152 and 153:

chmount Options Example Usage Note

- Page 154 and 155:

chown Localization Exit Values Mess

- Page 156 and 157:

chroot Exit Values Given the standa

- Page 158 and 159:

chtag Examples Usage notes Note: Co

- Page 160 and 161:

cksum File Tag Specific Options Loc

- Page 162 and 163:

cmp File Tag Specific Options Local

- Page 164 and 165:

col Usage notes Exit Values Portabi

- Page 166 and 167:

comm Portability Related Informatio

- Page 168 and 169:

compress Options Localization Exit

- Page 170 and 171:

confighfs Examples Usage notes -v n

- Page 172 and 173:

configstk Examples number specified

- Page 174 and 175:

configstrm Usage notes Example -u l

- Page 176 and 177:

| copytree Exit Values Related info

- Page 178 and 179:

cp cr carriage return lf line feed

- Page 180 and 181:

cp SPACE=(500,(100,500)) units, pri

- Page 182 and 183:

cp Table 6. Automatic conversion an

- Page 184 and 185:

cp 1. If an UNIX file does not exis

- Page 186 and 187:

cp Usage notes Table 10. cp Format:

- Page 188 and 189:

| | | | cp Localization Exit Values

- Page 190 and 191:

cpio Patterns are the same as those

- Page 192 and 193:

cpio Localization Exit Values Porta

- Page 194 and 195:

cron daemon Files If these files do

- Page 196 and 197:

crontab Options 0 0 * * * -- Midnig

- Page 198 and 199:

csplit Options -A Uses uppercase le

- Page 200 and 201:

csplit Related Information awk, sed

- Page 202 and 203:

cu Description Note: The cu utility

- Page 204 and 205:

| | | | | | cxx cxx — Compile, li

- Page 206 and 207:

date Example %OW The week number of

- Page 208 and 209:

| | | dbx Attach-types Options this

- Page 210 and 211:

| | | | | | | | | | | | | | | | | |

- Page 212 and 213:

| | | | | | | | | | | dbx dbx subco

- Page 214 and 215:

dbx: alias alias stopf(file, line)

- Page 216 and 217:

dbx: clear clear subcommand for dbx

- Page 218 and 219:

| | dbx: cont Usage Note The cont s

- Page 220 and 221:

| | | | | | | | | | | | | | | | | |

- Page 222 and 223:

| | | dbx: dump Option >file dump o

- Page 224 and 225:

dbx: gotoi gotoi subcommand for dbx

- Page 226 and 227:

dbx: list All lines from the first

- Page 228 and 229:

dbx: listi Examples 1. To list the

- Page 230 and 231:

dbx: mutex mutex subcommand for dbx

- Page 232 and 233:

| | | dbx: object Usage Note v The

- Page 234 and 235:

| dbx: pluginunload See the plugin

- Page 236 and 237:

dbx: readwritelock readwritelock ho

- Page 238 and 239:

| | | | dbx: return Examples 1. To

- Page 240 and 241:

dbx: set $frame Uses the stack fram

- Page 242 and 243:

dbx: set $r General register. $repe

- Page 244 and 245:

dbx: source Description The source

- Page 246 and 247:

| | | | | | dbx: stop Options at [

- Page 248 and 249:

dbx: thread 5. To display all threa

- Page 250 and 251:

dbx: tracei 3. To trace each time t

- Page 252 and 253:

dbx: whatis Usage notes 1. Variable

- Page 254 and 255:

dd Options 2. If this input block i

- Page 256 and 257:

dd Example ibs=size Sets the input

- Page 258 and 259:

df Options Space Free Total amount

- Page 260 and 261:

diff Description Options The diff c

- Page 262 and 263:

diff Localization results in the fo

- Page 264 and 265:

diff Limits Portability Related Inf

- Page 266 and 267:

. (dot) . (dot) — Run a shell fil

- Page 268 and 269:

dspmsg Options Examples default mes

- Page 270 and 271:

echo Description Examples Usage Not

- Page 272 and 273:

| ed need to specify addresses for

- Page 274 and 275:

| | | | | | | | | | | | | | | | | |

- Page 276 and 277:

| | | | | | | | ed the current line

- Page 278 and 279:

ed Exit Values Messages v LC_SYNTAX

- Page 280 and 281:

| | | | | | | | | | | | | | | | | |

- Page 282 and 283:

env Exit Values Portability v NLSPA

- Page 284 and 285:

ex Localization Portability Related

- Page 286 and 287:

exit exit — Return to the shell

- Page 288 and 289:

expand Related Information pr, unex

- Page 290 and 291:

expr Option Usage Note Examples Loc

- Page 292 and 293:

exrecover daemon Localization Files

- Page 294 and 295:

exrecover daemon Exit Values Relate

- Page 296 and 297:

exrecover daemon Related Informatio

- Page 298 and 299:

fc the one indicated by first throu

- Page 300 and 301:

| | | | | | | | | | | | | fg Exit V

- Page 302 and 303:

| | | | | | | | | | | | | | | | | |

- Page 304 and 305:

| | | | | | | | | | | | | | | | | |

- Page 306 and 307:

find Options number noted in the pr

- Page 308 and 309:

| | | | | | | | | | | | | | find nu

- Page 310 and 311:

find -newer file Compares the modif

- Page 312 and 313:

find Localization Exit Values 8. To

- Page 314 and 315:

fold Localization Exit Values Porta

- Page 316 and 317:

fuser Exit Values or Related Inform

- Page 318 and 319:

gencat Description Sequence Vertica

- Page 320 and 321:

getconf _POSIX_VDISABLE Specifies t

- Page 322 and 323:

getconf POSIX2_LOCALEDEF Indicates

- Page 324 and 325:

getfacl Options Examples -a Display

- Page 326 and 327:

getopts Example script recognizes -

- Page 328 and 329:

grep Options egrep works in a simil

- Page 330 and 331:

grep Portability Related Informatio

- Page 332 and 333:

head Messages Portability Related I

- Page 334 and 335:

iconv Options Localization Examples

- Page 336 and 337:

id Options Localization Example Usa

- Page 338 and 339:

inetd daemon Usage notes 1. Buffer

- Page 340 and 341:

infocmp Options Usage notes Example

- Page 342 and 343:

infocmp :co#80:\ :li#24:\ :kn#2:\ :

- Page 344 and 345:

ipcrm Options Examples Exit Values

- Page 346 and 347:

ipcs Table 14. Explanation of the i

- Page 348 and 349:

ipcs Table 14. Explanation of the i

- Page 350 and 351:

ipcs Examples -t v Time of the last

- Page 352 and 353:

jobs Options Localization Usage Not

- Page 354 and 355:

join Localization Exit Values Messa

- Page 356 and 357:

kill Options 7 SIGSTOP 8 SIGFPE 9 S

- Page 358 and 359:

kill Related Information jobs, ps,

- Page 360 and 361:

ld be a C370LIB object library or a

- Page 362 and 363:

ld _LD_LIBDIRS_ The directories use

- Page 364 and 365:

ld -u _LD_EXTRA_SYMBOL CEEMAIN or,

- Page 366 and 367:

ld Localization Exit values Related

- Page 368 and 369: lex Options For a description of th

- Page 370 and 371: lex Limits Portability Related Info

- Page 372 and 373: link Related Information link, ln,

- Page 374 and 375: ln Localization Exit Values 2. spaw

- Page 376 and 377: locale Description Options locale d

- Page 378 and 379: locale nonnegative formatted moneta

- Page 380 and 381: locale Portability Related Informat

- Page 382 and 383: localedef Related Information local

- Page 384 and 385: logger Portability POSIX.2, X/Open

- Page 386 and 387: lp Environment Variables lp uses th

- Page 388 and 389: ls -H Displays file formats for reg

- Page 390 and 391: ls r Permission to read the file w

- Page 392 and 393: ls Localization Exit Values Message

- Page 394 and 395: mail Sending Mail Example Usage not

- Page 396 and 397: mailx Description Options mailx hel

- Page 398 and 399: | | | mailx recipient’s home dire

- Page 400 and 401: | | | | | | | | | | | | | | | | | |

- Page 402 and 403: | | | | | | | | | | | | | | | | | |

- Page 404 and 405: | | | | | | | | | | | | | | | | | |

- Page 406 and 407: | | | | | | | | | | | | | | | | | |

- Page 408 and 409: | mailx Startup Files ~< !command R

- Page 410 and 411: | | | | | | | | | | | | | | | | | |

- Page 412 and 413: | | | | | | | | | | | | | | mailx s

- Page 414 and 415: mailx Files Localization mail. The

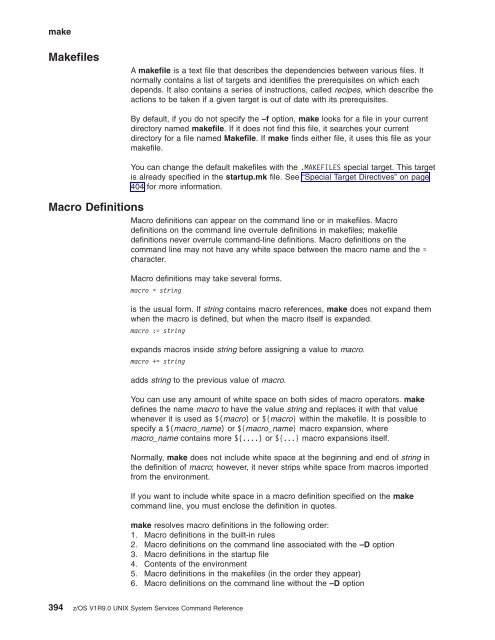

- Page 416 and 417: make Options -c dir Attempts to cha

- Page 420 and 421: make Usage Note to the full name of

- Page 422 and 423: make targets :- prereqs Clears the

- Page 424 and 425: make and: %.c : %.y ... rule body .

- Page 426 and 427: make 1. Extract the suffix from the

- Page 428 and 429: make Special Target Directives Spec

- Page 430 and 431: make .NOAUTODEPEND Disables the aut

- Page 432 and 433: make Options in the MAKEFLAGS envir

- Page 434 and 435: make Files make uses the following

- Page 436 and 437: make Limits Usage notes Portability

- Page 438 and 439: makedepend Options -S directory Spe

- Page 440 and 441: makedepend The following options co

- Page 442 and 443: makedepend Environment variables ma

- Page 444 and 445: | makedepend Exit values 3. For opt

- Page 446 and 447: | | | man Environment Variables man

- Page 448 and 449: mesg Related Information talk, writ

- Page 450 and 451: mkdir Description Options Localizat

- Page 452 and 453: | | | | | | | mkfifo Localization E

- Page 454 and 455: more Options more allows paging for

- Page 456 and 457: more [n]?[!]pattern Searches backwa

- Page 458 and 459: mount Options -a yes|include,sysnam

- Page 460 and 461: mount Usage notes 2. To mount an HF

- Page 462 and 463: mv Options When moving records, the

- Page 464 and 465: mv Removes the specifed suffix from

- Page 466 and 467: mv Table 16. Automatic conversion a

- Page 468 and 469:

mv 3. If you specify a UNIX file as

- Page 470 and 471:

mv Table 19. mv Format: File to Fil

- Page 472 and 473:

mv Examples 11. If a file is a symb

- Page 474 and 475:

mv Portability Related Information

- Page 476 and 477:

newgrp Portability Related Informat

- Page 478 and 479:

nl Example Localization Messages Po

- Page 480 and 481:

nm -M Inserts three columns in the

- Page 482 and 483:

nohup Localization Exit Values Port

- Page 484 and 485:

| | | | | | | | | | | | | | od Opti

- Page 486 and 487:

| | | od LL Corresponds to the numb

- Page 488 and 489:

oedit Option Usage notes Environmen

- Page 490 and 491:

pack Localization Exit Values Porta

- Page 492 and 493:

paste Options Examples Localization

- Page 494 and 495:

patch same file, patch only creates

- Page 496 and 497:

patch Localization Exit Values Port

- Page 498 and 499:

pax Description Note APAR OW52499 (

- Page 500 and 501:

pax Patterns Options Command-line p

- Page 502 and 503:

pax Rule: Specifying more than one

- Page 504 and 505:

pax If you do not specify -o, no co

- Page 506 and 507:

pax 482 z/OS V1R9.0 UNIX System Ser

- Page 508 and 509:

pax and have specified the correspo

- Page 510 and 511:

pax On UNIX and POSIX-compliant sys

- Page 512 and 513:

| pax handled by any other format s

- Page 514 and 515:

pax Output Usage notes the source f

- Page 516 and 517:

pax Table 26. Charset standards (co

- Page 518 and 519:

pax d[efault] If specified, extende

- Page 520 and 521:

pax not Not specified bin Binary da

- Page 522 and 523:

| | | pax The values for all the ke

- Page 524 and 525:

pax The -o noext option is the defa

- Page 526 and 527:

pax pax -ofrom=ISO8859-1,to=IBM-104

- Page 528 and 529:

pax Portability POSIX.2, X/Open Por

- Page 530 and 531:

pg Commands This is described in Ap

- Page 532 and 533:

pg $TMPDIR/pg* Temporary files to a

- Page 534 and 535:

pr Files default for n is 5. The ch

- Page 536 and 537:

print Usage Note Localization Exit

- Page 538 and 539:

printf printf — Write formatted o

- Page 540 and 541:

printf Related Information echo, pr

- Page 542 and 543:

ps Format Specifications Using the

- Page 544 and 545:

ps ruser Displays the real user ID

- Page 546 and 547:

ps the four byte value determined w

- Page 548 and 549:

pwd Localization Exit Values Portab

- Page 550 and 551:

ead Localization Usage Note Exit Va

- Page 552 and 553:

enice Options Localization Exit Val

- Page 554 and 555:

logind Options Note rlogind should

- Page 556 and 557:

m Options Localization Exit Values

- Page 558 and 559:

| | runcat runcat — Pipe output f

- Page 560 and 561:

| | | | sed _UNIX03=YES is set, one

- Page 562 and 563:

| | | | | | | sed Example If the va

- Page 564 and 565:

sed Related Information awk, diff,

- Page 566 and 567:

set ignoreeof Tells the shell not t

- Page 568 and 569:

set Portability POSIX.2, X/Open Por

- Page 570 and 571:

setfacl 2. The user tried to change

- Page 572 and 573:

setfacl Localization Exit Values Po

- Page 574 and 575:

sh Options and runs this file with

- Page 576 and 577:

sh and this second shell actually r

- Page 578 and 579:

sh -o option True if shell option i

- Page 580 and 581:

sh current ERR and EXIT traps, as w

- Page 582 and 583:

sh Quoting found only in FPATH, thi

- Page 584 and 585:

sh Variables are named parameters.F

- Page 586 and 587:

sh ${parameter:+word} Expands to wo

- Page 588 and 589:

sh $(command) as in: ed $(grep -f -

- Page 590 and 591:

sh number&− Closes output descrip

- Page 592 and 593:

| | | | sh shell environment starts

- Page 594 and 595:

sh Note: Shell variables that are e

- Page 596 and 597:

sh Table 28. Built-in Shell Variabl

- Page 598 and 599:

sh Files Table 29. Shell Variables

- Page 600 and 601:

sh Hangup The shell received a hang

- Page 602 and 603:

shedit A command line that extends

- Page 604 and 605:

shedit Meta-* Replaces the current

- Page 606 and 607:

shedit ?stringEnter Selects the fir

- Page 608 and 609:

shift Description Examples Usage No

- Page 610 and 611:

skulker Description Options skulker

- Page 612 and 613:

skulker Exit Values Messages 0 Succ

- Page 614 and 615:

sort Sorting Keys By default, sort

- Page 616 and 617:

sort Localization Exit Values Messa

- Page 618 and 619:

spell spell — Detect spelling err

- Page 620 and 621:

spell Limits Portability Related In

- Page 622 and 623:

stop that may be specified as octal

- Page 624 and 625:

strip Localization Exit Values Mess

- Page 626 and 627:

stty hup Hang up the modem line on

- Page 628 and 629:

stty ofill Use fill characters for

- Page 630 and 631:

stty Usage notes Localization evenp

- Page 632 and 633:

su v Changes the group ID. If a use

- Page 634 and 635:

su Exit Values Messages Limits Port

- Page 636 and 637:

sum Exit Values Portability See App

- Page 638 and 639:

tabs which case the number is consi

- Page 640 and 641:

tail Localization Exit Values Messa

- Page 642 and 643:

talk Exit Values Portability 3. The

- Page 644 and 645:

tar Rules : You cannot specify both

- Page 646 and 647:

tar Output Tip : If -O is specified

- Page 648 and 649:

tar Usage notes Archive Listing (Ta

- Page 650 and 651:

tar Portability 4.2BSD Related info

- Page 652 and 653:

tcsh -n Parses commands but does no

- Page 654 and 655:

tcsh A filename to be completed can

- Page 656 and 657:

tcsh entire input buffer with spell

- Page 658 and 659:

tcsh i-search-back (not bound) Sear

- Page 660 and 661:

tcsh up-history (up-arrow, ^P) Copi

- Page 662 and 663:

tcsh # The current event. This shou

- Page 664 and 665:

tcsh password″ rot with !:s/rot/r

- Page 666 and 667:

tcsh modifier is applied to a subst

- Page 668 and 669:

tcsh /usr/source/s1/ls.c. The resul

- Page 670 and 671:

tcsh Input or output The standard i

- Page 672 and 673:

tcsh fail, returning false (0). If

- Page 674 and 675:

tcsh Jobs Only one of these operato

- Page 676 and 677:

tcsh v The autologout shell variabl

- Page 678 and 679:

tcsh This will put the hostname and

- Page 680 and 681:

tcsh The shell synchronizes group,

- Page 682 and 683:

tcsh Table 32. tcsh Built-in Shell

- Page 684 and 685:

tcsh Table 32. tcsh Built-in Shell

- Page 686 and 687:

tcsh Table 32. tcsh Built-in Shell

- Page 688 and 689:

tcsh Table 32. tcsh Built-in Shell

- Page 690 and 691:

tcsh represented by ~ and other use

- Page 692 and 693:

tcsh here’s the behavior with sym

- Page 694 and 695:

| tcsh Table 33. tcsh Environment V

- Page 696 and 697:

tcsh Commands within loops are not

- Page 698 and 699:

tcsh: % (percent) v % job & will mo

- Page 700 and 701:

tcsh: bye bye built-in command for

- Page 702 and 703:

tcsh: complete This completion comp

- Page 704 and 705:

tcsh: dirs Description dirs used al

- Page 706 and 707:

tcsh: glob Description glob is like

- Page 708 and 709:

tcsh: limit hours, or a time of the

- Page 710 and 711:

tcsh: lsF See “tcsh — Invoke a

- Page 712 and 713:

tcsh: pushd -v Entries are printed

- Page 714 and 715:

tcsh: setty setty built-in command

- Page 716 and 717:

tcsh: unsetenv Description unsetenv

- Page 718 and 719:

test Description test checks for va

- Page 720 and 721:

test Usage notes Examples expr1 -o

- Page 722 and 723:

tic Example -c Specifies that the i

- Page 724 and 725:

times Option Usage Note Localizatio

- Page 726 and 727:

touch Localization Exit Values Mess

- Page 728 and 729:

| | | | | | | | | | | | tput Exit V

- Page 730 and 731:

| | | | | | | | | | | | | | | | | |

- Page 732 and 733:

trap Usage Note Examples Localizati

- Page 734 and 735:

tso Examples a mini-TSO/E environme

- Page 736 and 737:

tso export TSOPROFILE="prefix(wjs)

- Page 738 and 739:

tsort tsort — Sort files topologi

- Page 740 and 741:

type Exit Values Messages Portabili

- Page 742 and 743:

typeset Localization Exit Values Me

- Page 744 and 745:

| ulimit Usage notes Localization d

- Page 746 and 747:

umask Exit Values Portability v LC_

- Page 748 and 749:

uname Localization Usage Note Exit

- Page 750 and 751:

unexpand Options Localization Exit

- Page 752 and 753:

uniq Messages Portability Related I

- Page 754 and 755:

unmount Examples Usage notes codes.

- Page 756 and 757:

unpack File Exit Values Messages Po

- Page 758 and 759:

uptime uptime — Report how long t

- Page 760 and 761:

uucico daemon Options Examples File

- Page 762 and 763:

uucp Options v A pathname preceded

- Page 764 and 765:

uucp uucp remote!/tmp/file?.[!b]* /

- Page 766 and 767:

| | | | | | | | | | | | | | | | | |

- Page 768 and 769:

uuencode Localization Exit Values P

- Page 770 and 771:

uuname uuname — Display list of r

- Page 772 and 773:

uupick Localization Files Usage not

- Page 774 and 775:

uustat Examples rtype The request t

- Page 776 and 777:

uuto Description Options Localizati

- Page 778 and 779:

uux Options Unlike arguments to uuc

- Page 780 and 781:

uux Exit Values Portability Related

- Page 782 and 783:

uuxqt daemon Related Information uu

- Page 784 and 785:

vi These lines are not part of the

- Page 786 and 787:

vi m Records the current position p

- Page 788 and 789:

vi with a form feed (Ctrl-L), start

- Page 790 and 791:

vi same manner as the ex system com

- Page 792 and 793:

vi Ctrl-G Displays the current path

- Page 794 and 795:

vi command The command is a word, w

- Page 796 and 797:

vi arguments for the ab command, it

- Page 798 and 799:

vi [.,.] l[ist] [count] [flags] Dis

- Page 800 and 801:

vi so[urce] file Runs editor comman

- Page 802 and 803:

vi (^), the editor displays the scr

- Page 804 and 805:

vi autoindent, ai When autoindent i

- Page 806 and 807:

vi in the list are paragraph bounda

- Page 808 and 809:

vi wrapscan, ws If this option is o

- Page 810 and 811:

vi Localization Exit Values vi uses

- Page 812 and 813:

vi Related Information ed, ex, fg,

- Page 814 and 815:

wc Localization Exit Values Portabi

- Page 816 and 817:

who Files Localization Exit Values

- Page 818 and 819:

write Usage notes Localization Exit

- Page 820 and 821:

| writedown Examples 1 Failure due

- Page 822 and 823:

xlc and xlC The various compiler in

- Page 824 and 825:

xlc and xlC Setting up a configurat

- Page 826 and 827:

| | | | | | | | xlc and xlC CEE.SCE

- Page 828 and 829:

| | | | xlc and xlC 1. search place

- Page 830 and 831:

xlc and xlC * 64 bit ANSI C++ compi

- Page 832 and 833:

xlc and xlC principle, as both can

- Page 834 and 835:

xlc and xlC 5. -Bprefix and -tprogr

- Page 836 and 837:

xlc and xlC Note: When used in the

- Page 838 and 839:

xlc and xlC xlc -qipa=level=2:map:n

- Page 840 and 841:

| xargs xargs — Construct an argu

- Page 842 and 843:

xargs Example If no command templat

- Page 844 and 845:

yacc Options -b file_prefix Uses fi

- Page 846 and 847:

yacc Messages v Bad %start construc

- Page 848 and 849:

zcat Localization Exit Values Porta

- Page 850 and 851:

BPXBATCH BPXBATCH — Run shell com

- Page 852 and 853:

BPXBATCH Examples When PGM and prog

- Page 854 and 855:

MKDIR Return Codes Examples The def

- Page 856 and 857:

| | | | MOUNT MOUNT — Logically m

- Page 858 and 859:

| | | | | | | MOUNT file is sparse

- Page 860 and 861:

MOUNT Usage notes AUTOMOVE(EXCLUDE,

- Page 862 and 863:

MOUNT Return codes Examples As stat

- Page 864 and 865:

OCOPY Parameters v A file to an MVS

- Page 866 and 867:

OCOPY Usage notes TO1047 | FROM1047

- Page 868 and 869:

OCOPY PATHMODE (sirwxu) PATHOPTS (o

- Page 870 and 871:

OGET v A fully qualified name that

- Page 872 and 873:

OGET Return codes Examples 4. An ex

- Page 874 and 875:

OGETX example, doublebyte character

- Page 876 and 877:

OGETX Examples For OGETX to treat t

- Page 878 and 879:

OMVS Description Parameters RUNOPTS

- Page 880 and 881:

OMVS Table 37. Locales, Their Conve

- Page 882 and 883:

OMVS In general, the provider of th

- Page 884 and 885:

OMVS scrolled off the screen. If yo

- Page 886 and 887:

OMVS PF16(TOP) PF17(BOTTOM) PF18(TS

- Page 888 and 889:

OMVS HALFSCR Scrolls half the displ

- Page 890 and 891:

OPUT OPUT — Copy an MVS data set

- Page 892 and 893:

OPUT Return codes Examples the modu

- Page 894 and 895:

OPUTX v data_set_name(member_name).

- Page 896 and 897:

OSHELL Description OSHELL uses BPXB

- Page 898 and 899:

UNMOUNT Parameters FILESYSTEM(file_

- Page 900 and 901:

UNMOUNT Examples 1. The following c

- Page 902 and 903:

history — — Process a command h

- Page 904 and 905:

strings POSIX.2 XPG4.2 Display prin

- Page 906 and 907:

cpio — XPG4.2 Copy in/out file ar

- Page 908 and 909:

watchlog — — Report on users wh

- Page 910 and 911:

egexp that collation sequence). Any

- Page 912 and 913:

egexp Summary Examples The commands

- Page 914 and 915:

egexp 890 z/OS V1R9.0 UNIX System S

- Page 916 and 917:

BPXBATCH Format Description Any oth

- Page 918 and 919:

BPXBATCH Usage notes and exec. BPXB

- Page 920 and 921:

BPXBATCH The stdparm DD will allow

- Page 922 and 923:

BPXBATCH Files _BPX_BATCH_SPAWN cau

- Page 924 and 925:

BPXBATCH 900 z/OS V1R9.0 UNIX Syste

- Page 926 and 927:

| | | BPXCOPY Parameters v The mess

- Page 928 and 929:

BPXCOPY Specifying APF or NOAPF is

- Page 930 and 931:

BPXCOPY * ST 10,8(13) ST 13,SAVEARE

- Page 932 and 933:

Localization blank) and their behav

- Page 934 and 935:

910 z/OS V1R9.0 UNIX System Service

- Page 936 and 937:

| cpio After the header information

- Page 938 and 939:

| | | | | | | | | | | | | | | | | |

- Page 940 and 941:

pax pax interchange format # The pu

- Page 942 and 943:

pax pax extended header regular fil

- Page 944 and 945:

pax linkpath The pathname of a link

- Page 946 and 947:

queuedefs This file indicates that

- Page 948 and 949:

tar Description of the Header Files

- Page 950 and 951:

uucp All three files are stored in

- Page 952 and 953:

uucp Execute Files Execute files ar

- Page 954 and 955:

uucp 930 z/OS V1R9.0 UNIX System Se

- Page 956 and 957:

TZ Environment Variable Portability

- Page 958 and 959:

Environment Variables 934 z/OS V1R9

- Page 960 and 961:

MVS data sets 936 z/OS V1R9.0 UNIX

- Page 962 and 963:

Table 45. Commands that Disallow Au

- Page 964 and 965:

dbx: threads threads: Thread Displa

- Page 966 and 967:

| | | | | dbx: variables $hexchars

- Page 968 and 969:

| | | | | | | | | | | | | | | | | |

- Page 970 and 971:

946 z/OS V1R9.0 UNIX System Service

- Page 972 and 973:

948 z/OS V1R9.0 UNIX System Service

- Page 974 and 975:

Licensees of this program who wish

- Page 976 and 977:

952 z/OS V1R9.0 UNIX System Service

- Page 978 and 979:

usr/lib/cron/queuedefs file used by

- Page 980 and 981:

argument (continued) printing 511 r

- Page 982 and 983:

yte count (continued) displaying wi

- Page 984 and 985:

clone output streams 693 close 566

- Page 986 and 987:

copy (continued) MVS data sets memb

- Page 988 and 989:

detect aliases 722 spelling errors

- Page 990 and 991:

EDITOR environment variable descrip

- Page 992 and 993:

environment variable (continued) _P

- Page 994 and 995:

environment variable (continued) PW

- Page 996 and 997:

file (continued) comparing two (con

- Page 998 and 999:

files (continued) /tmp/VIn* used by

- Page 1000 and 1001:

FWDRETR function key for OMVS comma

- Page 1002 and 1003:

IPA (Interprocedural Analysis) opti

- Page 1004 and 1005:

M MACHTYPE tcsh environment variabl

- Page 1006 and 1007:

NOSHAREAS option of OMVS command 86

- Page 1008 and 1009:

process (continued) returning (cont

- Page 1010 and 1011:

eset access time 166 Resource Acces

- Page 1012 and 1013:

shell (continued) evaluating argume

- Page 1014 and 1015:

standard error (stderr) allocating

- Page 1016 and 1017:

tcsh environment variable (continue

- Page 1018 and 1019:

term tcsh shell variable descriptio

- Page 1020 and 1021:

user ID changing to superuser 607 u

- Page 1022 and 1023:

Y y.output file used by yacc 821 y.

- Page 1024:

Readers’ Comments — We’d Like