LOGIC DESIGN LABORATORY MANUAL - VTU e-Learning Centre

LOGIC DESIGN LABORATORY MANUAL - VTU e-Learning Centre

LOGIC DESIGN LABORATORY MANUAL - VTU e-Learning Centre

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Logic Design Laboratory Manual 4<br />

___________________________________________________________________________<br />

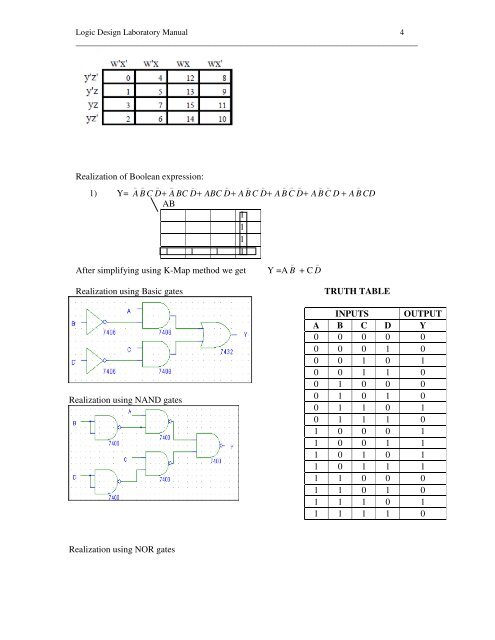

Realization of Boolean expression:<br />

_<br />

_<br />

_<br />

_<br />

_<br />

_<br />

1) Y= A B C D+<br />

A BC D+<br />

ABC D+<br />

A B C D+<br />

A B C D+<br />

A B C D + A B CD<br />

AB<br />

1<br />

1<br />

1<br />

1 1 1 1<br />

_<br />

_<br />

_<br />

_<br />

_<br />

_<br />

_<br />

_<br />

After simplifying using K-Map method we get<br />

Y =A _ B + C _ D<br />

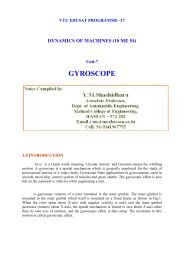

Realization using Basic gates<br />

Realization using NAND gates<br />

TRUTH TABLE<br />

INPUTS OUTPUT<br />

A B C D Y<br />

0 0 0 0 0<br />

0 0 0 1 0<br />

0 0 1 0 1<br />

0 0 1 1 0<br />

0 1 0 0 0<br />

0 1 0 1 0<br />

0 1 1 0 1<br />

0 1 1 1 0<br />

1 0 0 0 1<br />

1 0 0 1 1<br />

1 0 1 0 1<br />

1 0 1 1 1<br />

1 1 0 0 0<br />

1 1 0 1 0<br />

1 1 1 0 1<br />

1 1 1 1 0<br />

Realization using NOR gates