Synchronous Latency Insensitive Design - ICS

Synchronous Latency Insensitive Design - ICS

Synchronous Latency Insensitive Design - ICS

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

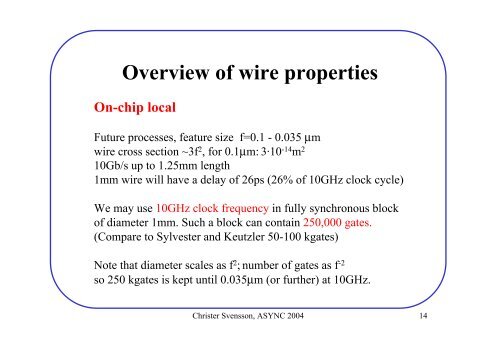

Overview of wire properties<br />

On-chip local<br />

Future processes, feature size f=0.1 - 0.035 µm<br />

wire cross section ~3f 2 , for 0.1µm: 3·10 -14 m 2<br />

10Gb/s up to 1.25mm length<br />

1mm wire will have a delay of 26ps (26% of 10GHz clock cycle)<br />

We may use 10GHz clock frequency in fully synchronous block<br />

of diameter 1mm. Such a block can contain 250,000 gates.<br />

(Compare to Sylvester and Keutzler 50-100 kgates)<br />

Note that diameter scales as f 2 ; number of gates as f -2<br />

so 250 kgates is kept until 0.035µm (or further) at 10GHz.<br />

Christer Svensson, ASYNC 2004 14