cmd6686gx manual - RTD Embedded Technologies, Inc.

cmd6686gx manual - RTD Embedded Technologies, Inc.

cmd6686gx manual - RTD Embedded Technologies, Inc.

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

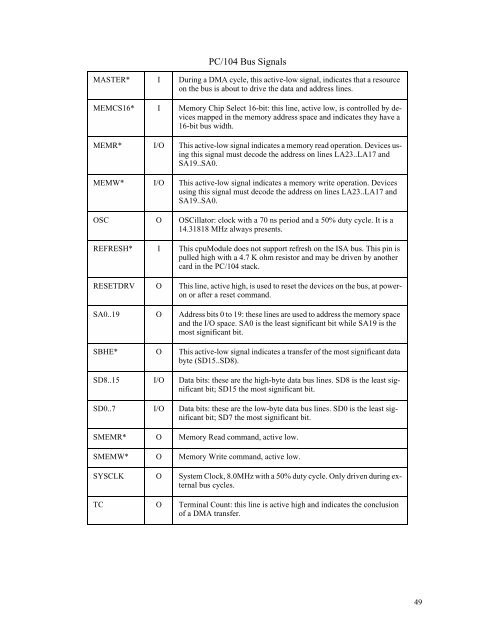

PC/104 Bus Signals<br />

MASTER* I During a DMA cycle, this active-low signal, indicates that a resource<br />

on the bus is about to drive the data and address lines.<br />

MEMCS16* I Memory Chip Select 16-bit: this line, active low, is controlled by devices<br />

mapped in the memory address space and indicates they have a<br />

16-bit bus width.<br />

MEMR* I/O This active-low signal indicates a memory read operation. Devices using<br />

this signal must decode the address on lines LA23..LA17 and<br />

SA19..SA0.<br />

MEMW* I/O This active-low signal indicates a memory write operation. Devices<br />

using this signal must decode the address on lines LA23..LA17 and<br />

SA19..SA0.<br />

OSC O OSCillator: clock with a 70 ns period and a 50% duty cycle. It is a<br />

14.31818 MHz always presents.<br />

REFRESH* I This cpuModule does not support refresh on the ISA bus. This pin is<br />

pulled high with a 4.7 K ohm resistor and may be driven by another<br />

card in the PC/104 stack.<br />

RESETDRV O This line, active high, is used to reset the devices on the bus, at poweron<br />

or after a reset command.<br />

SA0..19 O Address bits 0 to 19: these lines are used to address the memory space<br />

and the I/O space. SA0 is the least significant bit while SA19 is the<br />

most significant bit.<br />

SBHE* O This active-low signal indicates a transfer of the most significant data<br />

byte (SD15..SD8).<br />

SD8..15 I/O Data bits: these are the high-byte data bus lines. SD8 is the least significant<br />

bit; SD15 the most significant bit.<br />

SD0..7 I/O Data bits: these are the low-byte data bus lines. SD0 is the least significant<br />

bit; SD7 the most significant bit.<br />

SMEMR* O Memory Read command, active low.<br />

SMEMW* O Memory Write command, active low.<br />

SYSCLK O System Clock, 8.0MHz with a 50% duty cycle. Only driven during external<br />

bus cycles.<br />

TC O Terminal Count: this line is active high and indicates the conclusion<br />

of a DMA transfer.<br />

49