- Page 1 and 2:

Page | 1 Lecture Notes for Computer

- Page 3 and 4:

knowledge given in the book chapter

- Page 5 and 6:

CS 320 SCHEDULE (tentative) Week Wh

- Page 7 and 8:

6. Project reports - Presentation C

- Page 9 and 10:

9. Course policies: 1) Satisfactory

- Page 11 and 12:

Size - keep shrinking 1994 124mm 2

- Page 13 and 14:

Families of different models - Inte

- Page 15 and 16:

Super Computers CRAY - 1 st vector

- Page 17 and 18:

Fastest super computers November 20

- Page 19 and 20:

Class Activity - 2. Trace the conte

- Page 21 and 22:

TUTOR 1.32:> PHYSICAL ADDRESS=00002

- Page 23 and 24:

TUTOR 1.32:> PHYSICAL ADDRESS=00002

- Page 25 and 26:

Class Activity 3 - Study of instruc

- Page 27 and 28:

Class Activity 4 - Study of instruc

- Page 29 and 30:

TUTOR 1.32:> PHYSICAL ADDRESS=00002

- Page 31 and 32:

TUTOR 1.32:> PHYSICAL ADDRESS=00004

- Page 33 and 34:

Performance Improvement at Instruct

- Page 35 and 36:

5. Register indirect addressing mod

- Page 37 and 38:

High Level Language Statements Ass

- Page 39 and 40:

Lecture 7 Data transfer memory reg

- Page 41 and 42:

Problem Translate HLL statement A[

- Page 43 and 44:

More MIPS instructions jump j jr $S

- Page 45 and 46:

Problem Translate the following Whi

- Page 47 and 48:

Problem Translate the following exp

- Page 49 and 50:

Problem Translate the following exp

- Page 51 and 52:

Lecture 10 Translation of High Leve

- Page 53 and 54:

Translation of Procedures Problem H

- Page 55 and 56:

Example Write the MIPS code to comp

- Page 57 and 58:

Program Counter -relative op rs rt

- Page 59 and 60:

Example Opcode always 1 byte Memory

- Page 61 and 62:

Lecture 13 Enhancing Performance at

- Page 63 and 64:

Number Systems Numbers + ve numbers

- Page 65 and 66:

Example: Design a one bit ALU with

- Page 67 and 68:

Lecture 14 - Performance Improvemen

- Page 69 and 70:

Design of Adders c 1 a n , ..., a 1

- Page 71 and 72:

Carry lookahead adder Problem with

- Page 73 and 74:

Another look at CLA xi + yi = Pi xi

- Page 75 and 76:

4-bit CLA Page | 75 generates C3 ge

- Page 77 and 78:

Lecture 15 Performance Improvement

- Page 79 and 80:

Example 981 X 1234 0981 X 1234 mult

- Page 81 and 82:

Example Consider the multiplication

- Page 83 and 84:

2 nd version Reduce cost by reducin

- Page 85 and 86:

4th step 4 bits registers 0010 4 bi

- Page 87 and 88:

0010 ADDER Page | 87 0001 0010 ADDE

- Page 89 and 90:

2's complement of m'cand 1111110101

- Page 91 and 92:

0010 ADDER Page | 91 1111 0001 1 no

- Page 93 and 94:

Lecture 16 - Performance Improvemen

- Page 95 and 96:

Hardware units needed to perform th

- Page 97 and 98:

Step 1 Rem = Rem - Divisor ( this t

- Page 99 and 100: 5th step Rem = Rem - Divisor Now Re

- Page 101 and 102: 2nd step Shift remainder left Rem =

- Page 103 and 104: 3 rd version of Division algorithm

- Page 105 and 106: Step 3 Rem = Rem - Div Rem > 0 Shif

- Page 107 and 108: Normalized Form keeps one digit lef

- Page 109 and 110: Let us consider the addition of two

- Page 111 and 112: Control path Inputs Exponent differ

- Page 113 and 114: Lecture 19 Architectures for Crypto

- Page 115 and 116: 1. Following pseudo code represents

- Page 117 and 118: Find 7 36 mod 11 using right to lef

- Page 119 and 120: Lecture 20 - Performance Chapter -

- Page 121 and 122: total amount of work done in a give

- Page 123 and 124: Question 4 Assuming the CPI for pro

- Page 125 and 126: Question 9 Yet another user has the

- Page 127 and 128: Question 12 Assuming the CPI values

- Page 129 and 130: Use C2 CPI on M1 = 4*0.3+6*0.2+8*0.

- Page 131 and 132: Question 15 We are interested in tw

- Page 133 and 134: Question 18 You are the lead design

- Page 135 and 136: Arithmetic Logic unit Register file

- Page 137 and 138: Lecture 22 - Processor Design - Dat

- Page 139 and 140: Example Design the data path to fet

- Page 141 and 142: Now combine two functional units to

- Page 143 and 144: Lecture 23 Processor Design - Data

- Page 145 and 146: Example : - Design DataPath for SW

- Page 147 and 148: Processor Design - Data path for R&

- Page 149: Example : - Implement R+ I +J Forma

- Page 153 and 154: Draw the logic circuit _ _ _ _ _ _

- Page 155 and 156: Single cycle implementation of the

- Page 157 and 158: from Aluop B from output PC Data Ad

- Page 159 and 160: Lecture 27 High level view of the F

- Page 161 and 162: 0 Page | 161 1 2 3 5 4 0 - MemRead

- Page 163 and 164: FSM Controller for lw/sw 6 states 0

- Page 165 and 166: Lecture 28 R-type instruction conti

- Page 167 and 168: Branch Instruction Fetch Page | 167

- Page 169 and 170: Jump Inst Fetch Page | 169 Inst dec

- Page 171 and 172: Page | 171

- Page 173 and 174: 0 1 Page | 173 2 6 8 9 3 5 7 4 op 0

- Page 175 and 176: NS0 = 1 + 3 + 5 + 7 + 9 NS1 = 2 + 3

- Page 177 and 178: Lecture 30 Microprogramming - FSM c

- Page 179 and 180: - Microinstruction placed in a ROM

- Page 181 and 182: - In multicycle design - assume tha

- Page 183 and 184: Multi-cycle implementation of the M

- Page 185 and 186: 2.5 Draw the functional units neces

- Page 187 and 188: 2.9 The instruction, addi (add imme

- Page 189 and 190: Problems with pipelining Hazards Da

- Page 191 and 192: Ex: Represent the 5 stage pipeline

- Page 193 and 194: Example Represent the 5 stage pipel

- Page 195 and 196: Example: Find the size of each pipe

- Page 197 and 198: Pipelined control path - Single cyc

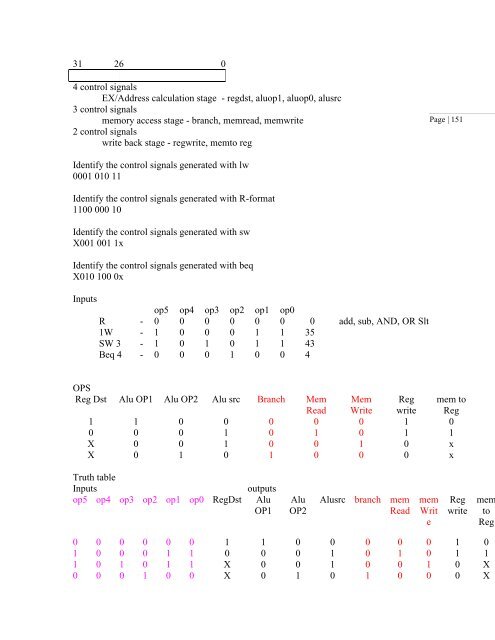

- Page 199 and 200: Control signals with instructions E

- Page 201 and 202:

Ex: Show the control signals genera

- Page 203 and 204:

Ex: Show the control signals genera

- Page 205 and 206:

Lecture 33 Forwarding Unit Design E

- Page 207 and 208:

Example: Illustrate the forwarding

- Page 209 and 210:

Design a Forwarding unit to integra

- Page 211 and 212:

Ex: Forwarding with 2 inst. (1) add

- Page 213 and 214:

Lecture 34 Data hazard and stalls F

- Page 215 and 216:

Tomasulo • Lasting Contributions

- Page 217 and 218:

Tomasulo Organization Page | 217

- Page 219 and 220:

4. Show the pipeline execution of f

- Page 221 and 222:

7. Illustrate the pipelined data pa

- Page 223 and 224:

11. Reorder the following instructi

- Page 225 and 226:

15. Design the forwarding unit for

- Page 227 and 228:

Temporal locality Low Data Accessin

- Page 229 and 230:

Associative mapping More flexible m

- Page 231 and 232:

Problems 1. Here is a series of add

- Page 233 and 234:

6. What are the miss rate of the fo

- Page 235 and 236:

Installation and Usage of Maxplus I

- Page 237 and 238:

intend to read registers this instr

- Page 239 and 240:

Tomasulo hardware algorithm From Wi

- Page 241:

When all operands are available o I