Intel 80310 I/O Processor Chipset AAU Coding Techniques

Intel 80310 I/O Processor Chipset AAU Coding Techniques

Intel 80310 I/O Processor Chipset AAU Coding Techniques

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

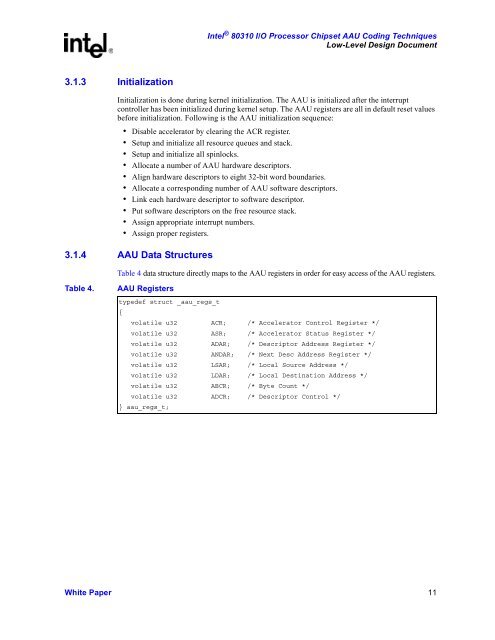

<strong>Intel</strong> ® <strong>80310</strong> I/O <strong>Processor</strong> <strong>Chipset</strong> <strong>AAU</strong> <strong>Coding</strong> <strong>Techniques</strong>Low-Level Design Document3.1.3 InitializationInitialization is done during kernel initialization. The <strong>AAU</strong> is initialized after the interruptcontroller has been initialized during kernel setup. The <strong>AAU</strong> registers are all in default reset valuesbefore initialization. Following is the <strong>AAU</strong> initialization sequence:• Disable accelerator by clearing the ACR register.• Setup and initialize all resource queues and stack.• Setup and initialize all spinlocks.• Allocate a number of <strong>AAU</strong> hardware descriptors.• Align hardware descriptors to eight 32-bit word boundaries.• Allocate a corresponding number of <strong>AAU</strong> software descriptors.• Link each hardware descriptor to software descriptor.• Put software descriptors on the free resource stack.• Assign appropriate interrupt numbers.• Assign proper registers.3.1.4 <strong>AAU</strong> Data StructuresTable 4 data structure directly maps to the <strong>AAU</strong> registers in order for easy access of the <strong>AAU</strong> registers.Table 4.<strong>AAU</strong> Registerstypedef struct _aau_regs_t{volatile u32 ACR; /* Accelerator Control Register */volatile u32 ASR; /* Accelerator Status Register */volatile u32 ADAR; /* Descriptor Address Register */volatile u32 ANDAR; /* Next Desc Address Register */volatile u32 LSAR; /* Local Source Address */volatile u32 LDAR; /* Local Destination Address */volatile u32 ABCR; /* Byte Count */volatile u32 ADCR; /* Descriptor Control */} aau_regs_t;White Paper 11