Intel 80310 I/O Processor Chipset AAU Coding Techniques

Intel 80310 I/O Processor Chipset AAU Coding Techniques

Intel 80310 I/O Processor Chipset AAU Coding Techniques

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

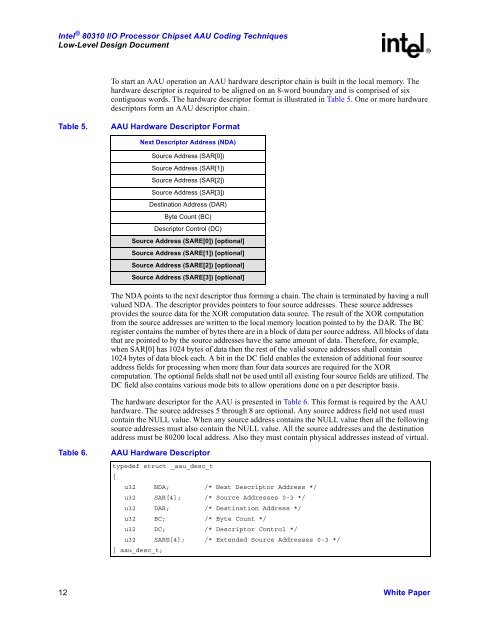

<strong>Intel</strong> ® <strong>80310</strong> I/O <strong>Processor</strong> <strong>Chipset</strong> <strong>AAU</strong> <strong>Coding</strong> <strong>Techniques</strong>Low-Level Design DocumentTo start an <strong>AAU</strong> operation an <strong>AAU</strong> hardware descriptor chain is built in the local memory. Thehardware descriptor is required to be aligned on an 8-word boundary and is comprised of sixcontiguous words. The hardware descriptor format is illustrated in Table 5. One or more hardwaredescriptors form an <strong>AAU</strong> descriptor chain.Table 5.<strong>AAU</strong> Hardware Descriptor FormatNext Descriptor Address (NDA)Source Address (SAR[0])Source Address (SAR[1])Source Address (SAR[2])Source Address (SAR[3])Destination Address (DAR)Byte Count (BC)Descriptor Control (DC)Source Address (SARE[0]) [optional]Source Address (SARE[1]) [optional]Source Address (SARE[2]) [optional]Source Address (SARE[3]) [optional]The NDA points to the next descriptor thus forming a chain. The chain is terminated by having a nullvalued NDA. The descriptor provides pointers to four source addresses. These source addressesprovides the source data for the XOR computation data source. The result of the XOR computationfrom the source addresses are written to the local memory location pointed to by the DAR. The BCregister contains the number of bytes there are in a block of data per source address. All blocks of datathat are pointed to by the source addresses have the same amount of data. Therefore, for example,when SAR[0] has 1024 bytes of data then the rest of the valid source addresses shall contain1024 bytes of data block each. A bit in the DC field enables the extension of additional four sourceaddress fields for processing when more than four data sources are required for the XORcomputation. The optional fields shall not be used until all existing four source fields are utilized. TheDC field also contains various mode bits to allow operations done on a per descriptor basis.The hardware descriptor for the <strong>AAU</strong> is presented in Table 6. This format is required by the <strong>AAU</strong>hardware. The source addresses 5 through 8 are optional. Any source address field not used mustcontain the NULL value. When any source address contains the NULL value then all the followingsource addresses must also contain the NULL value. All the source addresses and the destinationaddress must be 80200 local address. Also they must contain physical addresses instead of virtual.Table 6.<strong>AAU</strong> Hardware Descriptortypedef struct _aau_desc_t{u32 NDA; /* Next Descriptor Address */u32 SAR[4]; /* Source Addresses 0-3 */u32 DAR; /* Destination Address */u32 BC; /* Byte Count */u32 DC; /* Descriptor Control */u32 SARE[4]; /* Extended Source Addresses 0-3 */} aau_desc_t;12 White Paper