Single-Chip Low Power RF Transceiver for Narrowband Systems ...

Single-Chip Low Power RF Transceiver for Narrowband Systems ...

Single-Chip Low Power RF Transceiver for Narrowband Systems ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

CC1021<br />

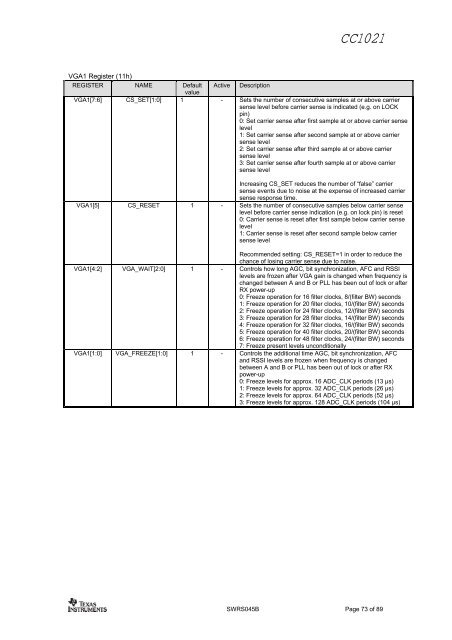

VGA1 Register (11h)<br />

REGISTER NAME Default<br />

value<br />

Active Description<br />

VGA1[7:6] CS_SET[1:0] 1 - Sets the number of consecutive samples at or above<br />

carrier<br />

sense level be<strong>for</strong>e carrier sense is indicated (e.g. on LOCK<br />

pin)<br />

0: Set carrier sense after first sample at or above carrier sense<br />

level<br />

1: Set carrier sense after second sample at or above carrier<br />

sense level<br />

2: Set carrier sense after third sample at or above carrier<br />

sense level<br />

3: Set carrier sense after fourth sample<br />

at or above carrier<br />

sense<br />

level<br />

VGA1[5] CS_RESET 1 -<br />

Increasing CS_SET reduces the number of “false” carrier<br />

sense events due to noise at the expense of increased<br />

carrier<br />

sense<br />

response time.<br />

Sets the number of consecutive samples<br />

below carrier sense<br />

level be<strong>for</strong>e carrier sense indication<br />

(e.g. on lock pin) is reset<br />

0: Carr ier sense is reset after first sample below carrier sense<br />

level<br />

1: Carrier sense is reset after second sample below<br />

carrier<br />

sense<br />

level<br />

VGA1[4:2] VGA_WAIT[2:0] 1 -<br />

Recom mended setting: CS_RESET=1 in order to reduce the<br />

chance of losing carrier sense due to noise.<br />

Controls how long AGC, bit synchronization, AFC<br />

and RSSI<br />

levels are frozen after VGA gain is changed when frequency is<br />

changed between A and B or PLL has been out of lock or after<br />

RX power-up<br />

0: Freeze operation <strong>for</strong> 16 filter clocks, 8/(filter BW) seconds<br />

1: Freeze operation <strong>for</strong> 20 filter clocks, 10/(filter BW) seconds<br />

2: Freeze operation <strong>for</strong> 24 filter clocks, 12/(filter BW) seconds<br />

3: Freeze operation <strong>for</strong> 28 filter clocks, 14/(filter BW) seconds<br />

4: Freeze operation <strong>for</strong> 32 filter clocks, 16/(filter BW) seconds<br />

5: Freeze operation <strong>for</strong> 40 filter clocks, 20/(filter BW) seconds<br />

6: Freeze operation <strong>for</strong> 48 filter clocks, 24/(filter BW) seconds<br />

7: Freeze present levels unconditionally<br />

VGA1[1:0] VGA_FREEZE[1:0] 1 - Controls the additional time AGC, bit synchronization, AFC<br />

and RSSI levels are frozen when frequency is changed<br />

between A and B or PLL has been out of lock or after RX<br />

power-up<br />

0: Freeze levels <strong>for</strong> approx. 16 ADC_CLK periods (13 µs)<br />

1: Freeze levels <strong>for</strong> approx. 32 ADC_CLK periods (26 µs)<br />

2: Freeze levels <strong>for</strong> approx. 64 ADC_CLK periods (52 µs)<br />

3: Freeze levels <strong>for</strong> approx. 128 ADC_CLK periods (104 µs)<br />

SWRS045B Page 73 of 89