Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Chapter 6 – Introduction (5/2/04) Page 6.0-1<br />

CHAPTER 6 – CMOS OPERATIONAL AMPLIFIERS<br />

Chapter Outline<br />

6.1 <strong>Design</strong> of CMOS Op Amps<br />

6.2 Compensation of Op Amps<br />

6.3 Two-Stage Operational Amplifier <strong>Design</strong><br />

6.4 Power Supply Rejection Ratio of the Two-Stage Op Amp<br />

6.5 Cascode Op Amps<br />

6.6 Simulation and Measurement of Op Amps<br />

6.7 Macromodels for Op Amps<br />

6.8 Summary<br />

Goal<br />

Understand the analysis, design, and measurement of simple CMOS op amps<br />

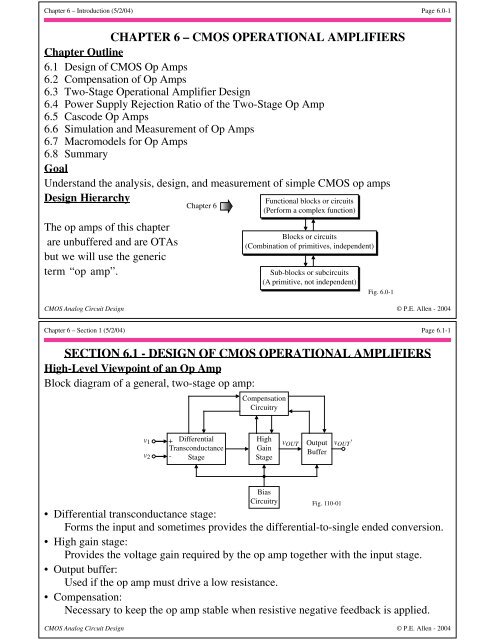

<strong>Design</strong> Hierarchy<br />

The op amps of this <strong>chapter</strong><br />

are unbuffered and are OTAs<br />

but we will use the generic<br />

term “op amp”.<br />

Chapter 6<br />

Functional blocks or circuits<br />

(Perform a complex function)<br />

Blocks or circuits<br />

(Combination of primitives, independent)<br />

Sub-blocks or subcircuits<br />

(A primitive, not independent)<br />

Fig. 6.0-1<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-1<br />

SECTION 6.1 - DESIGN OF CMOS OPERATIONAL AMPLIFIERS<br />

High-Level Viewpoint of an Op Amp<br />

Block diagram of a general, two-stage op amp:<br />

Compensation<br />

Circuitry<br />

v 1<br />

v 2<br />

+ Differential<br />

Transconductance<br />

- Stage<br />

High<br />

Gain<br />

Stage<br />

v OUT<br />

Output<br />

Buffer<br />

v OUT '<br />

Bias<br />

Circuitry<br />

Fig. 110-01<br />

• Differential transconductance stage:<br />

Forms the input and sometimes provides the differential-to-single ended conversion.<br />

• High gain stage:<br />

Provides the voltage gain required by the op amp together with the input stage.<br />

• Output buffer:<br />

Used if the op amp must drive a low resistance.<br />

• Compensation:<br />

Necessary to keep the op amp stable when resistive negative feedback is applied.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-2<br />

Ideal Op Amp<br />

Symbol:<br />

i 1<br />

V DD<br />

+<br />

+ +<br />

i 2<br />

v -<br />

v i<br />

1 -<br />

+<br />

+<br />

v OUT = A v (v 1 -v 2 )<br />

v 2<br />

-<br />

-<br />

V SS<br />

-<br />

Fig. 110-02<br />

Null port:<br />

If the differential gain of the op amp is large enough then input terminal pair becomes a<br />

null port.<br />

A null port is a pair of terminals where the voltage is zero and the current is zero.<br />

I.e.,<br />

v 1 - v 2 = v i = 0<br />

and<br />

i 1 = 0 and i 2 = 0<br />

Therefore, ideal op amps can be analyzed by assuming the differential input voltage is<br />

zero and that no current flows into or out of the differential inputs.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-3<br />

General Configuration of the Op Amp as a Voltage Amplifier<br />

R 1<br />

- R2<br />

+ +<br />

v<br />

+<br />

inn<br />

v inp<br />

v 2<br />

v 1<br />

- -<br />

Noniverting voltage amplifier:<br />

⎛R ⎜ 1 +R 2<br />

⎞<br />

⎟<br />

v inn = 0 ⇒ v out = ⎜ ⎟<br />

⎝<br />

R 1<br />

v<br />

⎠ inp<br />

Inverting voltage amplifier:<br />

v inp = 0 ⇒ v out = - R ⎜⎛ 2<br />

⎜ ⎝<br />

R 1 ⎠ ⎟⎟⎞ v inn<br />

+<br />

vout<br />

-<br />

Fig. 110-03<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-4<br />

Example 6.1-1 - Simplified Analysis of an Op Amp Circuit<br />

The circuit shown below is an inverting voltage amplifier using an op amp. Find the<br />

voltage transfer function, v out /v in .<br />

R 1<br />

i 1 i 2<br />

R 2<br />

i i<br />

- + +<br />

+<br />

v in + v i v out<br />

- -<br />

-<br />

Virtual Ground Fig. 110-04<br />

Solution<br />

If A v → ∞, then v i → 0 because of the negative feedback path through R 2 .<br />

(The op amp with –fb. makes its input terminal voltages equal.)<br />

v i = 0 and i i = 0<br />

Note that the null port becomes the familiar virtual ground if one of the op amp input<br />

terminals is on ground. If this is the case, then we can write that<br />

i 1 = v in<br />

R 1<br />

and i 2 = v out<br />

R 2<br />

v out<br />

Since, i i = 0, then i 1 + i 2 = 0 giving the desired result as v in<br />

= - R 2<br />

R 1<br />

.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-5<br />

Linear and Static Characterization of the Op Amp<br />

A model for a nonideal op amp that includes some of the linear, static nonidealities:<br />

v 1<br />

CMRR<br />

v 2<br />

v 1<br />

-<br />

+<br />

R icm I B2<br />

e n 2<br />

V OS<br />

*<br />

i n 2 C id R id<br />

R out vout<br />

R icm I B1<br />

Ideal Op Amp<br />

where<br />

R id = differential input resistance<br />

C id = differential input capacitance<br />

R icm = common mode input resistance<br />

V OS = input-offset voltage<br />

I B1 and I B2 = differential input-bias currents<br />

I OS = input-offset current (I OS = I B1 -I B2 )<br />

CMRR = common-mode rejection ratio<br />

e 2 n = voltage-noise spectral density (mean-square volts/Hertz)<br />

i 2 n = current-noise spectral density (mean-square amps/Hertz)<br />

Fig. 110-05<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-6<br />

Linear and Dynamic Characteristics of the Op Amp<br />

Differential and common-mode frequency response:<br />

⎛V ⎜ 1 (s)+V 2 (s)⎞<br />

⎟<br />

V out (s) = A v (s)[V 1 (s) - V 2 (s)] ± A c (s) ⎜<br />

⎟<br />

⎝ 2 ⎠<br />

Differential-frequency response:<br />

A v0<br />

A v0 p 1 p 2 p 3···<br />

A v (s) =<br />

⎛ s ⎞⎛<br />

s ⎞⎛<br />

s ⎞<br />

= (s -p<br />

⎜ ⎟⎜<br />

⎟⎜<br />

⎟ 1 )(s -p 2 )(s -p 3 )···<br />

⎜ ⎟<br />

⎝p 1<br />

- 1 ⎜ ⎟<br />

⎠⎝p 2<br />

- 1 ⎜ ⎟<br />

⎠⎝p 3<br />

- 1 ···<br />

⎠<br />

where p 1 , p 2 , p 3 ,··· are the poles of the differential-frequency response (ignoring zeros).<br />

20log10(A v0 )<br />

|A v (jω)| dB<br />

Asymptotic<br />

Magnitude<br />

Actual<br />

Magnitude<br />

-6dB/oct.<br />

GB<br />

0dB<br />

Fig. 110-06<br />

ω 1<br />

ω 2 ω 3<br />

ω<br />

-12dB/oct.<br />

-18dB/oct.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-7<br />

Other Characteristics of the Op Amp<br />

Power supply rejection ratio (PSRR):<br />

PSRR ∆V DD<br />

= ∆V OUT<br />

A v (s) V o/V in (V dd = 0)<br />

= V o /V dd (V in = 0)<br />

Input common mode range (<strong>IC</strong>MR):<br />

<strong>IC</strong>MR = the voltage range over which the input common-mode signal can vary<br />

without influence the differential performance<br />

Slew rate (SR):<br />

SR = output voltage rate limit of the op amp<br />

Settling time (T s ):<br />

-<br />

+<br />

v OUT<br />

Final Value + ε<br />

Final Value<br />

Final Value - ε<br />

v OUT (t)<br />

ε<br />

ε<br />

Upper Tolerance<br />

Lower Tolerance<br />

Settling Time<br />

0<br />

0<br />

v IN<br />

Fig. 110-07<br />

T s<br />

t<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-8<br />

Classification of CMOS Op Amps<br />

Categorization of op amps:<br />

Conversion<br />

Hierarchy<br />

Voltage<br />

to Current<br />

Current<br />

to Voltage<br />

Classic Differential<br />

Amplifier<br />

Differential-to-single ended<br />

Load (Current Mirror)<br />

Modified Differential<br />

Amplifier<br />

Source/Sink<br />

Current Loads<br />

MOS Diode<br />

Load<br />

First<br />

Voltage<br />

Stage<br />

Voltage<br />

to Current<br />

Current<br />

to Voltage<br />

Transconductance<br />

Grounded Gate<br />

Class A (Source<br />

or Sink Load)<br />

Transconductance<br />

Grounded Source<br />

Class B<br />

(Push-Pull)<br />

Current<br />

Stage<br />

Second<br />

Voltage<br />

Stage<br />

Table 110-01<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-9<br />

Two-Stage CMOS Op Amp<br />

Classical two-stage CMOS op amp broken into voltage-to-current and current-to-voltage<br />

stages:<br />

V DD<br />

M3<br />

M4<br />

M6<br />

-<br />

v in<br />

+<br />

M1 M2<br />

v out<br />

v in<br />

-<br />

+<br />

v out<br />

VBias<br />

M5<br />

M7<br />

V→I I→V V→I I→V<br />

V SS<br />

Fig. 6.1-8<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-10<br />

Folded Cascode CMOS Op Amp<br />

Folded cascode CMOS op amp broken into stages.<br />

V DD<br />

V Bias<br />

M3<br />

M10<br />

M11<br />

+ M1 M2<br />

v -<br />

in M8 M9<br />

v out<br />

-<br />

+<br />

M6 M7<br />

V Bias<br />

v out<br />

v in<br />

Fig. 6.1-9<br />

V Bias<br />

M4 M5<br />

V→I I→I I→V<br />

V SS<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-11<br />

<strong>Design</strong> of CMOS Op Amps<br />

Steps:<br />

1.) Choosing or creating the basic structure of the op amp.<br />

This step is results in a schematic showing the transistors and their interconnections.<br />

This diagram does not change throughout the remainder of the design unless the<br />

specifications cannot be met, then a new or modified structure must be developed.<br />

2.) Selection of the dc currents and transistor sizes.<br />

Most of the effort of design is in this category.<br />

Simulators are used to aid the designer in this phase. The general performance of the<br />

circuit should be known a priori.<br />

3.) Physical implementation of the design.<br />

Layout of the transistors<br />

Floorplanning the connections, pin-outs, power supply buses and grounds<br />

Extraction of the physical parasitics and resimulation<br />

Verification that the layout is a physical representation of the circuit.<br />

4.) Fabrication<br />

5.) Measurement<br />

Verification of the specifications<br />

Modification of the design as necessary<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-12<br />

Boundary Conditions and Requirements for CMOS Op Amps<br />

Boundary conditions:<br />

1. Process specification (V T , K', C ox , etc.)<br />

2. Supply voltage and range<br />

3. Supply current and range<br />

4. Operating temperature and range<br />

Requirements:<br />

1. Gain<br />

2. Gain bandwidth<br />

3. Settling time<br />

4. Slew rate<br />

5. Common-mode input range, <strong>IC</strong>MR<br />

6. Common-mode rejection ratio, CMRR<br />

7. Power-supply rejection ratio, PSRR<br />

8. Output-voltage swing<br />

9. Output resistance<br />

10. Offset<br />

11. Noise<br />

12. Layout area<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 1 (5/2/04) Page 6.1-13<br />

Specifications for a Typical Unbuffered CMOS Op Amp<br />

Boundary Conditions Requirement<br />

Process Specification See Tables 3.1-1 and 3.1-2<br />

Supply Voltage ±2.5 V ±10%<br />

Supply Current 100 µA<br />

Temperature Range 0 to 70°C<br />

Specifications<br />

Value<br />

Gain<br />

≥ 70 dB<br />

Gainbandwidth ≥ 5 MHz<br />

Settling Time<br />

≤ 1 µsec<br />

Slew Rate<br />

≥ 5 V/µsec<br />

Input CMR<br />

≥ ±1.5 V<br />

CMRR<br />

≥ 60 dB<br />

PSRR<br />

≥ 60 dB<br />

Output Swing<br />

≥ ±1.5 V<br />

Output Resistance N/A, capacitive load only<br />

Offset<br />

≤ ±10 mV<br />

Noise<br />

≤ 100nV/ Hz at 1KHz<br />

Layout Area ≤ 10,000 min. channel length 2<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 1 (5/2/04) Page 6.1-14<br />

Some Practical Thoughts on Op Amp <strong>Design</strong><br />

1.) Decide upon a suitable topology.<br />

• Experience is a great help<br />

• The topology should be the one capable of meeting most of the specifications<br />

• Try to avoid “inventing” a new topology but start with an existing topology<br />

2.) Determine the type of compensation needed to meet the specifications.<br />

• Consider the load and stability requirements<br />

• Use some form of Miller compensation or a self-compensated approach (shown<br />

later)<br />

3.) <strong>Design</strong> dc currents and device sizes for proper dc, ac, and transient performance.<br />

• This begins with hand calculations based upon approximate design equations.<br />

• Compensation components are also sized in this step of the procedure.<br />

• After each device is sized by hand, a circuit simulator is used to fine tune the design<br />

Two basic steps of design:<br />

1.) “First-cut” - this step is to use hand calculations to propose a design that has<br />

potential of satisfying the specifications. <strong>Design</strong> robustness is developed in this step.<br />

2.) Optimization - this step uses the computer to refine and optimize the design.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-1<br />

SECTION 6.2 - COMPENSATION OF OP AMPS<br />

Compensation<br />

Objective<br />

Objective of compensation is to achieve stable operation when negative feedback is<br />

applied around the op amp.<br />

Types of Compensation<br />

1. Miller - Use of a capacitor feeding back around a high-gain, inverting<br />

stage.<br />

• Miller capacitor only<br />

• Miller capacitor with an unity-gain buffer to block the forward path through the<br />

compensation capacitor. Can eliminate the RHP zero.<br />

• Miller with a nulling resistor. Similar to Miller but with an added series resistance<br />

to gain control over the RHP zero.<br />

2. Self compensating - Load capacitor compensates the op amp (later).<br />

3. Feedforward - Bypassing a positive gain amplifier resulting in phase lead. Gain can be<br />

less than unity.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-2<br />

Single-Loop, Negative Feedback Systems<br />

Block diagram:<br />

A(s) = differential-mode voltage gain of the<br />

op amp<br />

F(s) = feedback transfer function from the<br />

output of op amp back to the input.<br />

Definitions:<br />

• Open-loop gain = L(s) = -A(s)F(s)<br />

• Closed-loop gain = V out(s)<br />

V in (s) = A(s)<br />

1+A(s)F(s)<br />

V in (s)<br />

Stability Requirements:<br />

The requirements for stability for a single-loop, negative feedback system is,<br />

|A(jω 0° )F(jω 0° )| = |L(jω 0° )| < 1<br />

where ω 0° is defined as<br />

Arg[−A(jω 0° )F(jω 0° )] = Arg[L(jω 0° )] = 0°<br />

Another convenient way to express this requirement is<br />

Arg[−A(jω 0dB )F(jω 0dB )] = Arg[L(jω 0dB )] > 0°<br />

where ω 0dB is defined as<br />

|A(jω 0dB )F(jω 0dB )| = |L(jω 0dB )| = 1<br />

+<br />

-<br />

Σ<br />

F(s)<br />

A(s)<br />

V out (s)<br />

Fig. 120-01<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-3<br />

Illustration of the Stability Requirement using Bode Plots<br />

|A(jω)F(jω)|<br />

Arg[-A(jω)F(jω)]<br />

0dB<br />

180°<br />

135°<br />

90°<br />

45°<br />

0°<br />

-20dB/decade<br />

ω 0dB<br />

ω<br />

-40dB/decade<br />

Frequency (rads/sec.)<br />

A measure of stability is given by the phase when |A(jω)F(jω)| = 1. This phase is called<br />

phase margin.<br />

Phase margin = Φ M = Arg[-A(jω 0dB )F(jω 0dB )] = Arg[L(jω 0dB )]<br />

Φ M<br />

ω<br />

Fig. Fig. 120-02<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-4<br />

Why Do We Want Good Stability?<br />

Consider the step response of second-order system which closely models the closed-loop<br />

gain of the op amp.<br />

v out (t)<br />

A v0<br />

1.4<br />

1.2<br />

1.0<br />

0.8<br />

0.6<br />

0.4<br />

45°<br />

50°<br />

55°<br />

60°<br />

65°<br />

70°<br />

-<br />

+<br />

0.2<br />

0<br />

0 5 10 15 Fig. 120-03<br />

ω o t = ω n t (sec.)<br />

A “good” step response is one that quickly reaches its final value.<br />

Therefore, we see that phase margin should be at least 45° and preferably 60° or larger.<br />

(A rule of thumb for satisfactory stability is that there should be less than three rings.)<br />

Note that good stability is not necessarily the quickest risetime.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-5<br />

Uncompensated Frequency Response of Two-Stage Op Amps<br />

Two-Stage Op Amps:<br />

V DD<br />

V CC<br />

M3<br />

M4<br />

M6<br />

Q3<br />

Q4<br />

Q6<br />

-<br />

v in<br />

+<br />

M1 M2<br />

v out<br />

-<br />

v in<br />

Q1 Q2<br />

+<br />

v out<br />

+<br />

VBias<br />

-<br />

Small-Signal Model:<br />

M5<br />

V SS<br />

M7<br />

+<br />

VBias<br />

-<br />

Q5<br />

V EE<br />

Q7<br />

Fig. 120-04<br />

g m1 v in<br />

2<br />

D1, D3 (C1, C3) D2, D4 (C2, C4) D6, D7 (C6, C7)<br />

+<br />

R 1 C 1 v1 g +<br />

+<br />

m2v in<br />

v out<br />

2<br />

-<br />

g m4 v 1<br />

R 2 C<br />

v2 R 3 C 3 2 - gm6 v 2<br />

-<br />

Fig. 120-05<br />

Note that this model neglects the base-collector and gate-drain capacitances for purposes<br />

of simplification.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-6<br />

Uncompensated Frequency Response of Two-Stage Op Amps - Continued<br />

For the MOS two-stage op amp:<br />

1<br />

1<br />

R 1 ≈ g ||r m3 ds3 ||r ds1 ≈ g R m3 2 = r ds2 || r ds4 and R 3 = r ds6 || r ds7<br />

C 1 = C gs3 +C gs4 +C bd1 +C bd3 C 2 = C gs6 +C bd2 +C bd4 and C 3 = C L +C bd6 +C bd7<br />

For the BJT two-stage op amp:<br />

1<br />

R 1 = g m3<br />

||r π3 ||r π4 ||r o1 ||r o3 ≈ 1<br />

g m3<br />

R 2 = r π6 || r o2 || r o4 ≈ r π6 and R 3 = r o6 || r o7<br />

C 1 = C π3 +C π4 +C cs1 +C cs3 C 2 = C π6 +C cs2 +C cs4 and C 3 = C L +C cs6 +C cs7<br />

Assuming the pole due to C 1 is much greater than the poles due to C 2 and C 3 gives,<br />

+<br />

+<br />

g m1 v in v out<br />

R 2 C<br />

v2 R 3 C 3 2 - gm6 v 2<br />

-<br />

+<br />

+<br />

g m1 V in V V out<br />

R I C I R II C II I - gmII V I<br />

-<br />

Fig. 120-06<br />

The locations for the two poles are given by the following equations<br />

p’ 1 = −1<br />

−1<br />

R I C I<br />

and p’ 2 = R II C II<br />

where R I (R II ) is the resistance to ground seen from the output of the first (second) stage<br />

and C I (C II ) is the capacitance to ground seen from the output of the first (second) stage.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-7<br />

Uncompensated Frequency Response of an Op Amp<br />

A vd (0) dB<br />

-20dB/decade<br />

|A(jω)|<br />

Arg[-A(jω)]<br />

0dB<br />

Phase Shift<br />

180°<br />

135°<br />

90°<br />

45°<br />

0°<br />

-45°/decade<br />

|p 1 '|<br />

log 10 (ω)<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

GB<br />

-45°/decade<br />

-40dB/decade<br />

log 10 (ω)<br />

|p 2 '| ω 0dB Fig. 120-07<br />

If we assume that F(s) = 1 (this is the worst case for stability considerations), then the<br />

above plot is the same as the loop gain.<br />

Note that the phase margin is much less than 45°.<br />

Therefore, the op amp must be compensated before using it in a closed-loop<br />

configuration.

Chapter 6 – Section 2 (5/2/04) Page 6.2-8<br />

Miller Compensation of the Two-Stage Op Amp<br />

V DD<br />

V CC<br />

M3<br />

M1<br />

-<br />

M2<br />

v in<br />

+<br />

+<br />

VBias<br />

-<br />

C M<br />

M5<br />

M4<br />

V SS<br />

Q3 Q4<br />

M6<br />

C M<br />

Q6<br />

C c v out<br />

C c v out<br />

-<br />

Q1 Q2<br />

C<br />

v I<br />

C II in C<br />

+<br />

I<br />

C II<br />

M7<br />

+<br />

VBias<br />

-<br />

The various capacitors are:<br />

C c = accomplishes the Miller compensation<br />

C M = capacitance associated with the first-stage mirror (mirror pole)<br />

C I = output capacitance to ground of the first-stage<br />

C II = output capacitance to ground of the second-stage<br />

Q5<br />

V EE<br />

Q7<br />

Fig. 120-08<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-9<br />

Compensated Two-Stage, Small-Signal Frequency Response Model Simplified<br />

Use the CMOS op amp to illustrate:<br />

1.) Assume that g m3 >> g ds3 + g ds1<br />

2.) Assume that g m3<br />

C M<br />

>> GB<br />

Therefore,<br />

v 1 v2<br />

C c<br />

+<br />

-g m1 v in<br />

2 1 g m2 v in<br />

C M g m3 2 g m4 v 1<br />

C 1 rds2 ||r ds4<br />

g m6 v 2 r ds6 ||r ds7 C L<br />

v out<br />

-<br />

r ds1 ||r ds3<br />

g m1 v in rds2 ||r ds4<br />

g m6 v 2 rds6 ||r ds7<br />

C II<br />

+<br />

v in<br />

-<br />

CI<br />

C c<br />

v 2<br />

+<br />

v out<br />

-<br />

Fig. 120-09<br />

Same circuit holds for the BJT op amp with different component relationships.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-10<br />

General Two-Stage Frequency Response Analysis<br />

+<br />

V in<br />

-<br />

g mI V in<br />

C I RI gmII V 2<br />

R II C II<br />

where<br />

g mI = g m1 = gm2, R I = r ds2 ||r ds4 , C I = C 1<br />

and<br />

g mII = g m6 , R II = r ds6 ||r ds7 , C II = C 2 = C L<br />

Nodal Equations:<br />

-g mI V in = [G I + s(C I + C c )]V 2 - [sC c ]V out and 0 = [g mII - sC c ]V 2 + [G II + sC II + sC c ]V out<br />

Solving using Cramer’s rule gives,<br />

V out (s)<br />

V in (s) = g mI (g mII - sC c )<br />

G I G II +s [G II (C I +C II )+G I (C II +C c )+g mII C c ]+s 2 [C I C II +C c C I +C c C II ]<br />

A o [1 - s (C c /g mII )]<br />

= 1+s [R I (C I +C II )+R II (C 2 +C c )+g mII R 1 R II C c ]+s 2 [R I R II (C I C II +C c C I +C c C II )]<br />

where, A o = g mI g mII R I R II<br />

⎛ ⎞<br />

⎜ ⎟<br />

In general, D(s) = ⎜1- s p ⎟ ⎜ ⎜ ⎛<br />

1 ⎝ ⎠ ⎟ ⎟<br />

1- s ⎞ ⎛ 1 ⎞<br />

⎜ ⎟<br />

p = 1-s ⎜ ⎟<br />

2 p + 1<br />

1 p + s2<br />

2 p 1 p → D(s) ≈ 1- s<br />

2<br />

p + s2<br />

1 p 1 p , if |p 2 |>>|p 1 |<br />

2<br />

∴ p 1 =<br />

V 2<br />

C c<br />

+<br />

⎝<br />

⎠<br />

⎝<br />

V out<br />

-<br />

Fig.120-10<br />

-1<br />

-1<br />

R I (C I +C II )+R II (C II +C c )+g mII R 1 R II C c<br />

≈ g mII R 1 R II C c<br />

, z = g mII<br />

C c<br />

⎠<br />

p 2 = -[R I(C I +C II )+R II (C II +C c )+g mII R 1 R II C c ] -g mII C c<br />

R I R II (C I C II +C c C I +C c C II ) ≈ C I C II +C c C I +C c C II<br />

≈ -g mII<br />

C II<br />

, C II > C c > C I<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-11<br />

Summary of Results for Miller Compensation of the Two-Stage Op Amp<br />

There are three roots of importance:<br />

1.) Right-half plane zero:<br />

z 1 = g mII<br />

C c<br />

= g m6<br />

C c<br />

This root is very undesirable- it boosts the magnitude while decreasing the phase.<br />

2.) Dominant left-half plane pole (the Miller pole):<br />

-1<br />

p 1 ≈ g mII R I R II C c<br />

= -(g ds2+g ds4 )(g ds6 +g ds7 )<br />

g m6 C c<br />

This root accomplishes the desired compensation.<br />

3.) Left-half plane output pole:<br />

p 2 ≈ -g mII<br />

C II<br />

≈ -g m6<br />

C L<br />

This pole must be ≥ unity-gainbandwidth or the phase margin will not be satisfied.<br />

Root locus plot of the Miller compensation:<br />

Closed-loop poles, C c ≠0<br />

Open-loop poles<br />

C c =0<br />

jω<br />

σ<br />

p 2 p 2 ' p 1 ' p 1<br />

z 1 Fig. 120-11<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-12<br />

Compensated Open-Loop Frequency Response of the Two-Stage Op Amp<br />

|A(jω)F(jω)|<br />

A vd (0) dB<br />

Compensated<br />

Uncompensated<br />

-20dB/decade<br />

Arg[-A(jω)F(jω)|<br />

Note that the unity-gainbandwidth, GB, is<br />

GB<br />

0dB<br />

log 10 (ω)<br />

Phase Shift<br />

Uncompensated<br />

-40dB/decade<br />

180°<br />

135°<br />

-45°/decade<br />

90°<br />

-45°/decade<br />

Compensated<br />

45°<br />

Phase<br />

No phase margin<br />

Margin<br />

0°<br />

log 10 (ω)<br />

|p 1 | |p 1 '| |p 2 '| |p 2 |<br />

Fig. 120-12<br />

1<br />

GB = A vd (0)·|p 1 | = (g mI g mII R I R II ) g mII R I R II C = g mI<br />

c C = g m1<br />

c C = g m2<br />

c C c<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-13<br />

Conceptually, where do these roots come from?<br />

1.) The Miller pole:<br />

V DD<br />

|p 1 | ≈<br />

1<br />

R I (g m6 R II C c )<br />

R I<br />

C c<br />

R II<br />

v out<br />

M6<br />

v I<br />

≈g m6 R II C c<br />

Fig. 120-13<br />

2.) The left-half plane output pole:<br />

V DD<br />

|p 2 | ≈ g m6<br />

C II<br />

C c<br />

R II<br />

v out<br />

M6<br />

C II<br />

1<br />

GB·C<br />

≈ 0 c<br />

V DD<br />

R II<br />

v out<br />

M6<br />

C II<br />

3.) Right-half plane zero (One source of zeros is from<br />

multiple paths from the input to output):<br />

g<br />

-g<br />

v out = ⎜ ⎜⎛ m6 R II (1/sC c ) R -R ⎜⎛ m6<br />

II⎝ ⎜<br />

⎝<br />

R<br />

⎠ ⎟⎟⎞<br />

II + 1/sC c<br />

v’ + ⎜ ⎜⎛ II<br />

sC<br />

⎠ ⎟⎟⎞ c<br />

- 1<br />

⎝<br />

R<br />

⎠ ⎟⎟⎞<br />

II + 1/sC c<br />

v’’ = R II + 1/sC c<br />

v<br />

where v = v’ = v’’.<br />

v''<br />

v'<br />

C c<br />

Fig. 120-14<br />

V DD<br />

R II<br />

v out<br />

M6<br />

Fig. 120-15<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-14<br />

Influence of the Mirror Pole<br />

Up to this point, we have neglected the influence of the pole, p 3 , associated with the<br />

current mirror of the input stage. A small-signal model for the input stage that includes<br />

C 3 is shown below:<br />

gm1V in<br />

2<br />

rds1<br />

rds3<br />

i 3<br />

gm2V in<br />

1<br />

i<br />

gm3 C 3 2 3 rds2 rds4<br />

Fig. 120-16<br />

The transfer function from the input to the output voltage of the first stage, V o1 (s), can be<br />

written as<br />

V o1 (s)<br />

V in (s) =<br />

-g m1<br />

2(g ds2 +g ds4 ) ⎢ ⎢ ⎡ g m3 +g ds1 +g ds3<br />

⎣ ⎦ ⎥ ⎥ ⎤ -g m1<br />

g m3 + g ds1 +g ds3 +sC 3<br />

+ 1 ≈ 2(g ds2 +g ds4 ) ⎢ ⎢ ⎡ sC 3 + 2g m3<br />

⎣ ⎦ ⎥ ⎥ ⎤<br />

sC 3 + g m3<br />

We see that there is a pole and a zero given as<br />

p 3 = - g m3<br />

C 3<br />

and z 3 = - 2g m3<br />

C 3<br />

+<br />

V o1<br />

-<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-15<br />

Influence of the Mirror Pole – Continued<br />

Fortunately, the presence of the zero tends to negate the effect of the pole. Generally,<br />

the pole and zero due to C 3 is greater than GB and will have very little influence on the<br />

stability of the two-stage op amp.<br />

The plot shown illustrates<br />

the case where these roots are<br />

less than GB and even then<br />

they have little effect on<br />

stability.<br />

In fact, they actually<br />

increase the phase margin<br />

slightly because GB is<br />

decreased.<br />

A vd (0) dB<br />

0dB<br />

Phase Shift<br />

0°<br />

45°<br />

90°<br />

135°<br />

180°<br />

F = 1<br />

C c ≠ 0<br />

C c = 0<br />

Magnitude influence of C 3<br />

C c = 0<br />

-45°/decade<br />

-6dB/octave<br />

GB<br />

log 10 (ω)<br />

-12dB/octave<br />

C c ≠ 0<br />

-45°/decade<br />

C c ≠ 0<br />

C<br />

Phase margi<br />

c = 0<br />

ignoring C<br />

Phase margin due to C 3<br />

3<br />

log 10 (ω)<br />

|p 1 | |p 3 ||z 3 | |p 2 |<br />

Fig. 120-17<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-16<br />

Summary of the Conditions for Stability of the Two-Stage Op Amp<br />

• Unity-gainbandwith is given as:<br />

⎛ 1 ⎞<br />

⎜<br />

⎟<br />

GB = A v (0)·|p 1 | = (g mI g mII R I R II g ⎟<br />

)·⎝⎜ mII R I R II C c<br />

= g mI<br />

⎛ 1 ⎞<br />

⎜<br />

⎟<br />

⎠<br />

C c<br />

= (g m1 g m2 R 1 R 2 g ⎟<br />

)·⎝⎜ m2 R 1 R 2 C c<br />

= g m1<br />

⎠<br />

C c<br />

• The requirement for 45° phase margin is:<br />

⎛ ω ⎞<br />

±180° - Arg[AF] = ±180° - tan-1⎜<br />

⎟<br />

⎝ |p1| - tan ⎛ ω ⎞<br />

-1⎜<br />

⎟<br />

⎠<br />

⎝ |p2| - tan ⎛ω⎞<br />

-1⎜<br />

⎟<br />

⎠<br />

⎝ z = 45° ⎠<br />

Let ω = GB and assume that z ≥ 10GB, therefore we get,<br />

⎛GB⎞<br />

±180° - tan-1⎜<br />

⎟<br />

⎝ |p1| - tan ⎛GB⎞<br />

-1⎜<br />

⎟<br />

⎠<br />

⎝ |p2| - tan ⎛GB⎞<br />

-1⎜<br />

⎟<br />

⎠<br />

⎝ z = 45° ⎠<br />

⎛GB⎞<br />

135° ≈ tan-1(Av(0)) + tan-1⎜<br />

⎟<br />

⎝ |p2| + tan ⎛GB⎞<br />

-1(0.1) = 90° + tan-1⎜<br />

⎟<br />

⎠<br />

⎝ |p2| + 5.7°<br />

⎠<br />

⎛GB⎞<br />

39.3° ≈ tan-1⎜<br />

⎟<br />

⎝ |p2| ⇒ GB<br />

⎠ |p 2 | = 0.818 ⇒ |p 2| ≥ 1.22GB<br />

• The requirement for 60° phase margin:<br />

|p2| ≥ 2.2GB if z ≥ 10GB<br />

• If 60° phase margin is required, then the following relationships apply:<br />

gm6<br />

Cc > 10g m1<br />

Cc ⇒ g m6 > 10gm1 and g m6<br />

C2 > 2.2g m1<br />

Cc ⇒ Cc > 0.22C2<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-17<br />

Controlling the Right-Half Plane Zero<br />

Why is the RHP zero a problem?<br />

Because it boosts the magnitude but lags the phase - the worst possible combination for<br />

stability.<br />

jω<br />

jω 3<br />

θ1 θ 2<br />

jω 2<br />

180° > θ 1 > θ 2 > θ 3<br />

jω 1<br />

θ3<br />

σ<br />

Fig. 430-01<br />

Solution of the problem:<br />

If a zero is caused by two paths to the output, then eliminate one of the paths.<br />

z 1<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-18<br />

Use of Buffer to Eliminate the Feedforward Path through the Miller Capacitor<br />

Model:<br />

The transfer<br />

function is given<br />

by the following<br />

equation,<br />

V o (s)<br />

V in (s) = (g mI )(g mII )(R I )(R II )<br />

1 + s[R I C I + R II C II + R I C c + g mII R I R II C c ] + s2[R I R II C II (C I + C c )]<br />

Using the technique as before to approximate p 1 and p 2 results in the following<br />

−1<br />

−1<br />

p 1 ≅ R I C I + R II C II + R I C c + g mII R I R II C c<br />

≅ g mII R I R II C c<br />

and<br />

C c<br />

+1<br />

C<br />

V c I<br />

+<br />

+<br />

v OUT V in gmI v in C I R I V out<br />

g mII V R I II C<br />

-<br />

II<br />

Inverting<br />

High-Gain<br />

Stage<br />

−g mII C c<br />

p 2 ≅ C II (C I + C c )<br />

Comments:<br />

Poles are approximately what they were before with the zero removed.<br />

For 45° phase margin, |p 2 | must be greater than GB<br />

For 60° phase margin, |p 2 | must be greater than 1.73GB<br />

V out<br />

-<br />

Fig. 430-02<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-19<br />

Use of Buffer with Finite Output Resistance to Eliminate the RHP Zero<br />

Assume that the unity-gain buffer has an output resistance of R o .<br />

Model:<br />

R o<br />

Inverting<br />

High-Gain<br />

Stage<br />

+1<br />

C c<br />

C<br />

V c I<br />

+<br />

+<br />

v OUT V in gmI v in C I R I R R o o<br />

V out<br />

g mII V R I II C<br />

-<br />

II<br />

-<br />

V out<br />

Fig. 430-03<br />

It can be shown that if the output resistance of the buffer amplifier, R o , is not neglected<br />

that another pole occurs at,<br />

−1<br />

p 4 ≅ R o [C I C c /(C I + C c )]<br />

and a LHP zero at<br />

z 2 ≅ −1<br />

R o C c<br />

Closer examination shows that if a resistor, called a nulling resistor, is placed in series<br />

with C c that the RHP zero can be eliminated or moved to the LHP.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-20<br />

Use of Nulling Resistor to Eliminate the RHP Zero (or turn it into a LHP zero) †<br />

C c<br />

R z<br />

C c R<br />

V z I<br />

+<br />

+<br />

Inverting v OUT V in g mI v in C I R V I out<br />

High-Gain<br />

g mII V I R II C<br />

-<br />

II<br />

-<br />

Stage<br />

Fig. 430-04<br />

Nodal equations:<br />

g mI V in + V I<br />

⎛ sC<br />

⎜ c<br />

⎞<br />

⎟<br />

R I<br />

+ sC I V I + ⎜<br />

⎟<br />

⎝<br />

1 + sC c R z<br />

(V I − V out ) = 0<br />

⎠<br />

g mII V I + V o<br />

⎛<br />

⎜<br />

sC c<br />

⎞<br />

⎟<br />

R II<br />

+ sC II V out + ⎜<br />

⎟<br />

⎝<br />

1 + sC c R z<br />

(V out − V I ) = 0<br />

⎠<br />

Solution:<br />

V out (s)<br />

V in (s) = a{1 − s[(C c/g mII ) − R z C c ]}<br />

1 + bs + cs2 + ds3<br />

where<br />

a = gmI g mII R I R II<br />

b = (C II + C c )R II + (C I + C c )R I + g mII R I R II C c + R z C c<br />

c = [R I R II (C I C II + C c C I + C c C II ) + R z C c (R I C I + R II C II )]<br />

d = R I R II R z C I C II C c<br />

†<br />

W,J. Parrish, "An Ion Implanted CMOS Amplifier for High Performance Active Filters", Ph.D. Dissertation, 1976, Univ. of CA., Santa Barbara.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-21<br />

Use of Nulling Resistor to Eliminate the RHP - Continued<br />

If R z is assumed to be less than R I or R II and the poles widely spaced, then the roots of the<br />

above transfer function can be approximated as<br />

−1<br />

−1<br />

p 1 ≅ (1 + g mII R II )R I C c<br />

≅ g mII R II R I C c<br />

−g mII C c<br />

p 2 ≅ C I C II + C c C I + C c C II<br />

≅ −g mII<br />

C II<br />

p 4 = −1<br />

R z C I<br />

and<br />

1<br />

z 1 = C c (1/g mII − R z )<br />

Note that the zero can be placed anywhere on the real axis.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-22<br />

Conceptual Illustration of the Nulling Resistor Approach<br />

V DD<br />

C c<br />

R II<br />

V out<br />

R z<br />

Fig. Fig. 430-05<br />

V''<br />

V'<br />

M6<br />

The output voltage, V out<br />

, can be written as<br />

⎛<br />

⎞<br />

⎜<br />

⎟<br />

-g m6 R II⎝ ⎜R z + 1<br />

⎡<br />

⎢<br />

sC c<br />

⎟<br />

⎠ R -R II<br />

II⎣ ⎢<br />

V out =<br />

R II + R z + 1 V’ +<br />

sC c<br />

R II + R z + 1 V” =<br />

sC c<br />

when V = V’ = V’’.<br />

Setting the numerator equal to zero and assuming g m6 = g mII gives,<br />

z 1 =<br />

1<br />

C c (1/g mII − R z )<br />

⎤<br />

⎥<br />

⎥<br />

⎦<br />

g m6 R z + g m6<br />

sC c<br />

- 1<br />

R II + R z + 1<br />

sC c<br />

V<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-23<br />

A <strong>Design</strong> Procedure that Allows the RHP Zero to Cancel the Output Pole, p 2<br />

We desire that z 1 = p 2 in terms of the previous notation.<br />

Therefore,<br />

1<br />

C c (1/g mII − R z ) = −g mII<br />

C II<br />

The value of R z can be found as<br />

-p 4 -p 2 -p 1 z 1<br />

⎛C ⎜ c + C II<br />

⎞<br />

⎟<br />

R z = ⎜<br />

⎟<br />

⎝<br />

C c<br />

(1/g mII )<br />

⎠<br />

With p 2 canceled, the remaining roots are p 1 and p 4 (the pole due to R z ) . For unity-gain<br />

stability, all that is required is that<br />

A v (0)<br />

|p 4 | > A v (0)|p 1 | = g mII R II R I C c<br />

= g mI<br />

C c<br />

and<br />

(1/R z C I ) > (g mI /C c ) = GB<br />

Substituting R z into the above inequality and assuming C II >> C c results in<br />

g mI<br />

C c > g mII<br />

C I C II<br />

This procedure gives excellent stability for a fixed value of C II (≈ C L ).<br />

Unfortunately, as C L changes, p 2 changes and the zero must be readjusted to cancel p 2 .<br />

jω<br />

σ<br />

Fig. 430-06<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-24<br />

Increasing the Magnitude of the Output Pole †<br />

The magnitude of the output pole , p 2 , can be increased by introducing gain in the Miller<br />

capacitor feedback path. For example,<br />

M10<br />

M11<br />

Fig. 6.2-15B<br />

M8<br />

M12<br />

C c<br />

M9<br />

V Bias<br />

V DD<br />

C gd6<br />

C<br />

r c<br />

M7<br />

ds8<br />

+ +<br />

v OUT<br />

Iin R 1 V 1 Vs8 R 2 C 2<br />

gm8Vs8<br />

- -<br />

M6<br />

V SS<br />

The resistors R 1 and R 2 are defined as<br />

1<br />

R 1 = g ds2 + g ds4 + g ds9<br />

and R 2 =<br />

g m6 V 1<br />

g m6 V 1<br />

+<br />

V out<br />

-<br />

C gd6 C c<br />

+<br />

+<br />

Iin R 1 V1 1<br />

R 2 C 2<br />

gm8 V s8<br />

- g m8 V s8 -<br />

1<br />

g ds6 + g ds7<br />

where transistors M2 and M4 are the output transistors of the first stage.<br />

Nodal equations:<br />

⎛ g<br />

⎜ m8 sC c<br />

⎞<br />

⎡<br />

⎤<br />

⎟<br />

⎢<br />

⎥<br />

I in = G 1 V 1 -g m8 V s8 = G 1 V 1 -⎜<br />

⎟<br />

⎝<br />

g m8 + sC c<br />

V out and 0 = g m6 V 1 + ⎢G ⎥<br />

⎣ 2 +sC 2 + g m8sC c<br />

g m8 +sC c<br />

V out<br />

⎠<br />

+<br />

V out<br />

-<br />

⎦<br />

†<br />

B.K. Ahuja, “An Improved Frequency Compensation Technique for CMOS Operational Amplifiers,” IEEE J. of Solid-State Circuits, Vol. SC-18,<br />

No. 6 (Dec. 1983) pp. 629-633.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-25<br />

Increasing the Magnitude of the Output Pole - Continued<br />

Solving for the transfer function V out /I in gives,<br />

V out<br />

I in<br />

⎛<br />

⎜<br />

= ⎜ ⎝<br />

-g m6<br />

⎞<br />

⎟<br />

⎟<br />

⎠<br />

G 1 G 2<br />

⎣<br />

⎢ ⎢⎢⎡<br />

⎛<br />

⎜<br />

⎜<br />

⎝<br />

⎡ C<br />

⎢ c<br />

1 + s⎢<br />

⎣<br />

g + C 2<br />

m8 G + C c<br />

2<br />

⎟<br />

⎟<br />

⎠<br />

1 + sC c ⎞<br />

g m8<br />

⎤<br />

⎥<br />

⎥<br />

⎦<br />

G + g m6C c<br />

2 G 1 G 2<br />

⎛<br />

⎜<br />

+ s2<br />

⎜ ⎝<br />

C c C 2<br />

g m8 G 2<br />

Using the approximate method of solving for the roots of the denominator gives<br />

-1<br />

-6<br />

p 1 = C c<br />

g m8<br />

+ C c<br />

G 2<br />

+ C 2<br />

G 2<br />

+ g m6C c<br />

≈ g m6 r ds<br />

2C c<br />

G 1 G 2<br />

and<br />

p 2 ≈<br />

- g m6r ds<br />

2C c<br />

6<br />

C c C 2<br />

g m8 G 2<br />

= g m8r ds<br />

2G 2<br />

⎛<br />

⎜<br />

6 ⎜ ⎝<br />

g m6<br />

⎞<br />

C 2<br />

⎟<br />

⎟<br />

⎠<br />

⎛<br />

⎜<br />

= ⎜ ⎝<br />

g m8 r ds<br />

⎞<br />

3 |p 2 ’|<br />

where all the various channel resistance have been assumed to equal r ds and p 2 ’ is the<br />

output pole for normal Miller compensation.<br />

Result:<br />

Dominant pole is approximately the same and the output pole is increased by ≈ g m r ds .<br />

⎟<br />

⎟<br />

⎠<br />

⎞<br />

⎟<br />

⎟<br />

⎠<br />

⎦ ⎥⎥⎥⎤<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-26<br />

Increasing the Magnitude of the Output Pole - Continued<br />

In addition there is a LHP zero at -g m8 /sC c and a RHP zero due to C gd6 (shown dashed<br />

in the model on Page 6.2-20) at g m6 /Cgd6.<br />

Roots are:<br />

jω<br />

-g m6 g m8 r ds -g m8 -1<br />

3C 2 C c g m6 r ds C c<br />

g m6<br />

C gd6<br />

σ<br />

Fig. 6.2-16A<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-27<br />

Concept Behind the Increasing of the Magnitude of the Output Pole<br />

V DD<br />

V DD<br />

r ds7<br />

C c<br />

v out<br />

1<br />

GB·C<br />

≈ 0<br />

M8<br />

c<br />

M6 C II<br />

3<br />

r ds7<br />

M6<br />

g m8 r ds8<br />

Fig. Fig. 430-08<br />

C II<br />

v out<br />

⎛ 3 ⎞ 3<br />

⎜<br />

⎟<br />

R out = r ds7 || ⎜<br />

⎟<br />

⎝<br />

g m6 g m8 r ds8<br />

≈<br />

⎠<br />

g m6 g m8 r ds8<br />

Therefore, the output pole is approximately,<br />

|p 2 | ≈ g m6g m8 r ds8<br />

3C II<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 2 (5/2/04) Page 6.2-28<br />

Identification of Poles from a Schematic<br />

1.) Most poles are equal to the reciprocal product of the resistance from a node to ground<br />

and the capacitance connected to that node.<br />

2.) Exceptions (generally due to feedback):<br />

a.) Negative feedback:<br />

C 3<br />

C 2 C 2<br />

-A<br />

-A<br />

C 1<br />

R 1<br />

b.) Positive feedback (A

Chapter 6 – Section 2 (5/2/04) Page 6.2-30<br />

Feedforward Compensation<br />

Use two parallel paths to achieve a LHP zero for lead compensation purposes.<br />

RHP Zero<br />

A<br />

C c<br />

LHP Zero<br />

-A<br />

C c<br />

LHP Zero using Follower<br />

C c<br />

V i<br />

V out<br />

V i<br />

V out<br />

Vi<br />

+1<br />

V out<br />

Inverting<br />

High Gain<br />

Amplifier<br />

C II<br />

R II<br />

Inverting<br />

High Gain<br />

Amplifier<br />

C II<br />

R II<br />

V out (s)<br />

V in (s) =<br />

+<br />

V i<br />

-<br />

AC c<br />

⎛ s + g<br />

⎜ mII /AC c<br />

C c + C II<br />

⎜ ⎝<br />

s + 1/[R II (C c + C II )]<br />

A<br />

⎞<br />

⎟<br />

⎟<br />

⎠<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

C c<br />

g mII V i<br />

C II<br />

R II<br />

+<br />

Vout<br />

- Fig.430-09<br />

To use the LHP zero for compensation, a compromise must be observed.<br />

• Placing the zero below GB will lead to boosting of the loop gain that could deteriorate<br />

the phase margin.<br />

• Placing the zero above GB will have less influence on the leading phase caused by the<br />

zero.<br />

Note that a source follower is a good candidate for the use of feedforward compensation.<br />

Chapter 6 – Section 2 (5/2/04) Page 6.2-31<br />

Self-Compensated Op Amps<br />

Self compensation occurs when the load capacitor is the compensation capacitor (can<br />

never be unstable for resistive feedback)<br />

|dB|<br />

-<br />

v in<br />

+<br />

R out (must be large)<br />

+<br />

G m<br />

v out<br />

-<br />

R out C L<br />

A v (0) dB<br />

Increasing C L<br />

-20dB/dec.<br />

Fig. 430-10<br />

Voltage gain:<br />

v out<br />

v in<br />

= A v (0) = G m R out<br />

Dominant pole:<br />

-1<br />

p 1 = R out C L<br />

Unity-gainbandwidth:<br />

GB = A v (0)·|p 1 | = G m<br />

C L<br />

Stability:<br />

Large load capacitors simply reduce GB but the phase is still 90° at GB.<br />

0dB<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

ω

Chapter 6 – Section 2 (5/2/04) Page 6.2-32<br />

Slew Rate of a Two-Stage CMOS Op Amp<br />

Remember that slew rate occurs when currents flowing in a capacitor become limited and<br />

is given as<br />

I lim = C dv C<br />

dt where v C is the voltage across the capacitor C.<br />

-<br />

v in >>0<br />

+<br />

M3<br />

M1<br />

+<br />

VBias<br />

-<br />

I 5<br />

M4<br />

M2<br />

M5<br />

V DD<br />

V SS<br />

Positive Slew Rate<br />

C c I5<br />

Assume a<br />

virtural<br />

ground<br />

M6<br />

I 6 I CL<br />

C L<br />

I 7<br />

M7<br />

v out<br />

-<br />

v in I 5 SR- = min⎢<br />

⎥<br />

⎣<br />

C c<br />

, I 7-I 5<br />

C L<br />

= I 5<br />

⎦ Cc if I 7 >>I 5 .<br />

Therefore, if C L is not too large and if I 7 is significantly greater than I 5 , then the slew rate<br />

of the two-stage op amp should be,<br />

SR = I 5<br />

Cc<br />

v out<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-1<br />

SECTION 6.3 - TWO-STAGE OP AMP DESIGN<br />

Unbuffered, Two-Stage CMOS Op Amp<br />

V DD<br />

M3<br />

M4<br />

C c<br />

M6<br />

v out<br />

Notation:<br />

- M1 M2<br />

v in<br />

+<br />

+<br />

VBias<br />

-<br />

M5<br />

V SS<br />

M7<br />

C L<br />

Fig. 6.3-1<br />

S i = W i<br />

L i<br />

= W/L of the ith transistor<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-2<br />

DC Balance Conditions for the Two-Stage Op Amp<br />

For best performance, keep all transistors in<br />

saturation.<br />

M4 is the only transistor that cannot be forced<br />

into saturation by internal connections or<br />

external voltages.<br />

Therefore, we develop conditions to force M4 to<br />

-<br />

be in saturation.<br />

1.) First assume that V SG4 = V SG6 . This will +<br />

cause “proper mirroring” in the M3-M4 mirror.<br />

Also, the gate and drain of M4 are at the same<br />

potential so that M4 is “guaranteed” to be in<br />

saturation.<br />

⎛S ⎜ 6<br />

⎞<br />

⎟<br />

2.) If V SG4 = V SG6 , then I 6 = ⎜ ⎟ ⎝<br />

S 4<br />

I<br />

⎠ 4<br />

⎛S ⎜ 7<br />

⎞ ⎛S ⎟ ⎜ 7<br />

⎞<br />

⎟<br />

3.) However, I 7 = ⎜ ⎟ ⎝<br />

S 5<br />

I 5 = ⎜ ⎟ ⎝<br />

S 5<br />

(2I 4 )<br />

⎠<br />

⎠<br />

V DD<br />

+<br />

V<br />

+ SG4 V SG6<br />

-<br />

-<br />

M6<br />

M3 M4 I 4 C c<br />

I 6<br />

M1 M2<br />

v in I 7<br />

I 5<br />

+<br />

M7<br />

VBias M5<br />

-<br />

4.) For balance, I 6 must equal I 7 ⇒ S 6<br />

S 4<br />

= 2S 7<br />

S 5<br />

called the “balance conditions”<br />

5.) So if the balance conditions are satisfied, then V DG4 = 0 and M4 is saturated.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

V SS<br />

C L<br />

v out<br />

Fig. 6.3-1A<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-3<br />

<strong>Design</strong> Relationships for the Two-Stage Op Amp<br />

Slew rate SR I 5<br />

= C c<br />

(Assuming I 7 >>I 5 and C L > C c )<br />

g m1<br />

2g m1<br />

First-stage gain A v1 = g ds2 + g = ds4 I 5 (λ 2 + λ 4 )<br />

g m6 g m6<br />

Second-stage gain A v2 = g ds6 + g = ds7 I 6 (λ 6 + λ 7 )<br />

Gain-bandwidth GB g m1<br />

= C c<br />

Output pole p −g m6<br />

2 = C L<br />

RHP zero z g m6<br />

1 = C c<br />

60° phase margin requires that g m6 = 2.2g m2 (C L /C c ) if all other roots are ≥ 10GB.<br />

Positive <strong>IC</strong>MR V in(max) = V DD −<br />

Negative <strong>IC</strong>MR V in(min) = V SS +<br />

I 5<br />

β 3 − |V T03 | (max) + V T1(min) )<br />

I 5<br />

β 1 + V T1(max) + V DS5 (sat)<br />

Saturation voltageV DS (sat) =<br />

2I DS<br />

β<br />

(all transistors are saturated)<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-4<br />

Op Amp Specifications<br />

The following design procedure assumes that specifications for the following parameters<br />

are given.<br />

1. Gain at dc, A v (0)<br />

2. Gain-bandwidth, GB<br />

3. Phase margin (or settling time)<br />

4. Input common-mode range, <strong>IC</strong>MR<br />

5. Load Capacitance, C L<br />

6. Slew-rate, SR<br />

-<br />

7. Output voltage swing<br />

+<br />

8. Power dissipation, P diss<br />

Max. <strong>IC</strong>MR<br />

and/or p 3 V DD<br />

+<br />

V V +<br />

V out (max)<br />

SG4 SG6 -<br />

-<br />

M6 g m6 or<br />

M3 M4<br />

C c I 6<br />

Proper Mirroring<br />

V SG4 =V SG6<br />

GB = g m1<br />

C c<br />

v out<br />

C<br />

v L<br />

in<br />

C M1 M2 c ≈ 0.2C L<br />

(PM = 60°)<br />

Min. <strong>IC</strong>MR I 5 I5 = SR·C c V out (min)<br />

+<br />

VBias<br />

-<br />

M5<br />

V SS<br />

M7<br />

Fig. 160-02<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-5<br />

Unbuffered Op Amp <strong>Design</strong> Procedure<br />

This design procedure assumes that the gain at dc (A v ), unity gain bandwidth (GB), input<br />

common mode range (V in (min) and V in (max)), load capacitance (C L ), slew rate (SR),<br />

settling time (T s ), output voltage swing (V out (max) and V out (min)), and power dissipation<br />

(P diss ) are given. Choose the smallest device length which will keep the channel<br />

modulation parameter constant and give good matching for current mirrors.<br />

1. From the desired phase margin, choose the minimum value for C c , i.e. for a 60° phase<br />

margin we use the following relationship. This assumes that z ≥ 10GB.<br />

C c > 0.22C L<br />

2. Determine the minimum value for the “tail current” (I 5 ) from the largest of the two<br />

values.<br />

I 5 = SR .C c or I 5 ≅ 10⎜ ⎛ V DD + |V SS |<br />

⎝ 2 . ⎠ ⎟⎞<br />

Ts<br />

3. <strong>Design</strong> for S 3 from the maximum input voltage specification.<br />

I 5<br />

S 3 = K' 3 [V DD − V in (max) − |V T03 |(max) + V T1 (min)]2<br />

4. Verify that the pole of M3 due to C gs3 and C gs4 (= 0.67W 3 L 3 C ox ) will not be dominant by<br />

assuming it to be greater than 10 GB<br />

g m3<br />

2C gs3<br />

> 10GB.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-6<br />

Unbuffered Op Amp <strong>Design</strong> Procedure - Continued<br />

5. <strong>Design</strong> for S 1 (S 2 ) to achieve the desired GB.<br />

g m1 = GB . C c → S g m2 2<br />

2 = K' 2 I 5<br />

6. <strong>Design</strong> for S 5 from the minimum input voltage. First calculate V DS5 (sat) then find S 5 .<br />

V DS5 (sat) = V in (min) − V SS −<br />

I 5<br />

2I 5<br />

β 1 −V T1 (max) ≥ 100 mV → S 5 = K' 5 [V DS5 (sat)]2<br />

7. Find S 6 by letting the second pole (p 2 ) be equal to 2.2 times GB and assuming that<br />

V SG4 = V SG6 .<br />

g m6 = 2.2g m2 (C L /C c ) and<br />

g m6 2K P 'S 6 I 6 S 6 I 6<br />

g m4<br />

= =<br />

2K P 'S 4 I 4<br />

S 4 I 4<br />

= S 6<br />

S 4<br />

→ S 6 = g m6<br />

g m4<br />

S 4<br />

8. Calculate I 6 from<br />

I g m6 2<br />

6 = 2K' 6 S 6<br />

Check to make sure that S 6 satisfies the V out (max) requirement and adjust as necessary.<br />

9. <strong>Design</strong> S 7 to achieve the desired current ratios between I 5 and I 6 .<br />

S 7 = (I 6 /I 5 )S 5 (Check the minimum output voltage requirements)<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-7<br />

Unbuffered Op Amp <strong>Design</strong> Procedure - Continued<br />

10. Check gain and power dissipation specifications.<br />

2g m2 g m6<br />

A v = I 5 (λ 2 + λ 3 )I 6 (λ 6 + λ 7 ) P diss = (I 5 + I 6 )(V DD + |V SS |)<br />

11. If the gain specification is not met, then the currents, I 5 and I 6 , can be decreased or<br />

the W/L ratios of M2 and/or M6 increased. The previous calculations must be rechecked<br />

to insure that they are satisfied. If the power dissipation is too high, then one can only<br />

reduce the currents I 5 and I 6 . Reduction of currents will probably necessitate increase of<br />

some of the W/L ratios in order to satisfy input and output swings.<br />

12. Simulate the circuit to check to see that all specifications are met.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-8<br />

Example 6.3-1 - <strong>Design</strong> of a Two-Stage Op Amp<br />

Using the material and device parameters given in Tables 3.1-1 and 3.1-2, design an<br />

amplifier similar to that shown in Fig. 6.3-1 that meets the following specifications.<br />

Assume the channel length is to be 1µm and the load capacitor is C L = 10pF.<br />

Av > 3000V/V V DD = 2.5V V SS = -2.5V<br />

GB = 5MHz SR > 10V/µs 60° phase margin<br />

V out range = ±2V <strong>IC</strong>MR = -1 to 2V P diss ≤ 2mW<br />

Solution<br />

1.) The first step is to calculate the minimum value of the compensation capacitor C c ,<br />

C c > (2.2/10)(10 pF) = 2.2 pF<br />

2.) Choose C c as 3pF. Using the slew-rate specification and C c calculate I 5 .<br />

I 5 = (3x10-12)(10x106) = 30 µA<br />

3.) Next calculate (W/L) 3 using <strong>IC</strong>MR requirements.<br />

(W/L) 3 =<br />

30x10-6<br />

(50x10 -6 )[2.5 − 2 − .85 + 0.55] 2 = 15 → (W/L) 3 = (W/L) 4 = 15<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-9<br />

Example 6.3-1 - Continued<br />

4.) Now we can check the value of the mirror pole, p 3 , to make sure that it is in fact<br />

greater than 10GB. Assume the C ox = 0.4fF/µm 2 . The mirror pole can be found as<br />

p -g m3 - 2K’ p S 3 I 3<br />

3 ≈ 2C gs3<br />

= 2(0.667)W 3 L 3 C ox<br />

= 2.81x10 9 (rads/sec)<br />

or 448 MHz. Thus, p 3 , is not of concern in this design because p 3 >> 10GB.<br />

5.) The next step in the design is to calculate g m1 to get<br />

g m1 = (5x106)(2π)(3x10-12) = 94.25µS<br />

Therefore, (W/L) 1 is<br />

(W/L) 1 = (W/L) g m1 2<br />

2 = 2K’ N I 1<br />

= (94.25) 2<br />

2·110·15 = 2.79 ≈ 3.0 ⇒ (W/L) 1 = (W/L) 2 = 3<br />

6.) Next calculate V DS5 ,<br />

V DS5 = (−1) − (−2.5) −<br />

30x10 -6<br />

110x10-6·3 - .85 = 0.35V<br />

Using V DS5 calculate (W/L) 5 from the saturation relationship.<br />

2(30x10-6)<br />

(W/L) 5 = (110x10-6)(0.35)2 = 4.49 ≈ 4.5 → (W/L) 5 = 4.5<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-10<br />

Example 6.3-1 - Continued<br />

7.) For 60° phase margin, we know that<br />

g m6 ≥ 10g m1 ≥ 942.5µS<br />

Assuming that g m6 = 942.5µS and knowing that g m4 = 150µS, we calculate (W/L) 6 as<br />

(W/L) 6 = 15 942.5x10 -6<br />

(150x10-6) = 94.25 ≈ 94<br />

8.) Calculate I 6 using the small-signal g m expression:<br />

(942.5x10-6)2<br />

I 6 = (2)(50x10-6)(94.25) = 94.5µA ≈ 95µA<br />

If we calculate (W/L) 6 based on V out (max), the value is approximately 15. Since 94<br />

exceeds the specification and maintains better phase margin, we will stay with (W/L) 6 =<br />

94 and I 6 = 95µA.<br />

With I 6 = 95µA the power dissipation is<br />

P diss = 5V·(30µA+95µA) = 0.625mW.<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-11<br />

Example 6.3-1 - Continued<br />

9.) Finally, calculate (W/L) 7<br />

⎛95x10-6⎞<br />

(W/L) 7 = 4.5 ⎜<br />

⎟<br />

⎝ 30x10-6 = 14.25 ≈ 14 → (W/L)<br />

⎠<br />

7 = 14<br />

Let us check the V out (min) specification although the W/L of M7 is so large that this is<br />

probably not necessary. The value of V out (min) is<br />

2·95<br />

V out (min) = V DS7 (sat) = 110·14 = 0.351V<br />

which is less than required. At this point, the first-cut design is complete.<br />

10.) Now check to see that the gain specification has been met<br />

(92.45x10-6)(942.5x10-6)<br />

A v = 15x10-6(.04 + .05)95x10-6(.04 + .05) = 7,697V/V<br />

which exceeds the specifications by a factor of two. .An easy way to achieve more gain<br />

would be to increase the W and L values by a factor of two which because of the<br />

decreased value of λ would multiply the above gain by a factor of 20.<br />

11.) The final step in the hand design is to establish true electrical widths and lengths<br />

based upon ∆L and ∆W variations. In this example ∆L will be due to lateral diffusion only.<br />

Unless otherwise noted, ∆W will not be taken into account. All dimensions will be<br />

rounded to integer values. Assume that ∆L = 0.2µm. Therefore, we have<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-12<br />

Example 6.3-1 - Continued<br />

W 1 = W 2 = 3(1 − 0.4) = 1.8 µm ≈ 2µm<br />

W 3 = W 4 = 15(1 − 0.4) = 9µm<br />

W 5 = 4.5(1 - 0.4) = 2.7µm ≈ 3µm<br />

W 6 = 94(1 - 0.4) = 56.4µm ≈ 56µm<br />

W 7 = 14(1 - 0.4) = 8.4 ≈ 8µm<br />

The figure below shows the results of the first-cut design. The W/L ratios shown do not<br />

account for the lateral diffusion discussed above. The next phase requires simulation.<br />

30µA<br />

4.5µm<br />

1µm<br />

15µm<br />

1µm<br />

M3<br />

M4<br />

M1 M2<br />

-<br />

3µm 3µm<br />

v 1µm 1µm<br />

in<br />

+<br />

30µA<br />

M8<br />

M5<br />

V DD = 2.5V<br />

4.5µm<br />

1µm<br />

15µm<br />

1µm<br />

V SS = -2.5V<br />

C c = 3pF<br />

95µA<br />

M6<br />

M7<br />

94µm<br />

1µm<br />

14µm<br />

1µm<br />

v out<br />

C L =<br />

10pF<br />

Fig. 6.3-3<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-13<br />

Incorporating the Nulling Resistor into the Miller Compensated Two-Stage Op Amp<br />

Circuit:<br />

V DD<br />

M11 M3<br />

M4 V B<br />

V A<br />

M10<br />

C M<br />

V C v v in +<br />

in -<br />

M1 M2<br />

M8<br />

C c<br />

M6<br />

vout<br />

C L<br />

I Bias<br />

M12<br />

M9<br />

M5<br />

M7<br />

We saw earlier that the roots were:<br />

p g m2 g m1<br />

1 = − A v C = − c A v C c<br />

1<br />

p 4 = − R z C I<br />

z 1 =<br />

p 2 = − g m6<br />

C L<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

V SS<br />

−1<br />

R z C c − C c /g m6<br />

Fig. 160-03<br />

where A v = g m1 g m6 R I R II .<br />

(Note that p 4 is the pole resulting from the nulling resistor compensation technique.)

Chapter 6 – Section 3 (5/2/04) Page 6.3-14<br />

<strong>Design</strong> of the Nulling Resistor (M8)<br />

In order to place the zero on top of the second pole (p 2 ), the following relationship must<br />

hold<br />

R 1 ⎛C ⎜ L + C c<br />

⎞ ⎛C ⎟ ⎜ c +C L<br />

⎞<br />

⎟<br />

1<br />

z = g m6<br />

⎜<br />

⎟<br />

⎝<br />

C c<br />

= ⎜ ⎟<br />

⎠ ⎝<br />

C c ⎠ 2K’ P S 6 I 6<br />

The resistor, R z , is realized by the transistor M8 which is operating in the active region<br />

because the dc current through it is zero. Therefore, R z , can be written as<br />

R ∂v DS8<br />

z =<br />

⎢<br />

∂i D8 V DS8 =0 = 1<br />

K’ P S 8 (V SG8 -|V TP |)<br />

The bias circuit is designed so that voltage V A is equal to V B .<br />

∴ |V GS10 | − |V T | = |V GS8 | − |V T |⇒ V SG11 = V SG6 ⇒<br />

⎝<br />

⎜<br />

In the saturation region<br />

2(I 10 )<br />

|V GS10 | − |V T | = K' P (W 10 /L 10 ) = |V GS8| − |V T |<br />

∴ R z =<br />

1<br />

K’ P S 8<br />

K’ P S 10<br />

2I 10<br />

= 1 S 8<br />

S 10<br />

2K’ P I 10<br />

Equating the two expressions for R z gives<br />

W 8<br />

⎞<br />

L 8<br />

⎛<br />

⎜<br />

⎜<br />

⎝<br />

W 11<br />

⎞<br />

L 11<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

⎟<br />

⎟<br />

⎠<br />

⎛<br />

⎜<br />

= ⎜ ⎝<br />

C c<br />

⎛<br />

⎜<br />

⎞<br />

⎟<br />

⎟<br />

⎠<br />

⎟<br />

⎟<br />

⎠<br />

⎛<br />

⎜<br />

= ⎜ ⎝<br />

I 10<br />

⎞<br />

I 6<br />

⎟<br />

⎟<br />

⎠<br />

W 6<br />

⎞<br />

L 6<br />

⎛<br />

⎜<br />

⎜ ⎝<br />

C L + C c<br />

S 10 S 6 I 6<br />

I 10<br />

⎟<br />

⎟<br />

⎠<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-15<br />

Example 6.3-2 - RHP Zero Compensation<br />

Use results of Ex. 6.3-1 and design compensation circuitry so that the RHP zero is<br />

moved from the RHP to the LHP and placed on top of the output pole p 2 . Use device data<br />

given in Ex. 6.3-1.<br />

Solution<br />

The task at hand is the design of transistors M8, M9, M10, M11, and bias current I 10 .<br />

The first step in this design is to establish the bias components. In order to set V A equal to<br />

V B , thenV SG11 must equal V SG6 . Therefore,<br />

S 11 = (I 11 /I 6 )S 6<br />

Choose I 11 = I 10 = I 9 = 15µA which gives S 11 = (15µA/95µA)94 = 14.8 ≈ 15.<br />

The aspect ratio of M10 is essentially a free parameter, and will be set equal to 1.<br />

There must be sufficient supply voltage to support the sum of V SG11 , V SG10 , and V DS9 .<br />

The ratio of I 10 /I 5 determines the (W/L) of M9. This ratio is<br />

(W/L) 9 = (I 10 /I 5 )(W/L) 5 = (15/30)(4.5) = 2.25 ≈ 2<br />

Now (W/L) 8 is determined to be<br />

⎛<br />

(W/L) 8 = ⎜<br />

⎝<br />

3pF<br />

3pF+10pF<br />

⎞<br />

⎟<br />

⎠<br />

1·94·95µA<br />

15µA = 5.63 ≈ 6<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-16<br />

Example 6.3-2 - Continued<br />

It is worthwhile to check that the RHP zero has been moved on top of p 2 . To do this,<br />

first calculate the value of R z . V SG8 must first be determined. It is equal to V SG10 , which is<br />

V SG10 =<br />

2I 10<br />

K’ P S 10<br />

+ |V TP | =<br />

2·15<br />

50·1 + 0.7 = 1.474V<br />

Next determine R z .<br />

1<br />

R z = K’ P S 8 (V SG10 -|V TP |) = 106<br />

50·5.63(1.474-.7) = 4.590kΩ<br />

The location of z 1 is calculated as<br />

−1<br />

z 1 =<br />

(4.590 x 103)(3x10 -12 ) −<br />

The output pole, p 2 , is<br />

3x10 -12 = -94.46x106 rads/sec<br />

942.5x10 -6<br />

p 2 = 942.5x10 -6<br />

10x10 -12 = -94.25x10 6 rads/sec<br />

Thus, we see that for all practical purposes, the output pole is canceled by the zero<br />

that has been moved from the RHP to the LHP.<br />

The results of this design are summarized below.<br />

W 8 = 6 µm W 9 = 2 µm W 10 = 1 µm W 11 = 15 µm<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-17<br />

An Alternate Form of Nulling Resistor<br />

To cancel p 2 ,<br />

z 1 = p 2 → R z = C c+C L 1<br />

g m6A C =<br />

C g m6B<br />

Which gives<br />

⎛<br />

⎜<br />

g m6B = g m6A⎝ ⎜<br />

C c<br />

⎞<br />

⎟<br />

⎟<br />

⎠<br />

C c +C L<br />

In the previous example,<br />

g m6A = 942.5µS, C c = 3pF<br />

and C L = 10pF.<br />

Choose I 6B = 10µA to get<br />

or<br />

g m6B = g m6AC c<br />

C c + C L<br />

→<br />

W 6B<br />

L 6B<br />

⎛<br />

= ⎜<br />

⎝<br />

3 ⎞<br />

⎟<br />

⎠<br />

I 13 2 6A W 6A<br />

I 6B<br />

L 6A<br />

⎛<br />

= ⎜<br />

⎝<br />

2K P W 6B I 6B<br />

L 6B<br />

- M1 M2<br />

v in<br />

+<br />

+<br />

VBias<br />

-<br />

M3<br />

M4<br />

M5<br />

V DD<br />

M11<br />

M6B<br />

M8<br />

V SS<br />

M10<br />

C c<br />

M9<br />

M6<br />

v out<br />

C L<br />

M7<br />

Fig. 6.3-4A<br />

3 ⎞<br />

⎟<br />

13 2 ⎛<br />

⎜<br />

⎠ ⎝<br />

⎟<br />

⎠<br />

⎛<br />

= ⎜<br />

⎝<br />

C c<br />

C c +C L<br />

⎞<br />

⎟<br />

⎠<br />

2K P W 6A I D6<br />

L 6A<br />

95⎞<br />

10 (94) = 47.6 → W 6B = 48µm<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-18<br />

Programmability of the Two-Stage Op Amp<br />

The following relationships depend on the bias<br />

current, I bias , in the following manner and allow for<br />

programmability after fabrication.<br />

A v (0) = g mI g mII R I R II ∝ 1<br />

I Bias<br />

GB = g mI<br />

C ∝ I Bias<br />

c<br />

P diss = (V DD +|V SS |)(1+K 1 +K 2 )I Bias ∝ I bias<br />

SR = K 1I Bias<br />

C c<br />

∝ I Bias<br />

1<br />

R out = 2λK 2 I Bias<br />

∝ 1<br />

I Bias<br />

1<br />

|p 1 | = g mII R I R II C c<br />

∝ I Bias 2<br />

I<br />

∝ I 1.5 Bias Bias<br />

|z| = g mII<br />

C c<br />

∝ I Bias<br />

Illustration of the I bias dependence →<br />

103<br />

102<br />

101<br />

100<br />

P diss and SR<br />

-<br />

v in<br />

M1 M2<br />

+<br />

IBias<br />

K 1 IBias K 2IBias<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004<br />

|p 1 |<br />

GB and z<br />

M3<br />

10-1<br />

Ao and R out<br />

10-2<br />

10-3<br />

1 10 100<br />

I Bias Fig. 160-05<br />

I Bias (ref)<br />

V DD<br />

M4<br />

M5<br />

V SS<br />

M6<br />

M7<br />

v out<br />

Fig. 6.3-04D<br />

Chapter 6 – Section 3 (5/2/04) Page 6.3-19<br />

Simulation of the Electrical <strong>Design</strong><br />

Area of source or drain = AS = AD = W[L1 + L2 + L3]<br />

where<br />

L1 = Minimum allowable distance between the contact in the S/D and the<br />

polysilicon (5µm)<br />

L2 = Width of a minimum size contact (5µm)<br />

L3 = Minimum allowable distance from contact in S/D to edge of S/D (5µm)<br />

∴ AS = AD = Wx15µm<br />

Perimeter of the source or drain = PD = PS = 2W + 2(L1+L2+L3)<br />

∴ PD = PS = 2W + 30µm<br />

Illustration:<br />

L3 L2 L1 L1 L2 L3<br />

Poly<br />

W<br />

Diffusion<br />

Diffusion<br />

L<br />

Fig. 6.3-5<br />

CMOS <strong>Analog</strong> Circuit <strong>Design</strong> © P.E. Allen - 2004

Chapter 6 – Section 3 (5/2/04) Page 6.3-20<br />

5-to-1 Current Mirror with Different Physical Performances<br />

Input<br />

;;;<br />

;;<br />

;; Output<br />

;;;<br />

;;<br />

;;; Metal<br />

;;;<br />

;;<br />

;;;<br />

;;;<br />

;;<br />

;;<br />

(a)<br />

;;;;;<br />

;;;;;;<br />

;;;;;;<br />

;;;;(b)<br />

;;<br />

1<br />

Poly<br />

Diffusion<br />

Contacts<br />

Ground<br />

Output<br />

; Input<br />

Ground<br />

Figure 6.3-6 The layout of a 5-to-1 current mirror. (a) Layout which minimizes<br />

area at the sacrifice of matching. (b) Layout which optimizes matching.<br />