Buffer Insertion Basics - Computer Engineering & Systems Group ...

Buffer Insertion Basics - Computer Engineering & Systems Group ...

Buffer Insertion Basics - Computer Engineering & Systems Group ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

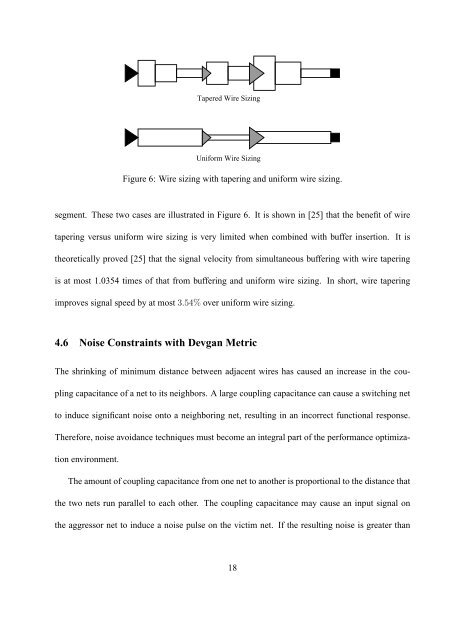

Tapered Wire Sizing<br />

Uniform Wire Sizing<br />

Figure 6: Wire sizing with tapering and uniform wire sizing.<br />

segment. These two cases are illustrated in Figure 6. It is shown in [25] that the benefit of wire<br />

tapering versus uniform wire sizing is very limited when combined with buffer insertion. It is<br />

theoretically proved [25] that the signal velocity from simultaneous buffering with wire tapering<br />

is at most 1.0354 times of that from buffering and uniform wire sizing. In short, wire tapering<br />

improves signal speed by at most 3.54% over uniform wire sizing.<br />

4.6 Noise Constraints with Devgan Metric<br />

The shrinking of minimum distance between adjacent wires has caused an increase in the coupling<br />

capacitance of a net to its neighbors. A large coupling capacitance can cause a switching net<br />

to induce significant noise onto a neighboring net, resulting in an incorrect functional response.<br />

Therefore, noise avoidance techniques must become an integral part of the performance optimization<br />

environment.<br />

The amount of coupling capacitance from one net to another is proportional to the distance that<br />

the two nets run parallel to each other. The coupling capacitance may cause an input signal on<br />

the aggressor net to induce a noise pulse on the victim net. If the resulting noise is greater than<br />

18