Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

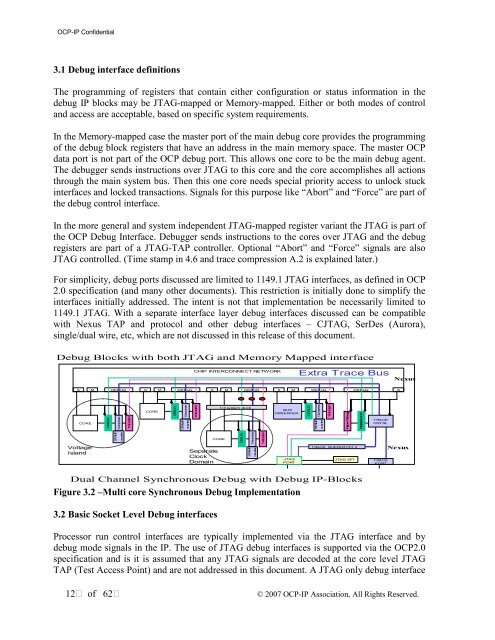

3.1 <strong>Debug</strong> interface definitions<br />

The programming of registers that contain either configuration or status information in the<br />

debug <strong>IP</strong> blocks may be JTAG-mapped or Memory-mapped. Either or both modes of control<br />

and access are acceptable, based on specific system requirements.<br />

In the Memory-mapped case the master port of the main debug core provides the programming<br />

of the debug block registers that have an address in the main memory space. The master <strong>OCP</strong><br />

data port is not part of the <strong>OCP</strong> debug port. This allows one core to be the main debug agent.<br />

The debugger sends instructions over JTAG to this core and the core accomplishes all actions<br />

through the main system bus. Then this one core needs special priority access to unlock stuck<br />

interfaces and locked transactions. Signals for this purpose like “Abort” and “Force” are part of<br />

the debug control interface.<br />

In the more general and system independent JTAG-mapped register variant the JTAG is part of<br />

the <strong>OCP</strong> <strong>Debug</strong> <strong>Interface</strong>. <strong>Debug</strong>ger sends instructions to the cores over JTAG and the debug<br />

registers are part of a JTAG-TAP controller. Optional “Abort” and “Force” signals are also<br />

JTAG controlled. (Time stamp in 4.6 and trace compression A.2 is explained later.)<br />

For simplicity, debug ports discussed are limited to 1149.1 JTAG interfaces, as defined in <strong>OCP</strong><br />

2.0 specification (and many other documents). This restriction is initially done to simplify the<br />

interfaces initially addressed. The intent is not that implementation be necessarily limited to<br />

1149.1 JTAG. With a separate interface layer debug interfaces discussed can be compatible<br />

with Nexus TAP and protocol and other debug interfaces – CJTAG, SerDes (Aurora),<br />

single/dual wire, etc, which are not discussed in this release of this document.<br />

<strong>Debug</strong> Blocks with both JTAG and Memory Mapped interface<br />

CH<strong>IP</strong> INTERCONNECT NETWORK<br />

Extra Trace Bus<br />

Nexus<br />

S<br />

M DEBUG S M DEBUG S M DEBUG S M DEBUG<br />

DEBUG<br />

S<br />

CORE<br />

DEBUG<br />

Compress<br />

TRIGGER<br />

CORE<br />

DEBUG<br />

STAMP<br />

Compress<br />

counter<br />

TRIGGER<br />

1/3 system clock<br />

BUS<br />

OBSERVER<br />

DEBUG<br />

STAMP<br />

Compress<br />

counter<br />

TRIGGER<br />

Hyper <strong>Debug</strong><br />

DEBUGCntrl<br />

TRACE<br />

CNTRL<br />

Voltage<br />

Island<br />

STAMP<br />

counter<br />

Separate<br />

Clock<br />

Domain<br />

CORE<br />

DEBUG<br />

STAMP<br />

Compress<br />

counter<br />

TRIGGER<br />

JTAG<br />

PORT<br />

TRACE BUFFER Ch1,2<br />

JTAG DFT<br />

TRACE<br />

PORT<br />

Nexus<br />

Dual Channel Synchronous <strong>Debug</strong> with <strong>Debug</strong> <strong>IP</strong>-Blocks<br />

Figure 3.2 –Multi core Synchronous <strong>Debug</strong> Implementation<br />

3.2 Basic Socket Level <strong>Debug</strong> interfaces<br />

Processor run control interfaces are typically implemented via the JTAG interface and by<br />

debug mode signals in the <strong>IP</strong>. The use of JTAG debug interfaces is supported via the <strong>OCP</strong>2.0<br />

specification and is it is assumed that any JTAG signals are decoded at the core level JTAG<br />

TAP (Test Access Point) and are not addressed in this document. A JTAG only debug interface<br />

12 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.