Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

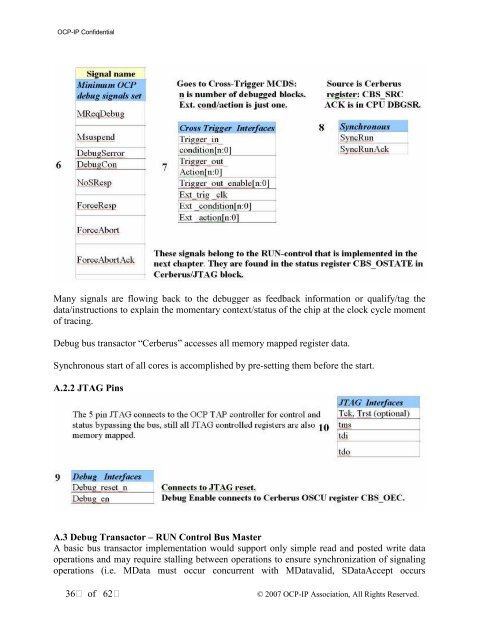

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

Many signals are flowing back to the debugger as feedback information or qualify/tag the<br />

data/instructions to explain the momentary context/status of the chip at the clock cycle moment<br />

of tracing.<br />

<strong>Debug</strong> bus transactor “Cerberus” accesses all memory mapped register data.<br />

Synchronous start of all cores is accomplished by pre-setting them before the start.<br />

A.2.2 JTAG Pins<br />

A.3 <strong>Debug</strong> Transactor – RUN Control Bus Master<br />

A basic bus transactor implementation would support only simple read and posted write data<br />

operations and may require stalling between operations to ensure synchronization of signaling<br />

operations (i.e. MData must occur concurrent with MDatavalid, SDataAccept occurs<br />

36 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.