Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

Control signals in case of gated clock domains and voltage domains in that the continuity and<br />

functionality is not interrupted if any <strong>IP</strong> block on the bus switches off clocks or voltages. By<br />

proper definition of the idle levels a blocking of the debug system shall not happen if one core<br />

or <strong>IP</strong> block goes into sleep mode.<br />

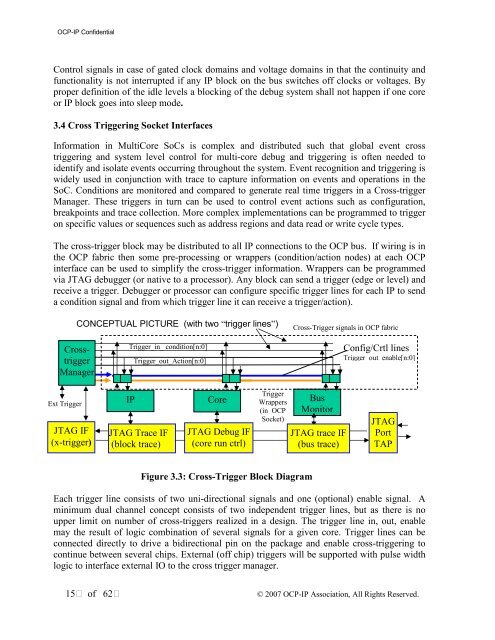

3.4 Cross Triggering Socket <strong>Interface</strong>s<br />

Information in Multi<strong>Core</strong> SoCs is complex and distributed such that global event cross<br />

triggering and system level control for multi-core debug and triggering is often needed to<br />

identify and isolate events occurring throughout the system. Event recognition and triggering is<br />

widely used in conjunction with trace to capture information on events and operations in the<br />

SoC. Conditions are monitored and compared to generate real time triggers in a Cross-trigger<br />

Manager. These triggers in turn can be used to control event actions such as configuration,<br />

breakpoints and trace collection. More complex implementations can be programmed to trigger<br />

on specific values or sequences such as address regions and data read or write cycle types.<br />

The cross-trigger block may be distributed to all <strong>IP</strong> connections to the <strong>OCP</strong> bus. If wiring is in<br />

the <strong>OCP</strong> fabric then some pre-processing or wrappers (condition/action nodes) at each <strong>OCP</strong><br />

interface can be used to simplify the cross-trigger information. Wrappers can be programmed<br />

via JTAG debugger (or native to a processor). Any block can send a trigger (edge or level) and<br />

receive a trigger. <strong>Debug</strong>ger or processor can configure specific trigger lines for each <strong>IP</strong> to send<br />

a condition signal and from which trigger line it can receive a trigger/action).<br />

CONCEPTUAL PICTURE (with two “trigger lines”)<br />

Cross-Trigger signals in <strong>OCP</strong> fabric<br />

Crosstrigger<br />

Manager<br />

Trigger_in_ condition[n:0]<br />

Trigger_out_Action[n:0]<br />

Config/Crtl lines<br />

Trigger_out_enable[n:0]<br />

Ext Trigger<br />

JTAG IF<br />

(x-trigger)<br />

Trigger<br />

<strong>IP</strong> <strong>Core</strong> Wrappers<br />

Bus<br />

Monitor<br />

JTAG Trace IF<br />

(block trace)<br />

JTAG <strong>Debug</strong> IF<br />

(core run ctrl)<br />

(in <strong>OCP</strong><br />

Socket)<br />

JTAG trace IF<br />

(bus trace)<br />

JTAG<br />

Port<br />

TAP<br />

Figure 3.3: Cross-Trigger Block Diagram<br />

Each trigger line consists of two uni-directional signals and one (optional) enable signal. A<br />

minimum dual channel concept consists of two independent trigger lines, but as there is no<br />

upper limit on number of cross-triggers realized in a design. The trigger line in, out, enable<br />

may the result of logic combination of several signals for a given core. Trigger lines can be<br />

connected directly to drive a bidirectional pin on the package and enable cross-triggering to<br />

continue between several chips. External (off chip) triggers will be supported with pulse width<br />

logic to interface external IO to the cross trigger manager.<br />

15 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.