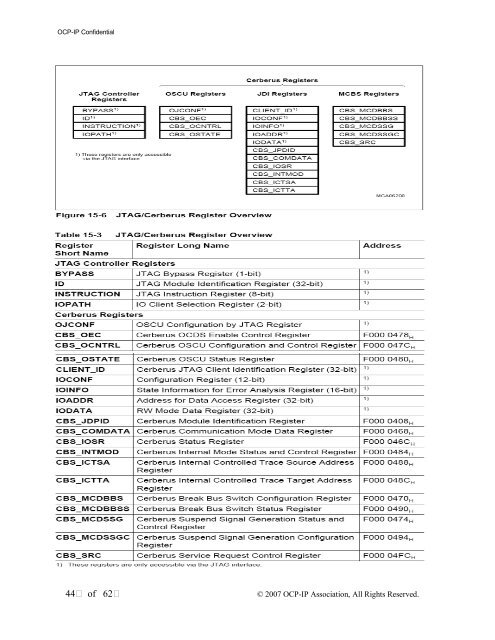

<strong>OCP</strong>-<strong>IP</strong> Confidential 44 of 62 © 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.

<strong>OCP</strong>-<strong>IP</strong> Confidential <strong>OCP</strong>- MCDS Wrappers 2 debug channels A, B active out of N possible channels CH<strong>IP</strong> PC Software <strong>OCP</strong> Data/Addr Socket <strong>OCP</strong> Data Wrapper Memory Mapped Access (can be extended for more than 2 channels) SYS <strong>Debug</strong> MCDS <strong>Core</strong>1 <strong>Core</strong>2 <strong>Core</strong>3 <strong>Debug</strong> Regs <strong>Debug</strong> Regs <strong>Debug</strong> Regs <strong>OCP</strong> Trace Compress <strong>OCP</strong> <strong>Debug</strong> Wrapper <strong>OCP</strong> Interconnect <strong>OCP</strong>-Wrapper <strong>Core</strong> N … Dual Trace <strong>Core</strong> 1 <strong>Core</strong> N … Cross Trigger <strong>Core</strong> 1 Cerberus Run Control Socket Power, Security Socket Trace Socket Cross-Trigger Socket OSCU System Control JTAG <strong>Debug</strong> <strong>Interface</strong> Multi-<strong>Core</strong> Break Switch Breakpoints, synchronized start/stop <strong>OCP</strong> <strong>Debug</strong> Socket TAP TRACE ICE BOX JTAG & TRACE (DAP) <strong>OCP</strong>-<strong>IP</strong> CONFIDENTIAL – NOT TO BE DUPLICATED 4 Figure A.5 : <strong>OCP</strong>/MCDS Wrappers A B A B A B Trace A B JTAG API RDI USB Ethernet Parallel Serial <strong>Debug</strong> Server API <strong>Core</strong>1 <strong>Debug</strong> <strong>Core</strong>2 <strong>Debug</strong> <strong>Core</strong>3 <strong>Debug</strong> <strong>OCP</strong> <strong>Debug</strong> <strong>Interface</strong> and OSI-Model Borderlines OSI for <strong>Debug</strong> Information: PHYSICAL LAYER | TRANSPORT LAYER CH<strong>IP</strong> CORE N CORE 1 CORES <strong>OCP</strong>- INTERFACE <strong>OCP</strong>- INTERCONNECT <strong>OCP</strong>- INTERFACE REGISTER CUSTOM CUSTOM EXTERNAL JTAG TRANSFER DEBUG DEBUG INTERFACE PROTOCOL LOGIC REGISTERS TRACE - <strong>OCP</strong> DATA - <strong>OCP</strong> ADDRESS <strong>OCP</strong>-Bus MCDS MCDS MCDS INTERFACE - <strong>OCP</strong> CONTROL (SRESP, WIDTH, …) Observer Trace Regs or Bus Observer <strong>Core</strong> <strong>Debug</strong> Regs TAP <strong>OCP</strong> - Wrapper - <strong>OCP</strong> DATA - <strong>OCP</strong> ADDRESS - <strong>OCP</strong> CONTROL (SRESP, WIDTH, …) 4 7 10 5 8 6 9 <strong>OCP</strong>-DATA SOCKET <strong>OCP</strong>-DATA SOCKET TAP <strong>OCP</strong>- JTAG <strong>OCP</strong>- TRACE <strong>OCP</strong>-TRIGGER <strong>OCP</strong>-RUN CONTROL EXT ENDED DEBUG SIGNALS 10 4 5 7 8 6 9 <strong>OCP</strong> - Wrapper Wrapper ch0 ch1 JTAG Data r/w Cross Trigger Run- Control <strong>OCP</strong> <strong>Debug</strong> Signal Classes and their Mapping on the MCDS <strong>Interface</strong> Instruction Trace (data port / mode port) 0 base address [31:0] / base_mode [2:0] = (idle, valid, forget, invalid); 1 address increment [3:0] / inc_mode [2:0] = (idle, valid, forget, invalid); Data Trace (data port / mode port) 2 address [31:0] / addr_mode [2:0] = (idle, valid, forget, invalid); 3 data [31:0] / data_mode [2:0]=(idle, byte, h_word, word, d_word, forget, none, invalid); 4 control [31:0] / control_mode [2:0] = (idle, write, read, forget); 5 ownership id [7:0] / id_mode [2:0] = (idle, valid, forget, invalid); Bus-Trace Instructions Data MCDS SW-Register <strong>Interface</strong> TAP TRACE JTAG 3 1 2 1 2 3 CERBERUS Bus-Transactor TAP Manufacturing <strong>OCP</strong>-<strong>IP</strong> CONFIDENTIAL – NOT TO BE DUPLICATED Figure A.6 : <strong>OCP</strong> <strong>Debug</strong> <strong>Interface</strong> and OSI Model Borderlines. See page 35, 36, 41, 44. http://en.wikipedia.org/wiki/OSI_model 45 of 62 © 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.