Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

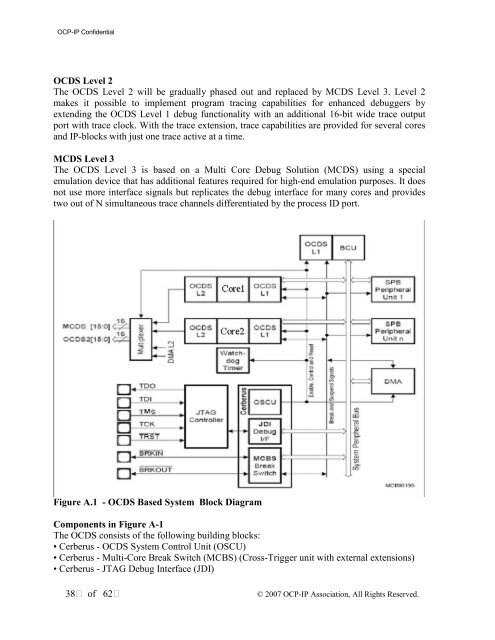

OCDS Level 2<br />

The OCDS Level 2 will be gradually phased out and replaced by MCDS Level 3. Level 2<br />

makes it possible to implement program tracing capabilities for enhanced debuggers by<br />

extending the OCDS Level 1 debug functionality with an additional 16-bit wide trace output<br />

port with trace clock. With the trace extension, trace capabilities are provided for several cores<br />

and <strong>IP</strong>-blocks with just one trace active at a time.<br />

MCDS Level 3<br />

The OCDS Level 3 is based on a Multi <strong>Core</strong> <strong>Debug</strong> Solution (MCDS) using a special<br />

emulation device that has additional features required for high-end emulation purposes. It does<br />

not use more interface signals but replicates the debug interface for many cores and provides<br />

two out of N simultaneous trace channels differentiated by the process ID port.<br />

Figure A.1 - OCDS Based System Block Diagram<br />

Components in Figure A-1<br />

The OCDS consists of the following building blocks:<br />

• Cerberus - OCDS System Control Unit (OSCU)<br />

• Cerberus - Multi-<strong>Core</strong> Break Switch (MCBS) (Cross-Trigger unit with external extensions)<br />

• Cerberus - JTAG <strong>Debug</strong> <strong>Interface</strong> (JDI)<br />

38 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.