Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Open Core Protocol Debug Interface Specification rev 1.0 - OCP-IP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>OCP</strong>-<strong>IP</strong> Confidential<br />

does place limitations on the ability to interface debug components on different cores and to set<br />

up and synchronize an <strong>OCP</strong> system into a debug mode.<br />

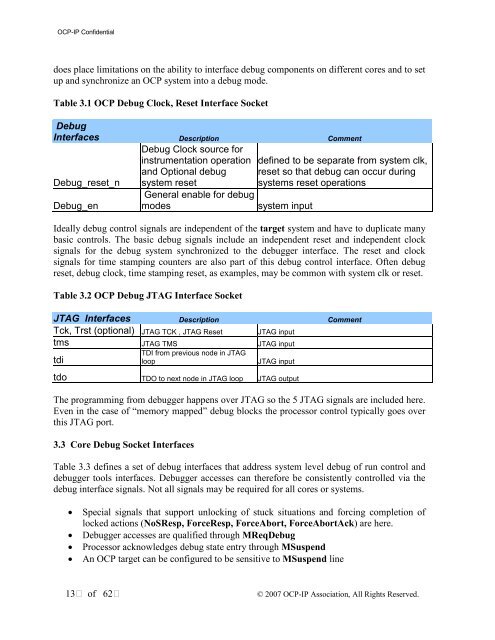

Table 3.1 <strong>OCP</strong> <strong>Debug</strong> Clock, Reset <strong>Interface</strong> Socket<br />

<strong>Debug</strong><br />

<strong>Interface</strong>s Description Comment<br />

<strong>Debug</strong>_reset_n<br />

<strong>Debug</strong>_en<br />

<strong>Debug</strong> Clock source for<br />

instrumentation operation<br />

and Optional debug<br />

system reset<br />

General enable for debug<br />

modes<br />

defined to be separate from system clk,<br />

reset so that debug can occur during<br />

systems reset operations<br />

system input<br />

Ideally debug control signals are independent of the target system and have to duplicate many<br />

basic controls. The basic debug signals include an independent reset and independent clock<br />

signals for the debug system synchronized to the debugger interface. The reset and clock<br />

signals for time stamping counters are also part of this debug control interface. Often debug<br />

reset, debug clock, time stamping reset, as examples, may be common with system clk or reset.<br />

Table 3.2 <strong>OCP</strong> <strong>Debug</strong> JTAG <strong>Interface</strong> Socket<br />

JTAG <strong>Interface</strong>s Description Comment<br />

Tck, Trst (optional) JTAG TCK , JTAG Reset JTAG input<br />

tms JTAG TMS JTAG input<br />

TDI from p<strong>rev</strong>ious node in JTAG<br />

tdi<br />

loop<br />

JTAG input<br />

tdo TDO to next node in JTAG loop JTAG output<br />

The programming from debugger happens over JTAG so the 5 JTAG signals are included here.<br />

Even in the case of “memory mapped” debug blocks the processor control typically goes over<br />

this JTAG port.<br />

3.3 <strong>Core</strong> <strong>Debug</strong> Socket <strong>Interface</strong>s<br />

Table 3.3 defines a set of debug interfaces that address system level debug of run control and<br />

debugger tools interfaces. <strong>Debug</strong>ger accesses can therefore be consistently controlled via the<br />

debug interface signals. Not all signals may be required for all cores or systems.<br />

• Special signals that support unlocking of stuck situations and forcing completion of<br />

locked actions (NoSResp, ForceResp, ForceAbort, ForceAbortAck) are here.<br />

• <strong>Debug</strong>ger accesses are qualified through MReq<strong>Debug</strong><br />

• Processor acknowledges debug state entry through MSuspend<br />

• An <strong>OCP</strong> target can be configured to be sensitive to MSuspend line<br />

13 of 62<br />

© 2007 <strong>OCP</strong>-<strong>IP</strong> Association, All Rights Reserved.